# Com Block PCMCIA INTERFACE USER MANUAL

### Scope 1

The COM-13xx ComBlock modules are PC cards which support communication with a host computer through a standard PCMCIA interface. These ComBlock modules can be used as

- (a) ready-to-use application-specific ComBlocks, or

- (b) development platforms with user-developed code.

This manual addresses both use cases. Its scope is limited to the 16-bit PCMCIA interface<sup>1</sup>.

Users of ready-to-use application-specific ComBlocks should read the following sections: "Architecture", "Windows Device Driver Installation" and on "Applications".

Developers should also read the sections on PCMCIA component which implements the PCMCIA interface within the FPGA

The current implementation is subject to the following limitations:

- PCMCIA interface with 16-bit memorymapped and 8-bit I/O-mapped data transfers between ComBlock and host PC

- Windows XP/2000 device driver

The PCMCIA interface sustained (average) throughput was measured using one-way data transfer benchmarks as shown below:

| Throughput test conditions               | Throughput |

|------------------------------------------|------------|

| Memory-mapped data transfers:            | 9.5 Mbps   |

| Host computer: AMD processor 1.2 GHz.    | (either    |

| C runtime application, no hard disk data | direction) |

| transfers. No other application running. |            |

| I/O-mapped data transfers:               | 4.5 Mbps   |

| Host computer: AMD processor 1.2 GHz.    | (either    |

| C runtime application, no hard disk data | direction) |

| transfers. No other application running. |            |

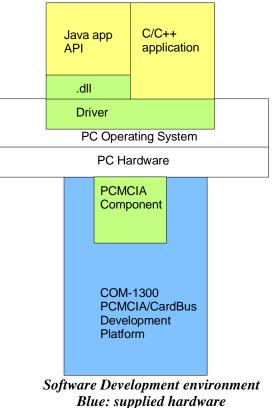

### 2 **Architecture**

The end-to-end communication architecture between a host computer and the ComBlock module as a PCMCIA peripheral is illustrated below:

Green: supplied ready-to-use software

Yellow: application-level code examples.

<sup>1</sup> COM-13xx PC Cards also embody the 32-bit CardBus interface, as addressed in a separate user manual.

MSS • 18221 Flower Hill Way #A • Gaithersburg, Maryland 20879 • U.S.A. Telephone: (240) 631-1111 Facsimile: (240) 631-1676 www.comblock.com © MSS 2000-2005 Issued 9/9/2005

### 2.1 Host side (PC):

In order for a user to setup a PCMCIA connection between the host computer and the ComBlock, the user must first create a Java or C/C++ application.

The Java application calls simple methods described in the Java Application Programming Interface (API) described further in this document.

C/C++ applications can call drivers functions directly as described in the <u>C/C++ Applications</u> described further in this document.

### 2.2 Peripheral side (ComBlock):

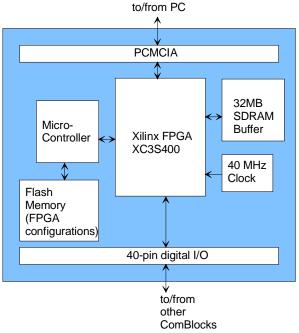

On the peripheral side, the PCMCIA connection is implemented almost entirely within the FPGA as illustrated below:

Development Card Hardware Block Diagram

## 2.3 Supplied Components:

The **PCMCIA software package** provides software to help users and developers create PCMCIA communication between the COM-13xx ComBlock module and a host PC. The software components include the following:

- Windows device driver for XP/2000 (.sys and .inf files)

- Java API

- Java simple application code examples

- C/C++ simple application code examples

• cis\_p, iorw\_p, memory\_p NGC components for integration within the VHDL code

The **PCMCIA software package** is available in the ComBlock CD and can also be downloaded from <u>http://www.comblock.com/download/PCMCIA.zip</u>

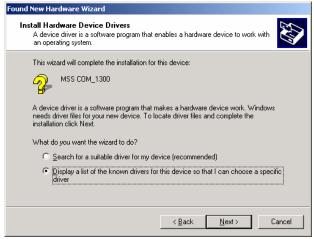

## 3 Windows Device Driver Installation

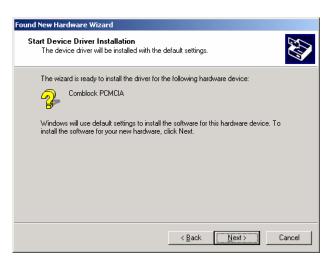

When connecting the COM-1300 PCMCIA interface for the first time, the user is prompted for new hardware installation. Follow the step-by-step instructions shown below each screen shot.

| Found New Hardware Wizard |                                                                                                                        |

|---------------------------|------------------------------------------------------------------------------------------------------------------------|

|                           | Welcome to the Found New<br>Hardware Wizard<br>This wizard helps you install a device driver for a<br>hardware device. |

|                           | < Back Next > Cancel                                                                                                   |

Click on Next.

Check "Display a list of known drivers for the device so that I can choose a specific driver". Click "Next".

| d New Hardware Wizard                                     |       |             |

|-----------------------------------------------------------|-------|-------------|

| ardware Type<br>What type of hardware do you want to inst | tall? | <u>IX</u> I |

| Select a hardware type, and then click Ne                 | xt.   |             |

| Hardware types:                                           |       |             |

| Infrared devices                                          |       |             |

| 🕎 Jungo                                                   |       |             |

| A Modems                                                  |       |             |

| Multi-port serial adapters                                |       |             |

| B Network adapters                                        |       |             |

| NT Apm/Legacy Support                                     |       |             |

| Cher devices                                              |       |             |

| PCMCIA adapters                                           |       |             |

| CMCIA and Flash memory devices                            |       | -           |

Select "Other Devices". Go to the Next screen.

| Found New Hardware Wizard                                                      |                                                                                                           |  |  |

|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|--|

| Select a Device Driver<br>Which driver do you want to install for this device? |                                                                                                           |  |  |

| have a disk that contains the                                                  | model of your hardware device and then click Next. If you<br>driver you want to install, click Have Disk. |  |  |

|                                                                                | lodels:<br>Standard Dual Channel PCI IDE Controller                                                       |  |  |

|                                                                                | Standard DDa/ESDI Hard Disk. Controller                                                                   |  |  |

|                                                                                | Have Disk                                                                                                 |  |  |

|                                                                                | < <u>B</u> ack <u>N</u> ext > Cancel                                                                      |  |  |

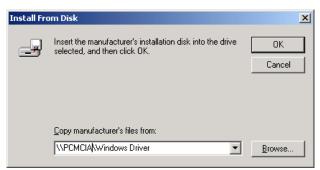

Click on "Have Disk".

Point to the location where the driver files are and click OK.

| Found Ne                   | w Hardware ¥                       | ¥izard                                   |             |                |            |       |              |

|----------------------------|------------------------------------|------------------------------------------|-------------|----------------|------------|-------|--------------|

|                            | t a Device Du<br>/hich driver do y | t <b>iver</b><br>ou want to install f    | for this de | evice?         |            |       |              |

| $\diamond$                 |                                    | ufacturer and mod<br>t contains the driv |             |                |            |       | Next. If you |

| Mo <u>d</u> els:<br>Comblo | ok PCMCIA                          |                                          |             |                |            |       |              |

|                            |                                    |                                          |             |                |            |       | Have Disk    |

|                            |                                    |                                          |             | < <u>B</u> ack | <u>N</u> e | ext > | Cancel       |

Go to the next screen.

Click on Next.

The last window for the New Hardware Wizard should appear, as shown below, for a successfully installed device.

Click on Finish.

At this point, the driver for COM-1300 with PCMCIA interface has been successfully installed and next time the device is plugged in, the system automatically finds appropriate driver. With the driver installed, the user can talk to the device, using the API.

# 4 Applications

### 4.1 Java API

The Java API is documented in ...\Java\API\Pcmcia.html and can be found in the <u>PCMCIA software package</u>.

The applications call simple methods to get a handle, dispose of the handle, read and write.

The DLL, which links the Java application to the drivers, is provided in the <u>PCMCIA software</u> <u>package</u>. It is suggested to copy the pcmciaio.dll file to the Java project directory.

The Java application can transfer data buffers in the range of 0 to 2,048 Bytes to/from the PCMCIA target. When addressing a memory-mapped stream, all transfers are multiple of 2-byte words.

Flow control is implemented by checking the number of bytes actually transmitted at the end of the transaction.

### 4.2 C/C++ Applications

The applications in C++ contains functions to open the device handle, send/receive data and close the handle. Application examples can be found in the <u>PCMCIA</u> software package.

### 5 FPGA/VHDL/DRIVER Development

This section describes how to create a custom application that makes use of the PCMCIA medium on the ComBlock COM-1300 FPGA-based development platforms. This section can be skipped by users of ready-to-use application-specific ComBlock modules.

This section focuses primarily on the peripheral side of the PCMCIA connection.

### 5.1 Host <-> Target Communication Methods

In its basic form the PCMCIA component supports two methods of bi-directional data exchange between host and target:

- One virtual bi-directional channel is I/O mapped and exchanges 8-bit wide data.

- The other virtual bi-directional channel is memory-mapped, exchanges 16-bit words and is optimized for maximum throughput.

The intent is to use the I/O mapped channel to communicate with ComBlock itself, for monitoring and control purposes. The Memory-mapped channel's intended use is for transferring payload data.

The addressing scheme is the same for both I/O and Memory-mapped channels:

- Base address is 0.

- Address range used: 0 12

Beyond the basic software, developers can create multiple I/O and Memory-mapped channels by instantiating multiple VHDL components and specifying non-overlapping address ranges.

### 5.2 Driver Installation

Upon insertion of a COM-1300 (PCMCIA interface), the bus driver will read the CIS (Card Information Services), in particular, the vendor ID and product ID, from the FPGA. Then it searches

through the system registries to find matches with the vendor ID and product ID.

For the first-time installation of COM-1300, the operating system will discover that the vendor ID and product ID are new to the system registries. The user will be directed through a new hardware installation.

The New Hardware Wizard will check the INF file in the specified directory to see if it matches the vendor ID and product ID the host read from the hardware. If matched, the host will find the required drivers (.sys) defined in the .inf file, and copies the drivers to a location described in the .inf file (C:\WINDOWS\system32\drivers by default).

At this point, the .inf and .sys files will be copied by the operating system, and the system registry will be updated to include this device entry. Next time the device is plugged in, the system automatically finds it in the registry and links the device to the appropriate driver.

Note: In case of a conflict of resources with any other device on a Host PC please modify the following section in the comblock pcmcia.inf file:

IOConfig=DF40-DF7F MemConfig=000DD000-000DD800

The memory or io or both address ranges may need to be modified to non-conflicting values.

### 5.3 PCMCIA Component

The PCMCIA implementation on the target side is encapsulated within three NGC components, namely, cis p.ngc, iorw p.ngc and memory p.ngc. This implementation supports two bi-directional channels:

- One virtual channel that is I/O mapped and exchanges 8-bit wide data.

- The other virtual channel that is memorymapped, exchanges 16-bit words

Data is exchanged with the PCMCIA component through a 16Kbit dual-port (elastic) buffer in each direction.

The PCMCIA component works in conjunction with the Windows XP/2000 OS drivers and the Java and C/C++ applications to establish a virtual channel between the COM-1300 and a host

computer. Only one application can connect to the PCMCIA at any given time.

### 5.3.1 Interface

The component is described primarily by its interface definition:

entity PCMCIA is port (

- --// Clocks, reset

- CLK P: in std logic;

- -- Main processing or I/O clock used outside of this component.

- -- All application interface signals are synchronous with CLK\_P

- -- Key assumptions about speed: CLK\_P > 8 MHz

- SYNC\_RESET: in std\_logic;

- -- synchronous reset at power up

- -- Note: Pull-ups are defined in the constraint file.

- PC CARD\_ADDR: in std\_logic\_vector(25 downto 0); -- Address

- PC CARD DATA: inout std logic vector(15 downto 0); -- Data

- PC\_CARD\_WP\_IOIS16\_N: out std\_logic;

- -- WP During memory only interface

- -- IOIS16# During memory or I/O interface

- -- PULL-UP

- PC\_CARD\_RESERVED\_INPACK\_N: out std\_logic;

- -- RESERVED During memory only interface

- -- INPACK# During memory or I/O interface

- PC\_CARD\_BVD2\_SPKR\_N: out std\_logic; -- BVD2

- During memory only interface -- SPKR#

- During memory or I/O interface -- PULL-UP

- PC\_CARD\_BVD1\_STSCHG\_N: out std\_logic;

- -- BVD1 During memory only interface

- -- STSCHG# During memory or I/O interface -- PULL-UP

- PC\_CARD\_RESERVED\_IORD\_N: in std\_logic;

- -- RESERVED During memory only interface

- -- IORD# During memory or I/O interface

- PC\_CARD\_RESERVED\_IOWR\_N: in std\_logic; -- RESERVED During memory only interface

- -- IOWR# During memory or I/O interface

- PC\_CARD\_CE1\_N: in std\_logic;

- -- CE1#

- PC\_CARD\_CE2\_N: in std\_logic;

- -- CE2#

- PC\_CARD\_OE\_N: in std\_logic; - OE#

- PC\_CARD\_WE\_N\_IN: in std\_logic; -- WE#

- PC\_CARD\_REG\_N: in std\_logic;

- -- REG#

- PC\_CARD\_WAIT\_N: out std\_logic;

- -- WAIT#. Atmel uC to drive WAIT# active low while the FPGA is -- being configured.

- PC\_CARD\_READY\_IREQ\_N: out std\_logic;

- -- READY During memory only interface

- -- IREO# During memory or I/O interface

- -- PULL-UP

- PC\_CARD\_RESET\_UC\_MOSI: in std\_logic;

- -- RESET During normal microcontroller operation

- -- UC\_MOSI During microcontroller programming

--// user interfaces

-- Synchronous with CLK\_P clock

<sup>--//</sup> Host bus adapter interface:

<sup>--//</sup> Stream1. 16-bit Memory read/write transactions

| DATA1_OUT: out std_logic_vector(7 downto 0);<br>DATA1_OUT_SAMPLE_CLK: out std_logic;                 | Offs  |

|------------------------------------------------------------------------------------------------------|-------|

| read DATA1_OUT at rising edge of CLK_P when                                                          |       |

| DATA1_OUT_SAMPLE_CLK = '1'                                                                           | То    |

| Note1: the user is responsible for checking                                                          | com   |

| DATA1_OUT_BUFFER_EMPTY before<br>reading.                                                            | Offse |

| Note 2: When the elastic buffer is not empty, DATA1_OUT is                                           | Addı  |

| present at this interface even before requesting it. The request                                     | Offse |

| DATA1_OUT_SAMPLE_CLK_REQ only moves the read pointer                                                 | 0     |

| to the next read location.<br>DATA1_OUT_BUFFER_EMPTY: out std_logic;                                 | 1     |

| DATA1_OUT_SAMPLE_CLK_REQ: in std_logic;                                                              | 2     |

| requests data. If no data is available in the buffer, the                                            |       |

| DATA1_OUT_SAMPLE_CLK will stay low.                                                                  | 3     |

| (flow control)                                                                                       |       |

| DATA1_IN: in std_logic_vector(7 downto 0);                                                           | 4     |

| DATA1_IN_SAMPLE_CLK: in std_logic;                                                                   | 5     |

| read DATA1_IN at rising edge of CLK_P when<br>DATA1_IN_SAMPLE_CLK = '1'                              |       |

| DATA1_IN_SAMPLE_CLK = 1<br>DATA1_IN_SAMPLE_CLK_REQ: out std_logic;                                   | 6     |

| requests data when the input elastic buffer is less than half full.                                  | 7     |

| (flow control)                                                                                       | 8     |

| // user interfaces                                                                                   | 9     |

| // Stream2. 8-bit I/O read/write transactions at I/O address 0                                       | 10    |

| Synchronous with CLK_P clock                                                                         | 11    |

| DATA2_OUT: out std_logic_vector(7 downto 0);                                                         | 12    |

| DATA2_OUT_SAMPLE_CLK: out std_logic;<br>read DATA2_OUT at rising edge of CLK_P when                  | 13    |

| DATA2_OUT_SAMPLE_CLK = '1'                                                                           | 14    |

| Note1: the user is responsible for checking –                                                        | 15    |

| DATA2_OUT_BUFFER_EMPTY before reading.<br>Note 2: When the elastic buffer is not empty, DATA2_OUT is | 16    |

| present at this interface even before requesting it. The request –                                   | 17    |

| DATA2_OUT_SAMPLE_CLK_REQ                                                                             | 18    |

| only moves the read pointer to the next read location.                                               | 19    |

| DATA2_OUT_BUFFER_EMPTY: out std_logic;<br>DATA2_OUT_SAMPLE_CLK_REQ: in std_logic;                    | 20    |

| requests data. If no data is available in the buffer, the                                            | 21    |

| DATA2_OUT_SAMPLE_CLK will stay low.                                                                  | 22    |

| (flow control)                                                                                       | 23    |

| DATA2_IN: in std_logic_vector(7 downto 0);                                                           | 23    |

| DATA2_IN_SAMPLE_CLK: in std_logic;                                                                   | 25    |

| read DATA2_IN at rising edge of CLK_P when<br>DATA2_IN_SAMPLE_CLK = '1'                              | 26    |

| DATA2_IN_SAMPLE_CLK_REQ: out std_logic                                                               | 27    |

| requests data when the input elastic buffer is less than half full.                                  | 28    |

| (flow control)                                                                                       | 33    |

| // Test Points                                                                                       | 34    |

| Test points are under the shield. 6 at the edge connector.                                           | 35    |

| TEST_POINTS: out std_logic_vector(6 downto 1)                                                        | 55    |

| );<br>end entity;                                                                                    |       |

|                                                                                                      | 36    |

|                                                                                                      | 50    |

# 5.3.2 Card Information Services (CIS)

The CIS is a data structure stored in non-volatile memory within the PC Card. It is read by the operating system to determine what kind of PC card is installed, along with its speed, size and the system resources required by the card.

A detailed description of the PCMCIA CIS is provided below. The CIS is defined as a ROM within the VHDL code.

| Offset     | Data           | Description and interpretation                               |

|------------|----------------|--------------------------------------------------------------|

| - 55       | (hex)          | ···· 1                                                       |

| То         |                |                                                              |

| compute    |                |                                                              |

| Offset     |                |                                                              |

| Address =  |                |                                                              |

| Offset * 2 | 01             |                                                              |

| 0          | 01             | Device info tuple                                            |

| 2          | 03<br>D4       | Link to next tuple                                           |

| 2          | D4             | Device Type = Function specific,<br>WPS = OFF, Speed = 100nS |

| 3          | 00             | Memory block size = $1$ unit, $512$                          |

|            |                | bytes                                                        |

| 4          | FF             | End of tuple                                                 |

| 5          | 15             | Level 1 version / product                                    |

|            |                | information                                                  |

| 6          | 10             | Link to next tuple                                           |

| 7          | 04             | PCMCIA Version 2.x                                           |

| 8          | 01             |                                                              |

| 9          | 4D             | M                                                            |

| 10         | 53             | S                                                            |

| 11         | 53             | S                                                            |

| 12         | 00             | End manufacturer name                                        |

| 13         | 43             | С                                                            |

| 14         | 4F             | 0                                                            |

| 15         | 4D             | M                                                            |

| 16         | 20             | Space                                                        |

| 17         | 31             | 1                                                            |

| 18         | 33             | 3                                                            |

| 19         | 30             | 0                                                            |

| 20<br>21   | 30             | 0<br>End version information                                 |

| 21         | 00<br>FF       | Tuple termination byte                                       |

|            |                | Manufacturer ID                                              |

| 23<br>24   | 20<br>04       |                                                              |

| 24         | 04             | Link to next tuple<br>Unregistered PCMCIA ID                 |

| 26         | 00             | Unitegistered FCWCIA ID                                      |

| 20         | 00             | Card number & revision                                       |

| 28         | 01             |                                                              |

| 33         | 1A             | Configuration tuple                                          |

| 34         | 05             | Link to next tuple                                           |

| 35         | 01             | 2-byte (16-bit) configuration                                |

|            | , <sup>*</sup> | register base address, 1 byte                                |

|            |                | configuration register mask                                  |

| 36         | 03             | Index number of last                                         |

|            |                | configuration entry                                          |

| 37         | 00             | Configuration register base                                  |

|            |                | address 0x0200                                               |

| 38         | 02             |                                                              |

| 39         | 01             | Configuration register mask.                                 |

|            |                | Enables configuration registers 0                            |

|            |                | (configuration option register).                             |

| 40         | 1B             | Configuration table entry tuple                              |

| 41         | 16             | Link to next tuple                                           |

| 42         | C1             | Default bit set, interface bit set,                          |

| 42         | 01             | configuration index 1                                        |

| 43         | 01             | Memory or I/O interface                                      |

| Wait not required for memory<br>accesses<br>No write protect.<br>No ready/busy status needed.443DFeature selection field:<br>IRQ, I/O space, memory, timing,<br>Vcc power description structures<br>are present. No Vpp, , misc.<br>description structures.4571Power description structure:<br>- power down supply current<br>required<br>- maximum peak current<br>required (10 ms average)<br>- maximum average current (1<br>second average)<br>- nominal operating supply<br>voltage (+/- 5%)46B53.3V (3 * 1V + 0.30V extension)<br>47471E0.30V48666 * 100mA maximum average<br>current5054Power down supply current 5 *<br>1mA51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:<br>5.0 (mantissa) x 100 µs |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No write protect.<br>No ready/busy status needed.443DFeature selection field:<br>IRQ, I/O space, memory, timing,<br>Vcc power description structures<br>are present. No Vpp, , misc.<br>description structures.4571Power description structures:<br>- power down supply current<br>required<br>- maximum peak current<br>required (10 ms average)<br>- maximum average current (1<br>second average)<br>- nominal operating supply<br>voltage (+/- 5%)46B53.3V (3 * 1V + 0.30V extension)471E0.30V48666 * 100mA maximum peak<br>current5054Power down supply current 5 *<br>1mA51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                       |

| A43DNo ready/busy status needed.443DFeature selection field:<br>IRQ, I/O space, memory, timing,<br>Vcc power description structures<br>are present. No Vpp, , misc.<br>description structures.4571Power description structure:<br>- power down supply current<br>required<br>- maximum peak current<br>required (10 ms average)<br>- maximum average current (1<br>second average)<br>- nominal operating supply<br>voltage (+/- 5%)46B53.3V (3 * 1V + 0.30V extension)<br>47471E0.30V48666 * 100mA maximum average<br>current5054Power down supply current 5 *<br>1mA51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined, a<br>Ready/Busy scale is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                              |

| 443DFeature selection field:<br>IRQ, I/O space, memory, timing,<br>Vcc power description structures<br>are present. No Vpp, , misc.<br>description structures.4571Power description structure:<br>- power down supply current<br>required<br>- maximum peak current<br>required (10 ms average)<br>- maximum average current (1<br>second average)<br>- nominal operating supply<br>voltage (+/- 5%)46B53.3V (3 * 1V + 0.30V extension)<br>47471E0.30V48666 * 100mA maximum average<br>current49768 * 100mA maximum peak<br>current5054Power down supply current 5 *<br>1mA51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined, a<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                             |

| IRQ, I/O space, memory, timing,<br>Vcc power description structures<br>are present. No Vpp, , misc.<br>description structures.4571Power description structure:<br>- power down supply current<br>required<br>- maximum peak current<br>required (10 ms average)<br>- maximum average current (1<br>second average)<br>- nominal operating supply<br>voltage (+/- 5%)46B53.3V (3 * 1V + 0.30V extension)471E0.30V48666 * 100mA maximum average<br>current49768 * 100mA maximum peak<br>current5054Power down supply current 5 *<br>1mA51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined, a<br>no reserved time scale is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                |

| Vcc power description structures<br>are present. No Vpp, , misc.<br>description structures.4571Power description structure:<br>- power down supply current<br>required<br>- maximum peak current<br>required (10 ms average)<br>- maximum average current (1<br>second average)<br>- nominal operating supply<br>voltage (+/- 5%)46B53.3V (3 * 1V + 0.30V extension)471E0.30V48666 * 100mA maximum average<br>current49768 * 100mA maximum peak<br>current5054Power down supply current 5 *<br>1mA51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined,<br>no reserved time scale is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                     |

| are present. No Vpp, , misc.<br>description structures.4571Power description structure:<br>- power down supply current<br>required<br>- maximum peak current<br>required (10 ms average)<br>- maximum average current (1<br>second average)<br>- nominal operating supply<br>voltage (+/- 5%)46B53.3V (3 * 1V + 0.30V extension)<br>47471E0.30V48666 * 100mA maximum average<br>current49768 * 100mA maximum peak<br>current5054Power down supply current 5 *<br>1mA51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined, a<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                    |

| 4571Power description structures.4571Power description structure:<br>- power down supply current<br>required<br>- maximum peak current<br>required (10 ms average)<br>- maximum average current (1<br>second average)<br>- nominal operating supply<br>voltage (+/- 5%)46B53.3V (3 * 1V + 0.30V extension)<br>4746B53.3V (3 * 1V + 0.30V extension)471E0.30V48666 * 100mA maximum average<br>current49768 * 100mA maximum peak<br>current5054Power down supply current 5 *<br>1mA51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined, a<br>no reserved time scale is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                    |

| 4571Power description structure:<br>- power down supply current<br>required<br>- maximum peak current<br>required (10 ms average)<br>- maximum average current (1<br>second average)<br>- nominal operating supply<br>voltage (+/- 5%)46B53.3V (3 * 1V + 0.30V extension)471E0.30V48666 * 100mA maximum average<br>current49768 * 100mA maximum peak<br>current5054Power down supply current 5 *<br>1mA51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                      |

| -power down supply current<br>required-maximum peak current<br>required (10 ms average)-maximum average current (1<br>second average)-nominal operating supply<br>voltage (+/- 5%)46B53.3V (3 * 1V + 0.30V extension)471E0.30V48666 * 100mA maximum average<br>current49768 * 100mA maximum peak<br>current5054Power down supply current 5 *<br>1mA51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                          |

| required-maximum peak current<br>required (10 ms average)<br>-<br>maximum average current (1<br>second average)<br>-<br>nominal operating supply<br>voltage (+/- 5%)46B53.3V (3 * 1V + 0.30V extension)471E0.30V48666 * 100mA maximum average<br>current49768 * 100mA maximum peak<br>current5054Power down supply current 5 *<br>1mA51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                                        |

| -maximum peak current<br>required (10 ms average)<br>- maximum average current (1<br>second average)<br>- nominal operating supply<br>voltage (+/- 5%)46B53.3V (3 * 1V + 0.30V extension)471E0.30V48666 * 100mA maximum average<br>current49768 * 100mA maximum peak<br>current5054Power down supply current 5 *<br>1mA51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                                                      |

| required (10 ms average)<br>- maximum average current (1<br>second average)<br>- nominal operating supply<br>voltage (+/- 5%)46B53.3V (3 * 1V + 0.30V extension)471E0.30V48666 * 100mA maximum average<br>current49768 * 100mA maximum peak<br>current5054Power down supply current 5 *<br>1mA51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| -maximum average current (1<br>second average)<br>- nominal operating supply<br>voltage (+/- 5%)46B53.3V (3 * 1V + 0.30V extension)471E0.30V48666 * 100mA maximum average<br>current49768 * 100mA maximum peak<br>current5054Power down supply current 5 *<br>1mA51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| second average)<br>- nominal operating supply<br>voltage (+/- 5%)46B53.3V (3 * 1V + 0.30V extension)471E0.30V48666 * 100mA maximum average<br>current49768 * 100mA maximum peak<br>current5054Power down supply current 5 *<br>1mA51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| -nominal operating supply<br>voltage (+/- 5%)46B5 $3.3V (3 * 1V + 0.30V extension)$ 471E $0.30V$ 4866 $6 * 100$ mA maximum average<br>current4976 $8 * 100$ mA maximum peak<br>current5054Power down supply current 5 *<br>1mA51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| voltage (+/- 5%)46B53.3V (3 * 1V + 0.30V extension)471E0.30V4866666 * 100mA maximum average<br>current49768 * 100mA maximum peak<br>current50549 Power down supply current 5 *<br>1mA51E051E072Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined.527272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 46B5 $3.3V (3 * 1V + 0.30V extension)$ 471E $0.30V$ 4866 $6 * 100$ mA maximum average<br>current4976 $8 * 100$ mA maximum peak<br>current5054Power down supply current $5 *$<br>1mA51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined.5272Wait signal timing descriptor:<br>$7.0 (mantissa) x 100 ns$<br>(exponent) x 1 scaling factor =<br>$700 ns.$ 535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 471E0.30V48666 * 100mA maximum average<br>current49768 * 100mA maximum peak<br>current5054Power down supply current 5 *<br>1mA51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 471E0.30V48666 * 100mA maximum average<br>current49768 * 100mA maximum peak<br>current5054Power down supply current 5 *<br>1mA51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 48666 * 100mA maximum average<br>current49768 * 100mA maximum peak<br>current5054Power down supply current 5 *<br>1mA51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 49768 * 100mA maximum peak<br>current5054Power down supply current 5 *<br>1mA51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined,<br>no reserved time scale is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 49768 * 100mA maximum peak<br>current5054Power down supply current 5 *<br>1mA51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined, a<br>no reserved time scale is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| current5054Power down supply current 5 *<br>1mA51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined, a<br>no reserved time scale is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5054Power down supply current 5 *<br>1mA51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined, a<br>no reserved time scale is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1mA51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined, a<br>no reserved time scale is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 51E0Timing description structure. A<br>Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined, a<br>no reserved time scale is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Wait scale of 1 is defined, a<br>Ready/Busy scale of 1 is defined,<br>no reserved time scale is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Ready/Busy scale of 1 is defined,<br>no reserved time scale is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| no reserved time scale is defined.5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5272Wait signal timing descriptor:<br>7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.0 (mantissa) x 100 ns<br>(exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| (exponent) x 1 scaling factor =<br>700 ns.535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 535DReady/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 53 5D Ready/Busy timing descriptor:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.0 (mantissa) x 100 µs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| (exponent) x 1 (scaling factor) =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 500 μs max READY delay.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 54A66 I/O address lines, use data bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| $D_7$ - $D_0$ to access the registers (8-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| bit wide), specify an I/O range.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 55 60 Length size descriptor: 1 address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| (=2  bytes) and 1 length $(=1)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| byte). Only one address range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| descriptor present.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 56 00 Start address = $0x00000$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 57 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $58 \qquad 3F \qquad \text{Length of address block} = 0x40$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| (64 bytes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5950Interrupt request description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |