## COM-1019 DIRECT-SEQUENCE SPREAD-SPECTRUM MODULATOR 20 Mchip/s

## **Key Features**

- Direct sequence spread-spectrum (DS-SS) modulator.

- Programmable chip rates up to 20 Mchip/s.

- Spreading codes:

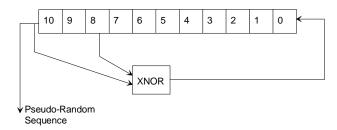

- O Gold sequences (up to  $2^{23}$ -1 chips).

- o Maximal length sequences, (max length  $2^{23}$ -1 chips).

- o Barker codes (length 11, 13).

- o GPS C/A codes.

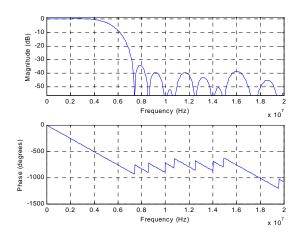

- code modulation: BPSK/QPSK/OQPSK with output spectral shaping filter: raised cosine square root filter with 20%, 25%, 35% or 40% rolloff. Filter can be bypassed.

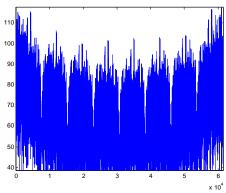

- Internal generation of pseudo-random bit stream and unmodulated carrier for test purposes.

- Built-in channel impairments generation:

- additive white Gaussian noise

- frequency offset (Doppler)

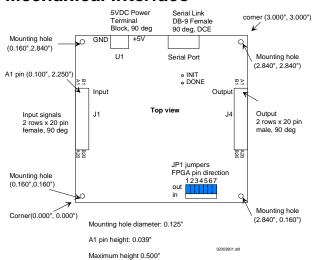

- Connectorized 3"x 3" module for ease of prototyping. Standard 40 pin 2mm dual row connectors (left, right). Single 5V supply with reverse voltage and overvoltage protection. Interfaces with 3.3V LVTTL logic.

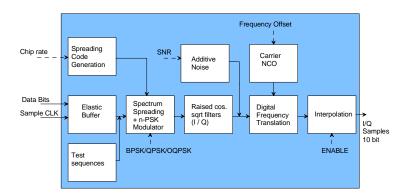

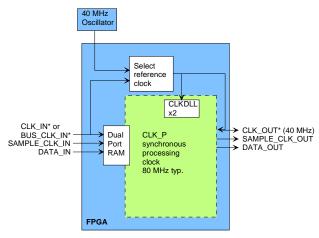

#### **Block Diagram**

For the latest data sheet, please refer to the **ComBlock** web site: <a href="https://www.comblock.com/download/com1019.pdf">www.comblock.com/download/com1019.pdf</a>. These specifications are subject to change without notice.

For an up-to-date list of **ComBlock** modules, please refer to <a href="https://www.comblock.com/product\_list.htm">www.comblock.com/product\_list.htm</a>.

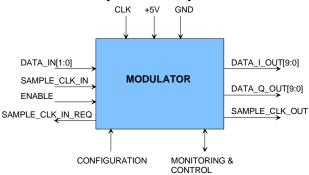

#### Electrical Interface

## **Modulator Inputs / Outputs**

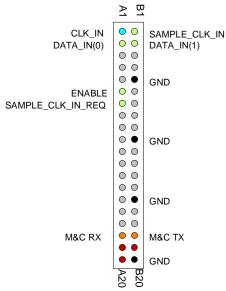

Two basic types of input connections are available for user selection:

- direct connection between data source and modulator.

- single data source to multiple modulators over a shared bus.

| Input Module      | Definition                      |

|-------------------|---------------------------------|

| Interface         |                                 |

| Direct connection |                                 |

| between two       |                                 |

| ComBlocks,        |                                 |

| REG19(4) = '0'    |                                 |

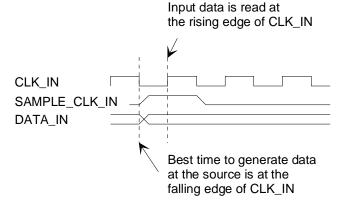

| CLK_IN            | Synchronous clock reference     |

|                   | for the input interface. All    |

|                   | input signals (DATA IN,         |

|                   | SAMPLE_CLK_IN,                  |

|                   | ENABLE) are read at the         |

|                   | rising edge of CLK IN.          |

|                   | Recommended maximum             |

|                   | frequency: 40 MHz.              |

|                   | LVTTL 0 – 3.3V                  |

| DATA_IN[1:0]      | Input data stream.              |

|                   |                                 |

|                   | In 1-bit serial mode, use       |

|                   | DATA_IN[0] only.                |

|                   |                                 |

|                   | In 2-bit parallel mode,         |

|                   | DATA_IN[0] is the I data bit    |

|                   | DATA_IN[1] is the Q data        |

|                   | bit                             |

|                   | The Q data bit is ignored in    |

|                   | BPSK mode.                      |

|                   | LVTTL 0 – 3.3V                  |

| SAMPLE_CLK_IN     | Input sample clock. One         |

|                   | CLK_IN-wide pulse. Read         |

|                   | the input signals at the rising |

|                   | edge of CLK_IN when             |

|                   | $SAMPLE\_CLK\_IN = '1'.$        |

|                   | LVTTL 0 – 3.3V                  |

| ENABLE            | Modulator enable input.         |

|                   | Internally pulled high.         |

|                   | Qualifies the SAMPLE_CLK_IN. Used for burst-mode transmission. In continuous mode, keep at '1'. LVTTL 0 – 3.3V |

|-------------------|----------------------------------------------------------------------------------------------------------------|

| SAMPLE_CLK_IN_REQ | Output. Requests a sample from the module upstream. For flow-control purposes.                                 |

| T 437 11        | D 6. 11.                                               |  |

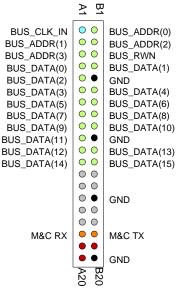

|-----------------|--------------------------------------------------------|--|

| Input Module    | Definition                                             |  |

| Interface       |                                                        |  |

| Bus connection, |                                                        |  |

| REG19(4) = '1'  |                                                        |  |

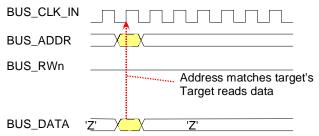

| BUS_CLK_IN      | 40 MHz input reference clock for                       |  |

|                 | use on the synchronous bus.                            |  |

| BUS_ADDR[3:0]   | Bus address. Input (since this                         |  |

|                 | module is a bus slave). Designates                     |  |

|                 | which slave module is targeted for                     |  |

|                 | this read or write transaction.                        |  |

|                 | All 1's indicates that the write data                  |  |

|                 | is to be broadcasted to all receiving                  |  |

|                 | slave modules.                                         |  |

|                 | Read at the rising edge of                             |  |

|                 | BUS CLK IN                                             |  |

| BUS RWN         | Read/Write#. Input (since this                         |  |

|                 | module is a bus slave).                                |  |

|                 | Indicates whether a read (1) or write                  |  |

|                 | (0) transaction is conducted. Read                     |  |

|                 | at the rising edge of BUS CLK IN.                      |  |

|                 | Read and Write refer to the bus                        |  |

|                 | master's perspective.                                  |  |

| BUS DATA[15:0]  | Bi-directional data bus.                               |  |

|                 | Input when BUS RWN='0'.                                |  |

|                 | Output when BUS RWN='1'.                               |  |

|                 | Read data latency is 2 clock periods                   |  |

|                 | after the read command.                                |  |

|                 | Functional definition during write:                    |  |

|                 | • bit 0 SAMPLE CLK IN. '1'                             |  |

|                 | when DATA IN is available                              |  |

|                 | • bit 1 DATA IN data stream to                         |  |

|                 | modulator.                                             |  |

|                 | <ul> <li>bits(15:2) undefined</li> </ul>               |  |

|                 | Functional definition during read:                     |  |

|                 | I — — — — — — — — — — — — — — — — — — —                |  |

|                 | bit 0 SAMPLE_CLK_IN_REQ  requests data from the source |  |

|                 | requests data from the source.                         |  |

|                 | Used for flow control.                                 |  |

|                 | • bits(15:1) undefined                                 |  |

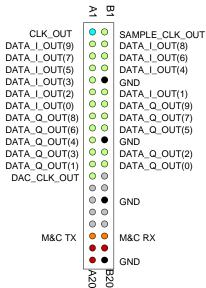

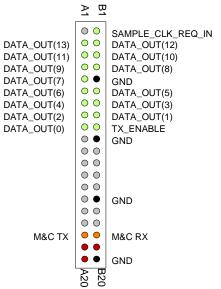

Two basic types of output connections are available for user selection:

- connection to dual 10-bit DACs, parallel I and Q samples, output sampling clock.

- connection to dual 14-bit DACs, multiplexed I and Q samples, input sampling clock.

| Output Module         | Definition                                                               |  |

|-----------------------|--------------------------------------------------------------------------|--|

| Interface.            |                                                                          |  |

| Parallel 10-bit I & Q |                                                                          |  |

| samples.              |                                                                          |  |

| REG19(0) ='0'         |                                                                          |  |

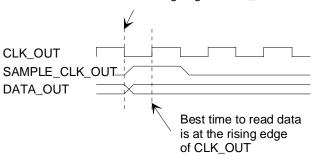

| CLK_OUT               | 40 MHz synchronous clock                                                 |  |

|                       | reference for the output interface.                                      |  |

|                       | The output signals                                                       |  |

|                       | DATA_I_OUT, DATA_Q_OUT,                                                  |  |

|                       | SAMPLE_CLK_OUT change                                                    |  |

|                       | immediately after the rising edge                                        |  |

|                       | of CLK_OUT.                                                              |  |

|                       | Recommended maximum                                                      |  |

|                       | frequency: 40 MHz.                                                       |  |

| DATA_I_OUT[9:0]       | Modulated output signal, real                                            |  |

|                       | axis. 10-bit precision.                                                  |  |

|                       | Format: 2's complement or unsigned, selected by                          |  |

|                       |                                                                          |  |

|                       | configuration bit 1.                                                     |  |

| DATA_Q_OUT[9:0]       | Modulated output signal,                                                 |  |

|                       | imaginary axis. 10-bit precision.                                        |  |

| GALLERY E. GLYL GAVE  | Same format as DATA_I_OUT.                                               |  |

| SAMPLE_CLK_OUT        | Output signal sampling clock.                                            |  |

|                       | Read the output signal at the                                            |  |

|                       | rising edge of CLK_OUT when                                              |  |

|                       | SAMPLE_CLK_OUT = '1'.                                                    |  |

|                       | Sampling rate is either                                                  |  |

|                       | 4 x symbol rate or fclk<br>(interpolation off/on<br>configuration bit 7) |  |

|                       |                                                                          |  |

|                       |                                                                          |  |

|                       |                                                                          |  |

|                       | high when output samples are transmitted in successive                   |  |

|                       | CLK OUT periods.                                                         |  |

| DAC CLK OUT           | Output sampling clock for Digital                                        |  |

| DRC_CER_OUT           | to Analog Converters.                                                    |  |

|                       | DAC reads the output sample at                                           |  |

|                       | the rising edge.                                                         |  |

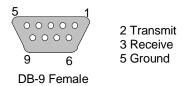

| Serial Monitoring     | DB9 connector.                                                           |  |

| & Control             | 115 Kbaud/s. 8-bit, no parity, one                                       |  |

|                       | stop bit. No flow control.                                               |  |

| Power Interface       | 4.75 – 5.25VDC. Terminal block.                                          |  |

|                       | Power consumption is                                                     |  |

|                       | approximately proportional to the                                        |  |

|                       | sampling frequency f <sub>sample clk</sub> .                             |  |

|                       | The maximum power                                                        |  |

|                       | consumption at 80 MHz is                                                 |  |

|                       | 600mA.                                                                   |  |

Important: I/O signals are 0-3.3V LVTTL. Inputs are NOT 5V tolerant!

## Configuration

An entire ComBlock assembly comprising several ComBlock modules can be monitored and controlled centrally over a single connection with a host computer. Connection types include built-in types:

- Asynchronous serial (DB9)

- or connections via adjacent ComBlocks:

- **USB**

- TCP-IP/LAN,

- Asynchronous serial (DB9)

- PC Card (CardBus, PCMCIA).

The module configuration is stored in non-volatile memory.

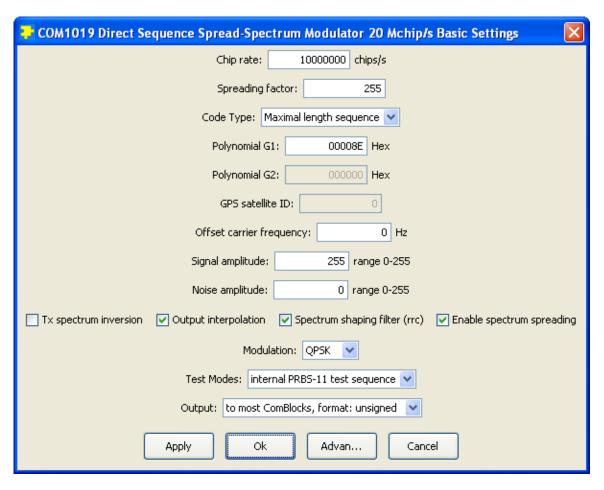

#### **Configuration (Basic)**

The easiest way to configure the COM-1019 is to use the ComBlock Control Center software supplied with the module on CD. In the ComBlock Control Center window detect the ComBlock module(s) by clicking the Detect button, next click to highlight the COM-1019 module to be configured, next click the Settings button to display the Settings window shown below.

### **Configuration (Advanced)**

Alternatively, users can access the full set of configuration features by specifying 8-bit control registers as listed below. These control registers can be set manually through the ComBlock Control Center "Advanced" configuration or by software using the ComBlock API (see <a href="https://www.comblock.com/download/M&C">www.comblock.com/download/M&C</a> reference.pdf)

All control registers are read/write.

Definitions for the <u>Control registers</u> are provided below.

#### **Control Registers**

The module configuration parameters are stored in volatile (SRT command) or non-volatile memory (SRG command). All control registers are read/write.

This module operates at an internal processing clock rate  $\mathbf{f}_{clk}$  of 80 MHz.

Most processing is done at the sampling rate /  $\mathbf{f}_{\text{sample\_clk}} = 4 * \text{chip rate}.$

In the definition below, a few control register bits may be undefined to maintain backward compatibility with previous versions. They can be ignored by the user when using the latest firmware release.

| Parameters | Configuration                                           |

|------------|---------------------------------------------------------|

| Chip rate  | 24-bit signed integer (2's complement)                  |

|            | expressed as                                            |

|            | fchip rate * $2^{24} / \mathbf{f_{clk}}$ .              |

|            | The maximum chip rate is $\mathbf{f_{clk}}/4$ (20       |

|            | Mchips/s). However, in practice it is                   |

|            | recommended to limit the maximum                        |

|            | chip rate to $0.99*(\mathbf{f_{clk}}/4)$ to account for |

|            | possible clock drifts between modulator                 |

|            | and demodulator.                                        |

|            | REG0 = bits 7-0                                         |

|            | REG1 = bits 15 - 8                                      |

|            | REG2 = bits 23 - 16                                     |

| Spreading             | Spreading code period                                                                |

|-----------------------|--------------------------------------------------------------------------------------|

| factor                | Range: $3 - 2^{23} - 1$                                                              |

| (Processing           | <ul> <li>When using Gold codes or maximal</li> </ul>                                 |

| gain)                 | length sequences, it is important that                                               |

|                       | this field be consistent with the G1                                                 |

|                       | and G2 generator polynomials                                                         |

|                       | below. Length is always in the form                                                  |

|                       | 2 <sup>n</sup> -1, where n is an integer.                                            |

|                       | <ul> <li>When using Barker codes, the</li> </ul>                                     |

|                       | spreading factor must be either 11 (0x0B) or 13 (0x0D).                              |

|                       | <ul> <li>Truncated codes can be generated by</li> </ul>                              |

|                       | selecting a spreading factor other                                                   |

|                       | than the code length.                                                                |

|                       | Please note that, even though generating                                             |

|                       | very long codes is possible, their use                                               |

|                       | may be impractible because of                                                        |

|                       | unacceptably long acquisition time at the                                            |

|                       | demodulator. Recommended spreading                                                   |

|                       | factor: 3 to 2047.                                                                   |

|                       | REG3 bits 7-0 (LSB)                                                                  |

|                       | REG4 bits 7-0                                                                        |

|                       | REG5 bits 7-0 (MSB)                                                                  |

| Code                  | 001 = Gold code                                                                      |

| selection             | 010 = Maximal length sequence                                                        |

|                       | 011 = Barker code                                                                    |

|                       | 100 = GPS C/A code                                                                   |

|                       | PEG(1): 0.0                                                                          |

| 0.11                  | REG6 bits 2-0                                                                        |

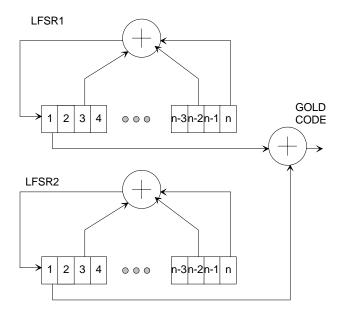

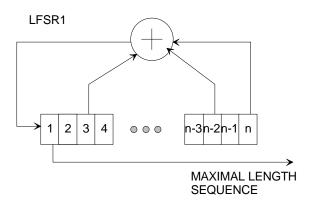

| Gold                  | 24-bit. Describes the taps in the linear                                             |

| sequence /<br>Maximal | feedback shift register 1:                                                           |

| Length                | Bit 0 is the leftmost tap (2 <sup>0</sup> in the                                     |

| Sequence              | polynomial). The largest non-zero bit is<br>the polynomial order n. n determines the |

| generator             | code period 2 <sup>n</sup> –1.                                                       |

| polynomial            | Example:                                                                             |

| G1                    | $G1 = 1 + x + x^4 + x^5 + x^6$ is represented                                        |

|                       | as 0x000039                                                                          |

|                       | This field is used only if Gold code or                                              |

|                       | Maximal length sequences are selected.                                               |

|                       | REG7 = bits $7 - 0$                                                                  |

|                       | REG8 = bits 15 - 8                                                                   |

|                       | REG9 = bits 23 - 16                                                                  |

| Gold code             | 24-bit. Describes the taps in the linear                                             |

| generator             | feedback shift register 2: Same format as                                            |

| polynomial            | G1 above.                                                                            |

| G2                    | This field is used only if Gold codes are                                            |

|                       | selected.                                                                            |

|                       | REG10 = bits 7 – 0                                                                   |

|                       | REG11 = bits 15 – 8                                                                  |

| GPS satellite         | REG12 = bits 23 - 16                                                                 |

| GPS satellite         | GPS signals from different satellites are                                            |

| π                     | designated by a PRN signal number in                                                 |

|                       | the range $1 - 37$ .                                                                 |

|                       | This field is used only if GPS C/A codes are selected.                               |

|                       | REG10 = bits $5 - 0$                                                                 |

|                       | 122010 01600 0                                                                       |

5

| Offset carrier                  | 24-bit signed integer (2's complement)                                 |  |

|---------------------------------|------------------------------------------------------------------------|--|

| frequency <b>f</b> <sub>c</sub> | expressed as                                                           |  |

|                                 | $f_c * 2^{24} / f_{\text{sample\_clk}}$ .                              |  |

|                                 | REG13 = bits 7 - 0                                                     |  |

|                                 | REG14 = bits 15 - 8                                                    |  |

| G: 1                            | REG15 = bits 23 - 16                                                   |  |

| Signal gain                     | Signal level.                                                          |  |

|                                 | 8-bit unsigned integer.                                                |  |

|                                 | Maximum level 255, Minimum level 0.<br>When the maximal level (255) is |  |

|                                 | selected, the peak-to-peak dynamic range                               |  |

|                                 | is +/- 371 out of a +/-512 (10-bit) range                              |  |

|                                 | and the standard deviation is 249.                                     |  |

|                                 | REG16 = bits 7-0                                                       |  |

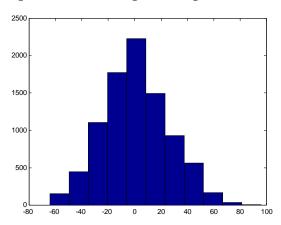

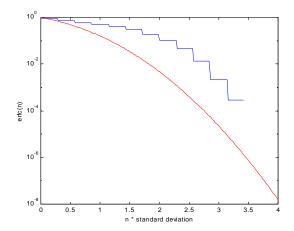

| Noise gain                      | Additive white Gaussian noise level.                                   |  |

|                                 | 8-bit unsigned integer.                                                |  |

|                                 | Maximum level 255, Minimum level 0.                                    |  |

|                                 | The noise samples standard deviation is                                |  |

|                                 | 111 for a maximum noise gain setting of                                |  |

|                                 | 255. (The noise bandwidth is +/- 2*                                    |  |

|                                 | symbol rate). REG17 = bits 7-0                                         |  |

| Internal /                      | This control bit selects the reference                                 |  |

| External                        | clock source.                                                          |  |

| reference                       | ■ Reference clock selection must be                                    |  |

| clock                           | 'internal' when this module is the first in                            |  |

| selection                       | the transmission chain and when using                                  |  |

|                                 | the internally generated test sequences                                |  |

|                                 | (see Test mode below).                                                 |  |

|                                 | ■ Reference clock selection must also be                               |  |

|                                 | 'internal' when user-supplied input data                               |  |

|                                 | is synchronous with a CLK_IN clock                                     |  |

|                                 | frequency other than the recommended 40 MHz.                           |  |

|                                 | ■ External reference clock should be                                   |  |

|                                 | used for applications whereby multiple                                 |  |

|                                 | modulators must be exactly synchronized                                |  |

|                                 | (for example in the case of signal                                     |  |

|                                 | diversity combining applications).                                     |  |

|                                 | 0 = internal clock                                                     |  |

|                                 | 1 = external clock                                                     |  |

| Output comple                   | REG18 bit 0                                                            |  |

| Output sample format            | 0 = 2's complement                                                     |  |

|                                 | 1 = unsigned<br>REG18 bit 1                                            |  |

| Modulation                      | 00 = BPSK                                                              |  |

|                                 | 01 = OPSK                                                              |  |

|                                 | 10 = OQPSK                                                             |  |

|                                 | With BPSK, one data bit is transmitted                                 |  |

|                                 | every code period.                                                     |  |

|                                 | With QPSK, two data bits (one symbol)                                  |  |

|                                 | are transmitted every code period.                                     |  |

|                                 | The code spectrum-spreading occurs                                     |  |

|                                 | after QPSK modulation of the data                                      |  |

|                                 | symbols. REG18 bits 3 – 2                                              |  |

|                                 | NEO 10 0113 3 - 2                                                      |  |

| Test mode    00 = disabled   01 = internal generation of 2047-bit periodic pseudo-random bit sequence as modulator input. (overrides external input bit stream).   10 = unmodulated carrier. (overrides external input bit stream)   REG18 bits 5 - 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| periodic pseudo-random bit sequence as modulator input. (overrides external input bit stream).  10 = unmodulated carrier. (overrides external input bit stream)  REG18 bits 5 - 4  Spectrum inversion  Invert Q bit. 0 = off 1 = on REG18 bit 6  Interpolation  Interpolation to maximum clock rate. 0 = off 1 = on REG18 bit 7  Output data flow  Output data is pushed to the next module (for example to COM-2001, or COM-1011/18) 1 = output data is pulled by next module (for example by the COM-4004) REG19 bit 0  Input format  Ouput spectrum spaping filter enabled 1 = canabled REG19 bit 1  Couput spectrum shaping filter on disabled 1 = enabled REG19 bit 2  Spreading  Enable/Disables raised cosine square root output spectrum shaping filter. 0 = disabled 1 = enabled REG19 bit 3  Input bus enabled REG19 bit 4  Bus address  Unique 4-bit address identifying this module on the input bus (if the input bus is enabled in REG19 bit 4). Ignore otherwise. This module acts as bus slave: it performs the read/write transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| modulator input. (overrides external input bit stream).  10 = unmodulated carrier. (overrides external input bit stream).  REG18 bits 5 - 4  Spectrum inversion  1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| modulator input. (overrides external input bit stream).  10 = unmodulated carrier. (overrides external input bit stream).  REG18 bits 5 - 4  Spectrum inversion  1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| input bit stream).  10 = unmodulated carrier. (overrides external input bit stream)  REG18 bits 5 - 4  Spectrum inversion  0 = off 1 = on REG18 bit 6  Interpolation  Interpolation to maximum clock rate. 0 = off 1 = on REG18 bit 7  Output data flow  0 = output data is pushed to the next module (for example to COM-2001, or COM-1011/18) 1 = output data is pulled by next module (for example by the COM-4004)  REG19 bit 0  Input format  1 = 2-bit parallel (see also input bus enable bit below).  REG19 bit 1  Ouput spectrum shaping filter enabled 1 = enabled REG19 bit 2  Spreading  Controls whether the input connection is point-to-point or point-to-multipoint over a data bus (via a COM-9004 demultiplexing connector for example). The J1 input connector pinout is affected by this control bit. 0 = direct connection. Point to point. 1 = input data bus enabled.  REG19 bit 4  Bus address  Input bus enabled in REG19 bit 4). Ignore otherwise. This module acts as bus slave: it performs the read/write transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Inversion   Invert Q bit.   Interpolation   In |

| external input bit stream) REG18 bits 5 – 4  Spectrum inversion  Invert Q bit. 0 = off 1 = on REG18 bit 6  Interpolation  Interpolation to maximum clock rate. 0 = off 1 = on REG18 bit 7  Output data flow  Output data flow  Output data flow  Input format  Input format  Output data 1 = output data is pushed to the next module (for example to COM-2001, or COM-1011/18) 1 = output data is pulled by next module (for example by the COM-4004) REG19 bit 0  Input format  Output Spectrum Shaping filter enabled  REG19 bit 1  Couput Spectrum Shaping filter enabled  REG19 bit 2  Spreading  Enables/Disables raised cosine square root output spectrum shaping filter. 0 = disabled 1 = enabled REG19 bit 2  Spreading  Input bus enabled  REG19 bit 3  Controls whether the input connection is point-to-point or point-to-multipoint over a data bus (via a COM-9004 demultiplexing connector for example). The J1 input connector pinout is affected by this control bit. 0 = direct connection. Point to point. 1 = input data bus enabled. REG19 bit 4  Bus address  Bus address  Unique 4-bit address identifying this module on the input bus (if the input bus is enabled in REG19 bit 4). Ignore otherwise. This module acts as bus slave: it performs the read/write transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| REG18 bits 5 - 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Inversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| inversion    O = off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Interpolation  Interpolation  Interpolation to maximum clock rate.  0 = off 1 = on REG18 bit 7  Output data flow  0 = output data is pushed to the next module (for example to COM-2001, or COM-1011/18) 1 = output data is pulled by next module (for example by the COM-4004) REG19 bit 0  Input format  0 = 1-bit serial 1 = 2-bit parallel (see also input bus enable bit below). REG19 bit 1  Ouput spectrum shaping filter enabled  Enables/Disables raised cosine square root output spectrum shaping filter. 0 = disabled 1 = enabled REG19 bit 2  Spreading  Input bus enabled  REG19 bit 3  Input bus enabled  Controls whether the input connection is point-to-point or point-to-multipoint over a data bus (via a COM-9004 demultiplexing connector for example). The J1 input connector pinout is affected by this control bit. 0 = direct connection. Point to point. 1 = input data bus enabled. REG19 bit 4  Bus address  Unique 4-bit address identifying this module on the input bus (if the input bus is enabled in REG19 bit 4). Ignore otherwise. This module acts as bus slave: it performs the read/write transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| REG18 bit 6  Interpolation  Interpolation to maximum clock rate.  0 = off 1 = on REG18 bit 7  Output data flow  0 = output data is pushed to the next module (for example to COM-2001, or COM-1011/18) 1 = output data is pulled by next module (for example by the COM-4004) REG19 bit 0  Input format  0 = 1-bit serial 1 = 2-bit parallel (see also input bus enable bit below). REG19 bit 1  Ouput spectrum shaping filter enabled  1 = enables/Disables raised cosine square root output spectrum shaping filter. 0 = disabled 1 = enabled REG19 bit 2  Spreading  Enable/Disable spectrum spreading. 0 = disabled 1 = enabled REG19 bit 3  Input bus enabled  Controls whether the input connection is point-to-point or point-to-multipoint over a data bus (via a COM-9004 demultiplexing connector for example). The J1 input connector pinout is affected by this control bit. 0 = direct connection. Point to point. 1 = input data bus enabled. REG19 bit 4  Bus address  Unique 4-bit address identifying this module on the input bus (if the input bus is enabled in REG19 bit 4). Ignore otherwise. This module acts as bus slave: it performs the read/write transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Interpolation  Interpolation to maximum clock rate.  0 = off 1 = on REG18 bit 7  Output data flow  0 = output data is pushed to the next module (for example to COM-2001, or COM-1011/18) 1 = output data is pulled by next module (for example by the COM-4004) REG19 bit 0  Input format  0 = 1-bit serial 1 = 2-bit parallel (see also input bus enable bit below). REG19 bit 1  Ouput spectrum shaping filter enabled  1 = enables/Disables raised cosine square root output spectrum shaping filter. 0 = disabled 1 = enabled REG19 bit 2  Spreading  Enable/Disable spectrum spreading. 0 = disabled 1 = enabled REG19 bit 3  Input bus enabled  Controls whether the input connection is point-to-point or point-to-multipoint over a data bus (via a COM-9004 demultiplexing connector for example). The J1 input connector pinout is affected by this control bit. 0 = direct connection. Point to point. 1 = input data bus enabled. REG19 bit 4  Bus address  Unique 4-bit address identifying this module on the input bus (if the input bus is enabled in REG19 bit 4). Ignore otherwise. This module acts as bus slave: it performs the read/write transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Output data flow  Input format  O= output data is pushed to the next module (for example to COM-2001, or COM-1011/18)  1 = output data is pulled by next module (for example by the COM-4004)  REG19 bit 0  Input format  O= 1-bit serial  1 = 2-bit parallel (see also input bus enable bit below).  REG19 bit 1  Ouput spectrum shaping filter enabled  Enables/Disables raised cosine square root output spectrum shaping filter.  0 = disabled  1 = enabled  REG19 bit 2  Spreading  Input bus enabled  Controls whether the input connection is point-to-point or point-to-multipoint over a data bus (via a COM-9004 demultiplexing connector for example).  The J1 input connector pinout is affected by this control bit.  0 = direct connection. Point to point.  1 = input data bus enabled.  REG19 bit 4  Bus address  Unique 4-bit address identifying this module on the input bus (if the input bus is enabled in REG19 bit 4). Ignore otherwise. This module acts as bus slave: it performs the read/write transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1 = on   REG18 bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| REG18 bit 7  Output data flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Output data flow    0 = output data is pushed to the next module (for example to COM-2001, or COM-1011/18)   1 = output data is pulled by next module (for example by the COM-4004)   REG19 bit 0   Input format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| flow module (for example to COM-2001, or COM-1011/18)  1 = output data is pulled by next module (for example by the COM-4004)  REG19 bit 0  Input format 0 = 1-bit serial 1 = 2-bit parallel (see also input bus enable bit below).  REG19 bit 1  Ouput spectrum shaping filter root output spectrum shaping filter enabled 1 = enabled  REG19 bit 2  Spreading Enable/Disables raised cosine square root output spectrum shaping filter. 0 = disabled 1 = enabled REG19 bit 2  Spreading Enable/Disable spectrum spreading. 0 = disabled 1 = enabled REG19 bit 3  Input bus enabled Controls whether the input connection is point-to-point or point-to-multipoint over a data bus (via a COM-9004 demultiplexing connector for example). The J1 input connector pinout is affected by this control bit. 0 = direct connection. Point to point. 1 = input data bus enabled. REG19 bit 4  Bus address Unique 4-bit address identifying this module on the input bus (if the input bus is enabled in REG19 bit 4). Ignore otherwise. This module acts as bus slave: it performs the read/write transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| COM-1011/18)  1 = output data is pulled by next module (for example by the COM-4004)  REG19 bit 0  Input format  0 = 1-bit serial 1 = 2-bit parallel (see also input bus enable bit below).  REG19 bit 1  Ouput spectrum shaping filter on enabled  Enables/Disables raised cosine square root output spectrum shaping filter. 0 = disabled 1 = enabled REG19 bit 2  Spreading  Enable/Disable spectrum spreading. 0 = disabled 1 = enabled REG19 bit 3  Input bus enabled Controls whether the input connection is point-to-point or point-to-multipoint over a data bus (via a COM-9004 demultiplexing connector for example). The J1 input connector pinout is affected by this control bit. 0 = direct connection. Point to point. 1 = input data bus enabled. REG19 bit 4  Bus address  Unique 4-bit address identifying this module on the input bus (if the input bus is enabled in REG19 bit 4). Ignore otherwise. This module acts as bus slave: it performs the read/write transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Input format  Input format  Ouput spectrum shaping filter enabled  Spreading  Input bus enabled  REG19 bit 2  Spreading  Input bus enabled  I = enabled  REG19 bit 3  Input bus enabled  I = enabled  REG19 bit 3  Input bus enabled  I = enabled  REG19 bit 3  Input bus enabled  Input connector pinout is affected by this control bit.  I = input data bus enabled.  REG19 bit 4  Input data bus enabled.  REG19 bit 4  Input bus enabled in REG19 bit 4). Ignore otherwise. This module acts as bus slave: it performs the read/write transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Input format  Input format  O = 1-bit serial 1 = 2-bit parallel (see also input bus enable bit below). REG19 bit 1  Ouput spectrum shaping filter enabled  Enables/Disables raised cosine square root output spectrum shaping filter.  O = disabled 1 = enabled REG19 bit 2  Spreading  Enable/Disable spectrum spreading. O = disabled 1 = enabled REG19 bit 3  Input bus enabled  Controls whether the input connection is point-to-point or point-to-multipoint over a data bus (via a COM-9004 demultiplexing connector for example). The J1 input connector pinout is affected by this control bit. O = direct connection. Point to point. 1 = input data bus enabled. REG19 bit 4  Bus address  Unique 4-bit address identifying this module on the input bus (if the input bus is enabled in REG19 bit 4). Ignore otherwise. This module acts as bus slave: it performs the read/write transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Input format  O = 1-bit serial 1 = 2-bit parallel (see also input bus enable bit below).  REG19 bit 1  Ouput spectrum shaping filter enabled  Enables/Disables raised cosine square root output spectrum shaping filter. O = disabled 1 = enabled REG19 bit 2  Spreading  Enable/Disable spectrum spreading. O = disabled 1 = enabled REG19 bit 3  Input bus enabled  Controls whether the input connection is point-to-point or point-to-multipoint over a data bus (via a COM-9004 demultiplexing connector for example). The J1 input connector pinout is affected by this control bit. O = direct connection. Point to point. 1 = input data bus enabled. REG19 bit 4  Bus address  Unique 4-bit address identifying this module on the input bus (if the input bus is enabled in REG19 bit 4). Ignore otherwise. This module acts as bus slave: it performs the read/write transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Input format  0 = 1-bit serial 1 = 2-bit parallel (see also input bus enable bit below).  REG19 bit 1  Ouput spectrum shaping filter enabled  Enables/Disables raised cosine square root output spectrum shaping filter. 0 = disabled 1 = enabled REG19 bit 2  Spreading  Enable/Disable spectrum spreading. 0 = disabled 1 = enabled REG19 bit 3  Input bus enabled  Controls whether the input connection is point-to-point or point-to-multipoint over a data bus (via a COM-9004 demultiplexing connector for example). The J1 input connector pinout is affected by this control bit. 0 = direct connection. Point to point. 1 = input data bus enabled. REG19 bit 4  Bus address  Unique 4-bit address identifying this module on the input bus (if the input bus is enabled in REG19 bit 4). Ignore otherwise. This module acts as bus slave: it performs the read/write transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1 = 2-bit parallel (see also input bus enable bit below). REG19 bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| (see also input bus enable bit below).  REG19 bit 1  Ouput spectrum shaping filter enabled  Spreading  Enables/Disables raised cosine square root output spectrum shaping filter.  0 = disabled  1 = enabled  REG19 bit 2  Spreading  Enable/Disable spectrum spreading.  0 = disabled  1 = enabled  REG19 bit 3  Input bus enabled  Controls whether the input connection is point-to-point or point-to-multipoint over a data bus (via a COM-9004 demultiplexing connector for example).  The J1 input connector pinout is affected by this control bit.  0 = direct connection. Point to point.  1 = input data bus enabled.  REG19 bit 4  Bus address  Unique 4-bit address identifying this module on the input bus (if the input bus is enabled in REG19 bit 4). Ignore otherwise. This module acts as bus slave: it performs the read/write transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |