# COM-1229/1230 DUAL DEMODULATORS (n-FSK / n-PSK / QAM / APSK) with USB 2.0 / TCP-IP

# Key Features

- Dual demodulators

- Concurrent demodulation

- Independently programmable data rate and center frequency.

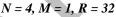

- <u>Demodulator 1</u>: continuous phase FSK (CPFSK) and its derivatives (MSK, GFSK, GMSK, 2-,4-,8-ary FSK).

- o Programmable 2-, 4-, 8-ary FSK

- Programmable modulation index h [0.125 to 4]

- Variable data rates up to 10 Msymbols/s =

- ✓ 30/20/10 Mbps. (8-, 4-, 2-ary FSK).

- Designed for continuous mode applications. Fast re-acquisition after short link interruption.

- <u>Demodulator 2</u>: BPSK, QPSK, OQPSK, 8PSK, 16QAM, 16APSK, 32APSK

- Variable data rates up to 20 Msymbols/s

- Demodulator complex (I&Q) input can be either

- digital (2 \* 10-bit complex, up to 80 Msamples/s)

- analog (64 Msamples/s).

- Demodulated data can be routed to

two synchronous serial interfaces

- USB 1.1/2.0.

- TCP-IP/LAN (COM-1230).

- Extensive monitoring:

- o Demodulator lock

- o Frequency error

- o AGC gain

- o SNR measurement.

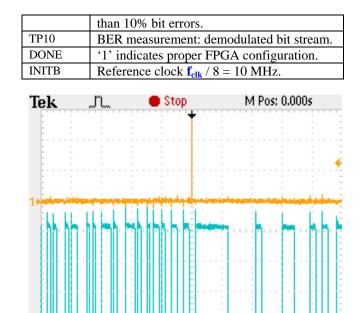

- BER measurement when transmitting PRBS-11 test sequence.

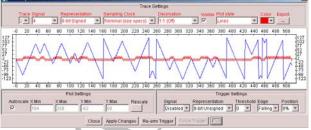

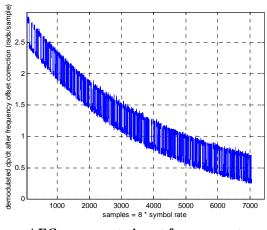

- ComScope –enabled: key internal signals can be captured in real-time and displayed on host computer.

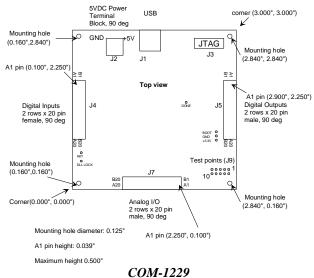

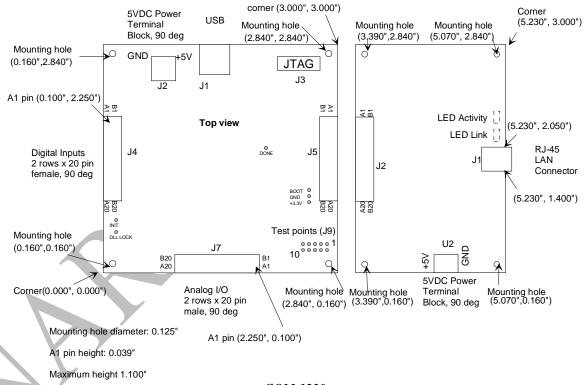

- Connectorized 3"x 3" module for ease of prototyping. Standard 40 pin 2mm dual row connectors (left, right, bottom). Single 5V supply with reverse voltage and overvoltage protection. Interfaces with 3.3V LVTTL logic.

For the latest data sheet, please refer to the **ComBlock** web site: <u>www.comblock.com/download/com1229.pdf</u>. These specifications are subject to change without notice.

For an up-to-date list of **ComBlock** modules, please refer to <u>www.comblock.com/product\_list.htm</u>.

COM-1230 (includes TCP-IP)

MSS • 18221 Flower Hill Way #A • Gaithersburg, Maryland 20879 • U.S.A. Telephone: (240) 631-1111 Facsimile: (240) 631-1676 <u>www.ComBlock.com</u> © MSS 2000-2006 Issued 2/5/2006

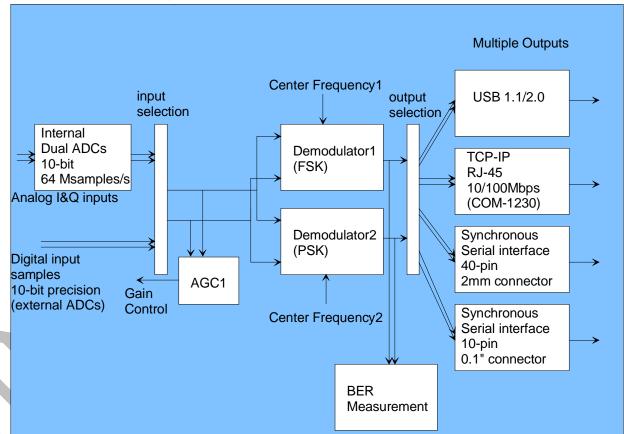

# **Overall Block Diagram**

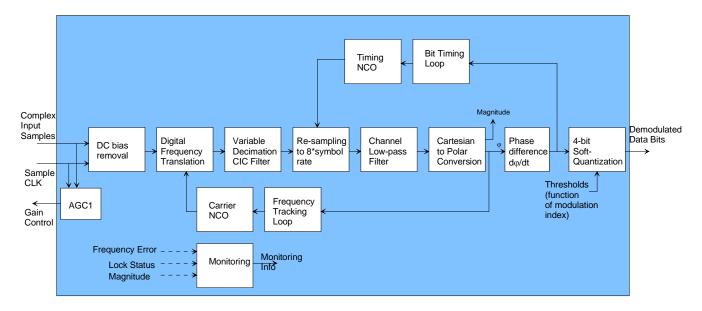

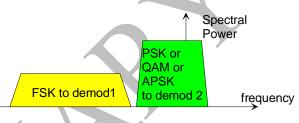

Block Diagram (FSK Digital Demodulator1)

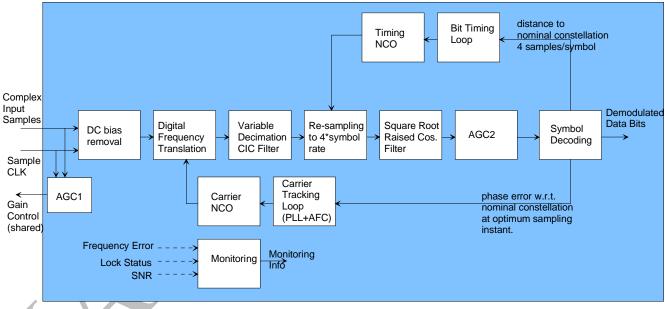

# Block Diagram (n-PSK / QAM / APSK Digital Demodulator2)

# **Electrical Interface**

|   | Digital Input   | Definition                                                   |

|---|-----------------|--------------------------------------------------------------|

|   | Interfaces (J4) |                                                              |

|   | DATA_I_IN[9:0]  | Modulated input signal, real axis.                           |

|   |                 | 10-bit precision. Synchronous with                           |

|   |                 | rising edge of CLK_IN. Format: 2's                           |

|   |                 | complement or unsigned.                                      |

|   |                 | Unused LSBs are pulled low.                                  |

| Y | DATA_Q_IN[9:0]  | Modulated input signal, imaginary                            |

|   |                 | axis. 10-bit precision. Same format                          |

|   |                 | as DATA_I_IN.                                                |

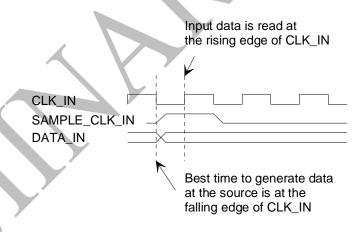

|   | SAMPLE_CLK_IN   | Input signal sampling clock $\mathbf{f}_{s}$ . One           |

|   |                 | CLK_IN-wide pulse. Read the                                  |

|   |                 | input signal at the rising edge of                           |

|   |                 | CLK_IN when SAMPLE_CLK_IN                                    |

|   |                 | = '1'.                                                       |

|   |                 | The minimum input sampling rate                              |

|   |                 | is 8 samples per symbol for FSK                              |

|   |                 | modulation and 4 samples/symbol                              |

|   |                 | for PSK, QAM and APSK                                        |

|   |                 | modulations. Samples can be                                  |

|   |                 | consecutive. For example,                                    |

|   |                 | SAMPLE_CLK_IN can be fixed at                                |

|   |                 | '1' to indicate that new input samples are provided once per |

|   |                 | CLK_IN clock period.                                         |

|   |                 | Signal is pulled-up.                                         |

|   | CLK_IN          | Input reference clock for                                    |

|   |                 | synchronous I/O. DATA_x_IN and                               |

|   |                 | SAMPLE CLK IN are read at the                                |

|   |                 | rising edge of CLK_IN. Maximum                               |

|   |                 | 80 MHz.                                                      |

|   |                 |                                                              |

| Analog        | Definition                                   |

|---------------|----------------------------------------------|

| Input         |                                              |

| Interfaces    |                                              |

| ( <b>J7</b> ) |                                              |

| RX_I_P /      | I-channel differential inputs. (_P for +,    |

| RX_I_N        | _N for -).                                   |

|               | 200 Ohm input impedance.                     |

|               | 2Vpp differential (1Vpp on each RX_I_P       |

|               | and RX_I_N signal) for full scale 10-bit     |

|               | ADC conversion.                              |

|               | Common-mode voltage is approximately         |

|               | 2.3V. It is recommended that the input be    |

|               | AC coupled.                                  |

| RX_Q_P /      | Q-channel differential inputs. (_P for +,    |

| RX_Q_N        | _N for -).                                   |

|               | Same electrical characteristics as above.    |

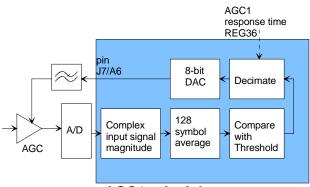

| RX_AGC1       | Output. When this demodulator is             |

|               | connected directly to an analog receiver,    |

|               | it generates an analog $0 - 3.3$ V signal to |

|               | control the analog gain prior to A/D         |

|               | conversion. The purpose is to use the        |

|               | maximum dynamic range while                  |

|               | preventing saturation at the A/D             |

|               | converter.                                   |

|               | 0 is the maximum gain, $+3.3V$ is the        |

|               | minimum gain.                                |

|               | Pin J7/A6.                                   |

| Output<br>Interfaces | Definition                                                                                                                                                                                                                |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB 2.0              | Type B receptacle. This interface<br>supports two virtual channels: one for<br>monitoring and control, the other to<br>convey a high-speed demodulated<br>data stream from demodulator<br>demod1 OR demod2 back to a host |

|    |           | computer. Use USB 2.0 approved                    |

|----|-----------|---------------------------------------------------|

|    |           | cable for connection to a host                    |

|    |           | computer. Maximum recommended                     |

|    |           | cable length is 3'.                               |

|    | LAN       | 4 wire. 10Base-T/100Base-TX. RJ45                 |

|    | (COM-1230 | connector. NIC wiring. Use standard               |

|    |           | category 5 cable for connection to a              |

|    |           | Hub/Switch. Use crossover cable for               |

|    |           | connection to a host computer.                    |

|    |           | This interface supports three virtual             |

|    |           | channels: one for monitoring and                  |

|    |           | control, the two other to convey                  |

|    |           | demodulated data from the two                     |

|    |           | demodulators back to a host                       |

|    |           | computer.                                         |

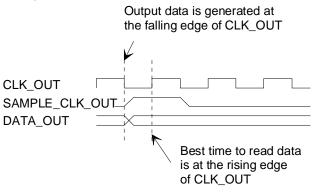

|    | DATA_OUT  |                                                   |

|    |           | the rising edge of CLK_OUT when                   |

|    |           | BIT CLK $OUT = '1'$ .                             |

|    |           | 4-bit soft-quantized demodulated bits             |

|    |           | for use by subsequent error correction            |

|    |           | decoders. Unsigned representation:                |

|    |           | 0000 for maximum amplitude '0',                   |

|    |           | 1111 for maximum amplitude '1'.                   |

|    |           | The information bit is the most                   |

|    |           | significant bit DATA_OUT(3).                      |

|    | BIT_CLK_O | T Demodulated bit clock. One CLK-                 |

|    |           | wide pulse. Read the output signal at             |

|    |           | the rising edge of CLK_OUT when                   |

|    |           | $BIT_CLK_OUT = '1'.$                              |

|    | RX_LOCK   | '1' when the demodulator is locked,               |

|    |           | '0' otherwise.                                    |

|    | CLK_OUT   | Output reference clock. Typically 40              |

| P* |           | MHz.                                              |

|    |           |                                                   |

|    | Power     | 4.75 – 5.25VDC. Terminal block. Power             |

|    | Interface | consumption is approximately proportional         |

|    |           | to the symbol clock rate $(f_{symbol_clk})$ . The |

|    |           | maximum power consumption is 650mA.               |

|    |           | 1 1                                               |

#### **Important: Digital I/O signals are 0-3.3V** LVTTL. Inputs are NOT 5V tolerant!

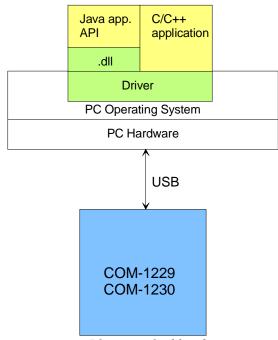

# Configuration

5

Complete ComBlock assemblies can be monitored and controlled centrally over a single USB (default), TCP-IP/LAN (COM-1230), Serial or PC Card connection (via adjacent ComBlocks).

The module configuration parameters are stored in non-volatile memory. All control registers are read/write.

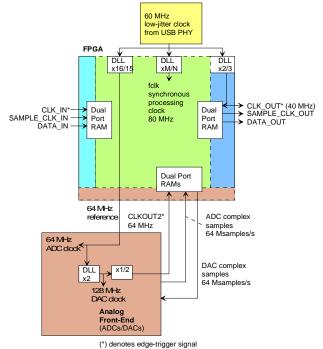

This module operates at a fixed internal clock rate  $\mathbf{f}_{clk}$  of 80 MHz.

| n-FSK Demodulator1             |                                                       |  |

|--------------------------------|-------------------------------------------------------|--|

| Parameters                     | Configuration                                         |  |

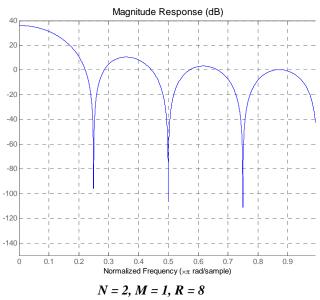

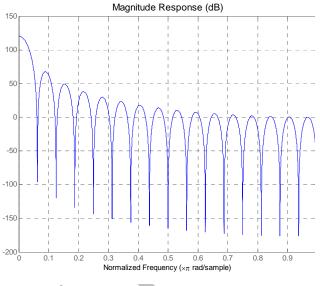

| Variable                       | Set the CIC Filter characteristics:                   |  |

| Decimation                     | CIC_N number of stages, 1 to 8                        |  |

|                                | CIC_M differential delay 1 to 2                       |  |

|                                | CIC R decimation 1 to 16384                           |  |

|                                | Number of truncated output bits: 0 to 63              |  |

|                                |                                                       |  |

|                                | Set $R = 1$ to bypass this stage.                     |  |

|                                | REG0 bits 3-0: CIC_N                                  |  |

|                                | REG0 bits 5-4: CIC_M                                  |  |

|                                | REG1: CIC_R LSB                                       |  |

|                                | REG2: CIC_R MSB                                       |  |

|                                | REG3 bits 5 - 0: number of truncated                  |  |

|                                |                                                       |  |

|                                | output bits                                           |  |

| Nominal                        | 32-bit unsigned integer expressed as                  |  |

| Symbol rate                    | fsymbol rate * $2^{32}$ / <b>f</b> <sub>clk</sub> .   |  |

| $(f_{symbol\_clk})$            | The maximum symbol rate is $f_{clk}/8$                |  |

|                                | (0x1FFFFFFF).                                         |  |

|                                | The data rate is 1x, 2x or 3x the symbol              |  |

|                                | rate depending on the M-ary number set                |  |

|                                | in REG15.                                             |  |

|                                |                                                       |  |

|                                | REG5 = bit 7-0 (LSB)                                  |  |

|                                | REG6 = bit 15 - 8                                     |  |

|                                | REG7 = bit 23 - 16                                    |  |

|                                | REG8 = bit 31 - 23 (MSB)                              |  |

| Nominal                        | This frequency value is subtracted from               |  |

| Center                         | the received signal actual center                     |  |

| frequency ( $\mathbf{f}_{c}$ ) | frequency.                                            |  |

|                                |                                                       |  |

|                                | 32-bit signed integer (2's complement                 |  |

|                                | representation) expressed as $2^{32}$ (2)             |  |

|                                | $\mathbf{f_c} * 2^{32} / \mathbf{f_{clk}}.$           |  |

|                                | Maximum theoretical range: $\pm \mathbf{f}_{clk}$ /2. |  |

|                                | REG9 = bit 7-0 (LSB)                                  |  |

|                                | REG10 = bit 15 - 8                                    |  |

|                                | REG11 = bit 23 - 16                                   |  |

|                                | REG12 = bit 31 - 23 (MSB)                             |  |

| Inverse                        | 1/(Modulation index h). Format 8.8                    |  |

| Modulation                     |                                                       |  |

| Index 1/h                      | Thus, 0x0200 represents the inverse of a              |  |

|                                | modulation index of 0.5. (MSK or                      |  |

|                                | GMSK modulation imply $h = 0.5$ ). Valid              |  |

|                                | range for <b>1/h</b> : 0.125 – 4                      |  |

|                                | REG13: bits 7:0 LSB                                   |  |

|                                | REG14: bit 15:8: MSB                                  |  |

| M-ary number                   | Size of the symbol alphabet:                          |  |

| -                              | 00 = 2-ary, 2-FSK, M=2                                |  |

|                                | 01 = 4-ary, 4-FSK, M=4                                |  |

|                                | 10 = 4-ary, 4-1-SK, M=4<br>10 = 8-ary, 8-FSK, M=8     |  |

|                                | •                                                     |  |

| ~                              | REG15 bits 1-0                                        |  |

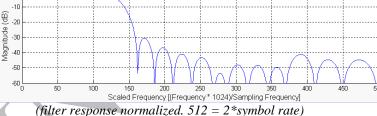

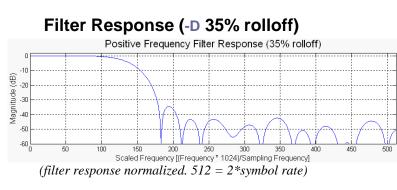

| Channel filter                 | Selects the channel filter:                           |  |

| selection                      | 00 = no filter                                        |  |

|                                | 01 = raised cosine filter 25% rolloff.                |  |

|                                | REG15 bits 3-2                                        |  |

| Spectrum                       | Invert Q bit.                                         |  |

| inversion                      |                                                       |  |

|                                | Flips the baseband modulation spectrum.               |  |

|                                | Does not affect any frequency error.<br>0 = off       |  |

|                                |                                                       |  |

|        |                              | 1                                                     | Г |

|--------|------------------------------|-------------------------------------------------------|---|

|        |                              | 1 = on                                                |   |

|        | AFC enable                   | REG15 bit 4                                           |   |

|        | AFC enable                   | An automatic frequency control circuit                |   |

|        |                              | can be enabled to acquire and track the               |   |

|        |                              | received signal center frequency in                   |   |

|        |                              | applications where the frequency error is             |   |

|        |                              | prohibitive.                                          |   |

|        |                              | 00 = automatic AFC selection based on                 |   |

|        |                              | the lock status.                                      |   |

|        |                              | 01 = force AFC disabled. No carrier                   |   |

|        |                              | acquisition and tracking.                             |   |

|        |                              | 10 = force AFC enabled.                               |   |

|        | Г                            | REG15 bits 6-5                                        |   |

|        | Force<br>(Re-)               | A one-time write of '1' forces the loops              |   |

|        | acquisition                  | back into acquisition mode. This can be               |   |

|        | acquisition                  | used to get out of any potential false                |   |

|        |                              | lock condition. There is no need to clear             | - |

|        |                              | this bit.                                             |   |

|        | DOUGANU                      | REG15 bit 7                                           |   |

|        | n-PSK/QAM/<br>Parameters     | APSK Demodulator2                                     |   |

|        | Variable                     | Configuration Set the CIC Filter characteristics:     | - |

|        | Decimation                   | CIC_N number of stages, 1 to 8                        |   |

|        | Deemanon                     | CIC_M differential delay 1 to 2                       |   |

|        |                              | CIC_R decimation 1 to 16384                           |   |

|        |                              | Number of truncated output bits: 0 to 63              |   |

|        |                              | Number of francated output bits. 0 to 05              |   |

|        |                              | Set $\mathbf{R} = 1$ to bypass this stage.            |   |

|        |                              |                                                       | Ī |

|        |                              | REG18: bits 3-0: CIC_N                                |   |

|        |                              | REG18: bits 5-4: CIC_M                                |   |

|        |                              | REG19: CIC_R LSB                                      |   |

|        |                              | REG20: CIC_R MSB                                      |   |

| -<br>- |                              | REG21 bits 5 - 0: number of truncated                 |   |

|        |                              | output bits                                           |   |

|        | Nominal                      | 32-bit unsigned integer expressed as                  |   |

|        | Symbol rate                  | fsymbol rate * $2^{32}$ / $\mathbf{f}_{clk}$ .        |   |

|        | (f <sub>symbol_clk</sub> )   | The maximum symbol rate is $\mathbf{f}_{elk}/4$       |   |

|        |                              | (0x3FFFFFF).                                          |   |

|        |                              | The data rate is between 1x and 6x the                |   |

|        |                              | symbol rate depending on the                          | - |

|        |                              | modulation type.                                      |   |

|        |                              | REG23 = bit 7-0 (LSB)                                 |   |

|        |                              | REG24 = bit 15 - 8                                    |   |

|        |                              | REG25 = bit 23 - 16                                   |   |

|        |                              | REG26 = bit 31 - 23 (MSB)                             |   |

|        | Nominal                      | This frequency value is subtracted from               |   |

|        | Center                       | the received signal actual center                     |   |

|        | frequency $(\mathbf{f}_{c})$ | frequency.                                            |   |

|        |                              | 32-bit signed integer (2's complement                 |   |

|        |                              | representation) expressed as $1 + 2^{32} + 2^{32}$    |   |

|        |                              | $f_{c} * 2^{32} / f_{clk}$                            |   |

|        |                              | Maximum theoretical range: $\pm \mathbf{f}_{clk}$ /2. |   |

|        |                              | REG27 = bit 7-0 (LSB)                                 |   |

|        |                              | REG28 = bit 15 - 8                                    |   |

|        |                              | REG29 = bit 23 - 16                                   |   |

|        | Modulat                      | REG30 = bit 31 – 23 (MSB)                             |   |

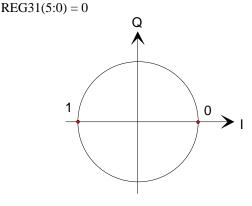

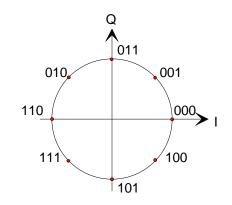

|        | Modulation                   | 0 = BPSK<br>1 - OPSK                                  | F |

|        | type                         | 1 = QPSK                                              | L |

|        |                              |                                                       |   |

|                    | 2 = OQPSK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | 3-7 = reserved for future QPSK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                    | constellations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

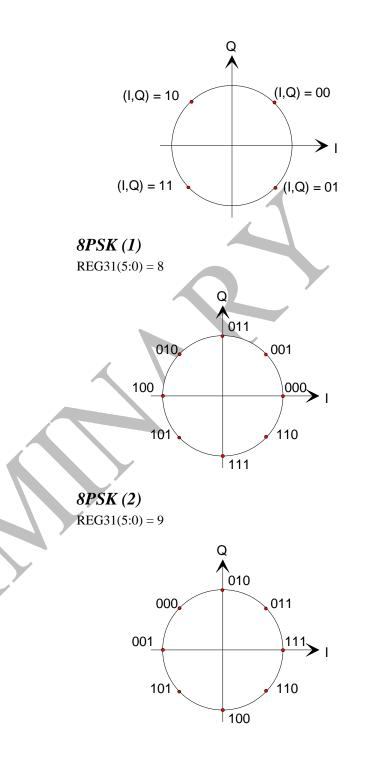

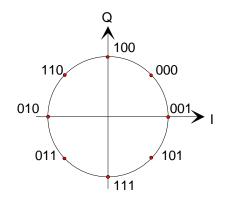

|                    | 8 = 8PSK constellation 8A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                    | 9 = 8PSK constellation 8B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                    | 10 = 8PSK constellation 8C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                    | 11 = 8PSK constellation $8D$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                    | 12-15 = reserved for future 8PSK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                    | constellations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

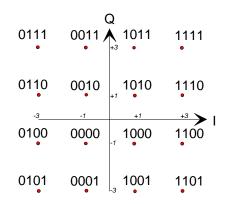

|                    | 16 = 16QAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                    | 17-23 reserved for future 16QAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                    | constellations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                    | 24 = 16APSK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    | 25-31 reserved for future 16APSK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                    | 32 = 32APSK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    | 33-39 reserved for future 32APSK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <b>G</b> (         | REG31 bits 5-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Spectrum           | Invert Q bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| inversion          | 0 = off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                    | 1 = on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                    | REG31 bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

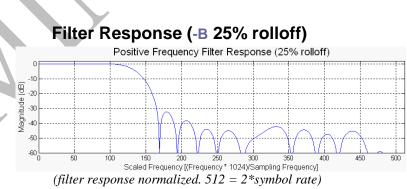

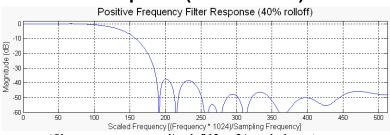

| Channel filter     | 0 = enable the root raised cosine filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| bypass             | (general case)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                    | 1 = bypass the root raised cosine filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                    | (special use in applications when a root                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                    | raised cosine filter is not used in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                    | modulator.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    | REG31 bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Carrier            | 00 = nominal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| frequency          | 01 = 2x loop gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| tracking loop      | 10 = 4x loop gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                    | 10 - 4x 100p gam                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| gain               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| gain               | 11 = 8x loop gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| gain               | 11 = 8x loop gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| gain               | 11 = 8x loop gain<br>The loop gain can be changed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| gain               | <ul><li>11 = 8x loop gain</li><li>The loop gain can be changed dynamically to ease the transition</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| gain               | <ul><li>11 = 8x loop gain</li><li>The loop gain can be changed<br/>dynamically to ease the transition<br/>between acquisition and tracking. A</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| gain               | <ul><li>11 = 8x loop gain</li><li>The loop gain can be changed<br/>dynamically to ease the transition<br/>between acquisition and tracking. A<br/>higher loop gain can be used to increase</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| gain               | <ul><li>11 = 8x loop gain</li><li>The loop gain can be changed<br/>dynamically to ease the transition<br/>between acquisition and tracking. A</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| gain               | <ul><li>11 = 8x loop gain</li><li>The loop gain can be changed<br/>dynamically to ease the transition<br/>between acquisition and tracking. A<br/>higher loop gain can be used to increase</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| gain               | <ul> <li>11 = 8x loop gain</li> <li>The loop gain can be changed<br/>dynamically to ease the transition<br/>between acquisition and tracking. A<br/>higher loop gain can be used to increase<br/>acquisition range or to minimize cycle</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| gain               | <ul> <li>11 = 8x loop gain</li> <li>The loop gain can be changed<br/>dynamically to ease the transition<br/>between acquisition and tracking. A<br/>higher loop gain can be used to increase<br/>acquisition range or to minimize cycle<br/>slips at low data rate. A lower loop gain</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| gain<br>AFC enable | <ul> <li>11 = 8x loop gain</li> <li>The loop gain can be changed<br/>dynamically to ease the transition<br/>between acquisition and tracking. A<br/>higher loop gain can be used to increase<br/>acquisition range or to minimize cycle<br/>slips at low data rate. A lower loop gain<br/>minimizes demodulation losses.</li> <li>REG32 bits 1-0</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    | <ul> <li>11 = 8x loop gain</li> <li>The loop gain can be changed<br/>dynamically to ease the transition<br/>between acquisition and tracking. A<br/>higher loop gain can be used to increase<br/>acquisition range or to minimize cycle<br/>slips at low data rate. A lower loop gain<br/>minimizes demodulation losses.</li> <li>REG32 bits 1-0</li> <li>The automatic frequency control circuit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                    | 11 = 8x loop gain<br>The loop gain can be changed<br>dynamically to ease the transition<br>between acquisition and tracking. A<br>higher loop gain can be used to increase<br>acquisition range or to minimize cycle<br>slips at low data rate. A lower loop gain<br>minimizes demodulation losses.<br>REG32 bits 1-0<br>The automatic frequency control circuit<br>extendeds the frequency acquisition over                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                    | <ul> <li>11 = 8x loop gain</li> <li>The loop gain can be changed<br/>dynamically to ease the transition<br/>between acquisition and tracking. A<br/>higher loop gain can be used to increase<br/>acquisition range or to minimize cycle<br/>slips at low data rate. A lower loop gain<br/>minimizes demodulation losses.</li> <li>REG32 bits 1-0</li> <li>The automatic frequency control circuit<br/>extendeds the frequency acquisition over<br/>+/- 10% of the symbol rate. When</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                    | 11 = 8x loop gain<br>The loop gain can be changed<br>dynamically to ease the transition<br>between acquisition and tracking. A<br>higher loop gain can be used to increase<br>acquisition range or to minimize cycle<br>slips at low data rate. A lower loop gain<br>minimizes demodulation losses.<br>REG32 bits 1-0<br>The automatic frequency control circuit<br>extendeds the frequency acquisition over<br>+/- 10% of the symbol rate. When<br>disabled, the receiver only means of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                    | <ul> <li>11 = 8x loop gain</li> <li>The loop gain can be changed<br/>dynamically to ease the transition<br/>between acquisition and tracking. A<br/>higher loop gain can be used to increase<br/>acquisition range or to minimize cycle<br/>slips at low data rate. A lower loop gain<br/>minimizes demodulation losses.</li> <li>REG32 bits 1-0</li> <li>The automatic frequency control circuit<br/>extendeds the frequency acquisition over<br/>+/- 10% of the symbol rate. When<br/>disabled, the receiver only means of<br/>carrier acquisition is the carrier</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                  |

|                    | 11 = 8x loop gain<br>The loop gain can be changed<br>dynamically to ease the transition<br>between acquisition and tracking. A<br>higher loop gain can be used to increase<br>acquisition range or to minimize cycle<br>slips at low data rate. A lower loop gain<br>minimizes demodulation losses.<br>REG32 bits 1-0<br>The automatic frequency control circuit<br>extendeds the frequency acquisition over<br>+/- 10% of the symbol rate. When<br>disabled, the receiver only means of<br>carrier acquisition is the carrier<br>frequency tracking loop which is                                                                                                                                                                                                                                                                                                                                                                                                              |

|                    | 11 = 8x loop gain<br>The loop gain can be changed<br>dynamically to ease the transition<br>between acquisition and tracking. A<br>higher loop gain can be used to increase<br>acquisition range or to minimize cycle<br>slips at low data rate. A lower loop gain<br>minimizes demodulation losses.<br>REG32 bits 1-0<br>The automatic frequency control circuit<br>extendeds the frequency acquisition over<br>+/- 10% of the symbol rate. When<br>disabled, the receiver only means of<br>carrier acquisition is the carrier<br>frequency tracking loop which is<br>inherently limited to approximately 1%                                                                                                                                                                                                                                                                                                                                                                    |

|                    | 11 = 8x loop gain<br>The loop gain can be changed<br>dynamically to ease the transition<br>between acquisition and tracking. A<br>higher loop gain can be used to increase<br>acquisition range or to minimize cycle<br>slips at low data rate. A lower loop gain<br>minimizes demodulation losses.<br>REG32 bits 1-0<br>The automatic frequency control circuit<br>extendeds the frequency acquisition over<br>+/- 10% of the symbol rate. When<br>disabled, the receiver only means of<br>carrier acquisition is the carrier<br>frequency tracking loop which is<br>inherently limited to approximately 1%<br>of the symbol rate.                                                                                                                                                                                                                                                                                                                                             |

|                    | 11 = 8x loop gain<br>The loop gain can be changed<br>dynamically to ease the transition<br>between acquisition and tracking. A<br>higher loop gain can be used to increase<br>acquisition range or to minimize cycle<br>slips at low data rate. A lower loop gain<br>minimizes demodulation losses.<br>REG32 bits 1-0<br>The automatic frequency control circuit<br>extendeds the frequency acquisition over<br>+/- 10% of the symbol rate. When<br>disabled, the receiver only means of<br>carrier acquisition is the carrier<br>frequency tracking loop which is<br>inherently limited to approximately 1%<br>of the symbol rate.<br>The AFC should only be used during                                                                                                                                                                                                                                                                                                       |

|                    | 11 = 8x loop gain<br>The loop gain can be changed<br>dynamically to ease the transition<br>between acquisition and tracking. A<br>higher loop gain can be used to increase<br>acquisition range or to minimize cycle<br>slips at low data rate. A lower loop gain<br>minimizes demodulation losses.<br>REG32 bits 1-0<br>The automatic frequency control circuit<br>extendeds the frequency acquisition over<br>+/- 10% of the symbol rate. When<br>disabled, the receiver only means of<br>carrier acquisition is the carrier<br>frequency tracking loop which is<br>inherently limited to approximately 1%<br>of the symbol rate.<br>The AFC should only be used during<br>acquisition as it interferes with the                                                                                                                                                                                                                                                              |