# COM-1505SOFT INTEGRATED PSK MODEM VHDL source code overview / IP core

## Overview

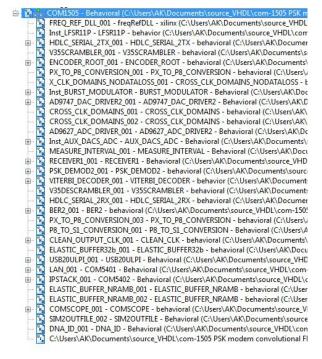

The COM-1505SOFT is a complete PSK modem written in VHDL, including PSK modulation, demodulation, convolutional error correction encoding and decoding, scrambling, HDLC framing, TCP-IP network interface and USB 2.0 interface. It is designed to be embodied within a single low-cost FPGA such as the Xilinx Spartan-6 LX45.

The entire **VHDL source code** is included.

#### Key features and performance:

- PSK (BPSK, QPSK, OQPSK) modulation

- Continuous mode operation (i.e. Burst mode is not supported)

- Convolution error correction, rates 1/2, 2/3, 3/4, 5/6 and 7/8.

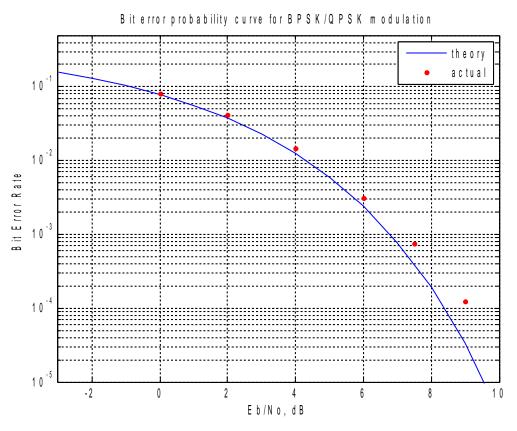

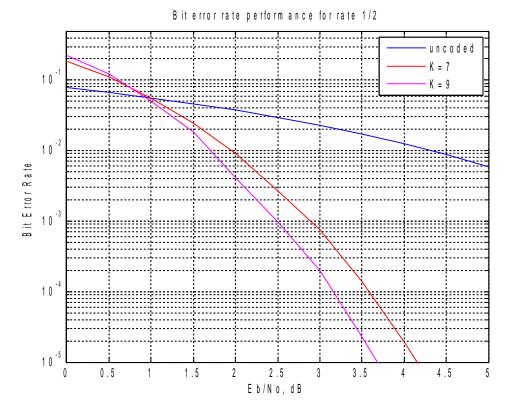

- Overall performance: 2.10<sup>-5</sup> BER @ 4dB Eb/No for K=7 rate ½ FEC.

- Serial HDLC to transmit empty frames over the synchronous link when no payload data is available.

- V.35 scrambling to randomize the modulated data stream.

- Maximum encoded data rate of 25 Msymbols/s when using a 100 MHz FPGA processing clock.

- User interfaces:

- Synchronous serial with elastic buffer or

- GbE TCP-IP server

- o USB 2.0 FS/HS

- Demodulator performance:

- BER: < 0.5 dB implementation losses w.r.t. theory

- Programmable frequency acquisition range.

- Demodulator acquisition threshold (uncoded) Eb/No = 2dB

- Ancillary components are also included for streaming, test signal generation and bit error rate measurement.

- Drivers for the high-speed and auxiliary DACs and ADCs are included for a seamless interface with popular Analog Devices analog/digital converters

# Target Hardware

The code is written in generic VHDL so that it can be ported to a variety of FPGAs. The code is developed and tested on a Xilinx Spartan-6 FPGA.

It can be easily ported to any Xilinx Kintex 7, Virtex-6, Virtex-5, Spartan-6 FPGAs and other FPGAs.

# **Overall Block Diagrams**

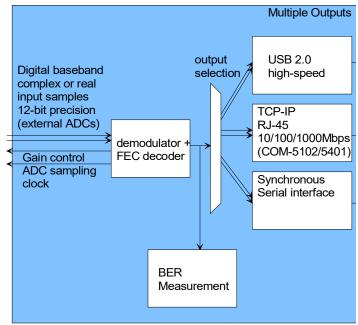

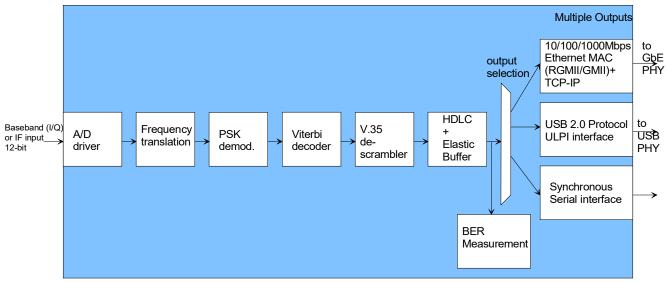

**Demodulator connectivity**

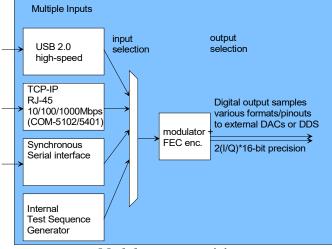

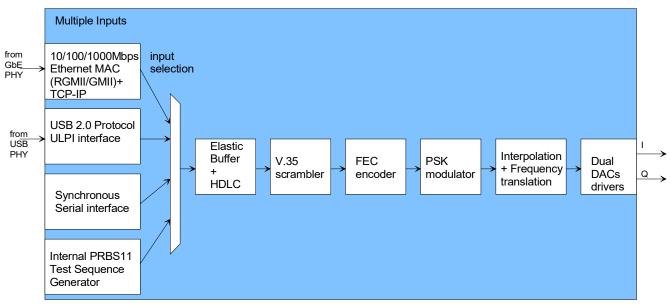

Modulator connectivity

#### Synthesis-time configuration parameters

In the *COM1505.vhd* component, set the **OPTION** constant as

-A for LAN and USB interfaces

-B for synchronous serial (clk + data + cts) and USB interfaces

-C for synchronous serial (clk + data), no HDLC.

#### **Run-time configuration parameters**

The user can set and modify the following controls at run-time through 8-bit control registers REGx, as listed below. The baseline code is written so that control registers REGx are written by an external microcontroller through a simple 8-bit address/data bus. See process UC WRITE 001.

| Transmitter                          |                                                                            |  |  |  |

|--------------------------------------|----------------------------------------------------------------------------|--|--|--|

| Parameters                           | Configuration                                                              |  |  |  |

| Input selection / format, test modes | Select the origin of the transmitter input data stream.                    |  |  |  |

|                                      | 0 = high-speed USB, 8-bit parallel                                         |  |  |  |

|                                      | 1 = LAN/TCP-IP, port 1024<br>(through Ethernet adapter), 8-bit<br>parallel |  |  |  |

|                                      | 2 = 1-bit synchronous serial                                               |  |  |  |

|                                      | 3 = internal PRBS-11 test sequence                                         |  |  |  |

|                                      | 5 = unmodulated carrier                                                    |  |  |  |

|                                      | 8-bit parallel input bytes are transmitted MSb first.                      |  |  |  |

|                                      | REG5(3:0)                                                                  |  |  |  |

| FEC convolu                                | itional encoder                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameters                                 | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Constraint                                 | 0001 = (K = 7, R=1/2, Intelsat)                                                                                                                                                                                                                                                                                                                                                                                                          |

| length K and                               | 0010 = (K = 7, R = 2/3, Intelsat)                                                                                                                                                                                                                                                                                                                                                                                                        |

| rate R                                     | 0011 = (K = 7, R = 3/4, Intelsat)                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                            | 0100 = (K = 7, R=5/6, Intelsat)                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                            | 0101 = (K = 7, R = 7/8, Intelsat)                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                            | REG12(4:1)                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Differential<br>Encoding                   | Differential encoding is useful in<br>removing phase ambiguities at the PSK<br>demodulator, at the expense of doubling<br>the bit error rate.<br>When enabled, the differential decoding<br>must be enabled at the receiving end.<br>There is no need to use the differential<br>encoding to remove phase ambiguities at<br>the PSK demodulator when the Viterbi<br>decoder and HDLC decoder are enabled.<br>0 = disabled<br>1 = enabled |

|                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Bypass FEC<br>encoding                     | $\frac{\text{REG12(5)}}{0 = \text{encoding enabled}}$                                                                                                                                                                                                                                                                                                                                                                                    |

| cheoding                                   | 1 = bypass                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                            | REG12(6)                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| V.35/Intelsat                              | 0 = enabled                                                                                                                                                                                                                                                                                                                                                                                                                              |

| IESS 308<br>scrambling                     | 1 = bypass                                                                                                                                                                                                                                                                                                                                                                                                                               |

| before FEC<br>encoding                     | REG12(7)                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| HDLC                                       | 0 = enabled                                                                                                                                                                                                                                                                                                                                                                                                                              |

| encoding                                   | 1 = bypass                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                            | REG12(0)                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PSK Modula                                 | ator                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Parameters                                 | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Processing<br>clock<br>f <sub>clk_tx</sub> | Modulator processing clock. Also serves as DAC sampling clock.                                                                                                                                                                                                                                                                                                                                                                           |

|                                            | 20-bit unsigned integer expressed as $f_{elk_tx} * 2^{20} / 300$ MHz.                                                                                                                                                                                                                                                                                                                                                                    |

|                                            | 120 MHz maximum.                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                            | 20 MHz recommended minimum                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                            | REG0 = bits 7-0 (LSB)                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                            | $REG1 = bits \ 15 - 8 \ (MSB)$                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                            | REG2(3:0) = bits 19 – 16 (MSB)                                                                                                                                                                                                                                                                                                                                                                                                           |

| Internal/Externa<br>l frequency<br>reference | 0 = internal. Use the internal 60 MHz<br>clock (from the USB PHY) as<br>frequency reference.                                                                                                                                                                                                                                            |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                              | 1 = external. Use the 10 MHz clock<br>externally supplied through the J7<br>SMA connector as frequency<br>reference.                                                                                                                                                                                                                    |

|                                              | REG2(7)                                                                                                                                                                                                                                                                                                                                 |

| Symbol rate                                  | The modulator symbol rate is in the                                                                                                                                                                                                                                                                                                     |

| f <sub>symbol</sub> rate tx                  | form $\mathbf{f}_{symbol rate tx} = \mathbf{f}_{clk_tx} / 2^n$<br>where n ranges from 1 ( $\mathbf{f}_{clk_tx}$ is twice<br>the symbol rate) to 15 (symbol rate =<br>$\mathbf{f}_{clk_tx} / 65536$ ).                                                                                                                                   |

|                                              | n is defined in REG3(3:0)                                                                                                                                                                                                                                                                                                               |

| Modulation type                              | 0 = BPSK                                                                                                                                                                                                                                                                                                                                |

|                                              | 1 = QPSK                                                                                                                                                                                                                                                                                                                                |

|                                              | 2 = OQPSK                                                                                                                                                                                                                                                                                                                               |

|                                              | REG4(5:0)                                                                                                                                                                                                                                                                                                                               |

| Spectrum<br>inversion                        | Invert Q bit. This is helpful in<br>compensating any frequency<br>spectrum inversion occurring in a<br>subsequent RF frequency translation.<br>0 = off                                                                                                                                                                                  |

|                                              | 1 = on                                                                                                                                                                                                                                                                                                                                  |

|                                              | REG4(6)                                                                                                                                                                                                                                                                                                                                 |

| Channel filter<br>enabled                    | 0 = enable the spectrum shaping<br>filters (root raised cosine,<br>interpolation)                                                                                                                                                                                                                                                       |

|                                              | 1 = bypass the spectrum shaping<br>filters. (special use in applications<br>when a root raised cosine filter is not<br>used in the demodulator.)<br>REG4(7)                                                                                                                                                                             |

| Signal gain                                  |                                                                                                                                                                                                                                                                                                                                         |

| Signal gain                                  | Signal level.<br>16-bit unsigned integer.<br>The maximum level should be<br>adjusted to prevent saturation. The<br>settings may vary slightly with the<br>selected symbol rate. Therefore, we<br>recommend <u>checking for saturation at</u><br><u>the D/A converter</u> when changing<br>either the symbol rate or the signal<br>gain. |

|                                              | REG6 = bits 7-0 (LSB)<br>REG7= bits 15-8 (MSB)                                                                                                                                                                                                                                                                                          |

| Output                                  | Frequency translation.                                                                                                                                                                                           |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Center                                  | 32-bit signed integer (2's complement                                                                                                                                                                            |

| frequency                               | representation) expressed as                                                                                                                                                                                     |

| $(f_{cout})$                            | $f_{cout} * 2^{32} / f_{clk_tx}$                                                                                                                                                                                 |

|                                         | REG8 = bits 7-0 (LSB)                                                                                                                                                                                            |

|                                         | REG9 = bits 15 - 8                                                                                                                                                                                               |

|                                         | REG10 = bits 23 – 16                                                                                                                                                                                             |

|                                         | REG11 = bits 31 – 23 (MSB)                                                                                                                                                                                       |

| Input bit rate                          | Option -C only                                                                                                                                                                                                   |

|                                         | Set the nominal input bit rate in order to<br>generate a regular bit clock to the data<br>source. Must be consistent with the<br>modulator symbol rate, modulation type<br>and FEC rate.                         |

|                                         | Example: 2 Mbps : x051EB852                                                                                                                                                                                      |

|                                         | $\mathbf{f}_{input bit rate tx} * 2^{32} / \mathbf{f}_{clk_rx}$                                                                                                                                                  |

|                                         | REG13 = bits 7-0 (LSB)                                                                                                                                                                                           |

|                                         | REG14 = bits 15 – 8                                                                                                                                                                                              |

|                                         | REG15 = bit 23 - 16                                                                                                                                                                                              |

|                                         | REG16 = bit 31 - 23 (MSB)                                                                                                                                                                                        |

| External<br>transmitter<br>gain control | When using an external transceiver such<br>as the COM-350x family, the transmitter<br>gain can be controlled through the<br>TX_GAIN_CNTRL1 analog output<br>signal. Range $0 - 3.3V$ .<br>REG17 = bits 7-0 (LSB) |

|                                         | REG18(3:0) = bits 11-8                                                                                                                                                                                           |

| External                                | REG19(0): TX_ENB                                                                                                                                                                                                 |

| transmitter<br>controls                 | $REG19(1) = RX_TXN$                                                                                                                                                                                              |

| PSK Demodulator<br>Parameters                  | r                                                                                                                                                                                                                                      |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameters                                     |                                                                                                                                                                                                                                        |

|                                                | Configuration                                                                                                                                                                                                                          |

|                                                | The demodulator processing clock<br>also serves as A/D converter<br>sampling clock.                                                                                                                                                    |

|                                                | It can be generated within the FPGA or externally.                                                                                                                                                                                     |

|                                                | Code baseline $\mathbf{f}_{clk_rx} = 100 \text{ MHz}$                                                                                                                                                                                  |

|                                                | Note: when using IF undersampling,<br>a dedicated oscillator is<br>recommended as the FPGA-<br>generated clock may show excessive<br>jitter (which translates into phase<br>noise).                                                    |

| rate                                           | The demodulator nominal symbol rate is in the form $f_{symbol rate rx} * 2^{32}$ /                                                                                                                                                     |

|                                                | f <sub>elk_rx</sub><br>REG25 = bits 7-0 (LSB)                                                                                                                                                                                          |

|                                                | REG26 = bits 15 - 8                                                                                                                                                                                                                    |

|                                                | REG27 = bit 23 - 16                                                                                                                                                                                                                    |

|                                                | REG28 = bit 31 – 23 (MSB)                                                                                                                                                                                                              |

| Nominal Center frequency $(\mathbf{f}_{c_rx})$ | Expected center frequency of the received signal. 32-bit signed integer (2's complement representation) expressed as $f_{e_rrx} * 2^{32} / f_{elk_rrx}$ .                                                                              |

|                                                | In the case of IF undersampling, the residual intermediate frequency is removed here. For example, in the case of a 125 MHz IF signal sampled at 100 Msamples/s, the 25 MHz residual frequency is removed here by entering 0x40000000. |

|                                                | REG29 = bit 7-0 (LSB)<br>REG30 = bit 15 - 8<br>REG31 = bit 23 - 16<br>REG32 = bit 31 - 23 (MSB)                                                                                                                                        |

| Modulation type                                | 0 = BPSK $1 = QPSK$                                                                                                                                                                                                                    |

|                                                | 2 = OQPSK<br>REG33(5:0)                                                                                                                                                                                                                |

|                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Spectrum<br>inversion                    | Invert Q bit. This is helpful in<br>compensating any frequency spectrum<br>inversion occurring during RF                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                          | frequency translations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                          | 0 = off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                          | 1 = on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                          | REG33(6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| High SNR                                 | To minimize the false lock probability at<br>high SNR, set this bit to '1' when Eb/No<br>is likely to exceed 10dB. To emphasize<br>operation at very low Eb/No, set this bit<br>to '0'<br>REG33(7)                                                                                                                                                                                                                                                                                                                                                    |

| Frequency<br>acquisition<br>range (scan) | The demodulator natural frequency<br>acquisition range is around 1% of the<br>symbol range (depending on<br>modulation, SNR). The frequency<br>acquisition range can be extended by<br>frequency scanning. Scanning steps are<br>spaced (f <sub>symbol rate rx</sub> /128) apart. The user<br>can thus trade-off acquisition time<br>versus frequency acquisition range by<br>specifying the number of scanning steps<br>here.<br>For example, 16 steps yield a frequency<br>acquisition range of +/-(f <sub>symbol rate rx</sub><br>*12.5%)<br>REG24 |

| AGC                                      | Users can to optimize the AGC response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| response time                            | time while avoiding instabilities<br>(depends on external factors such as<br>gain signal filtering at the RF front-end<br>and symbol rate). The response time is<br>approximately:                                                                                                                                                                                                                                                                                                                                                                    |

|                                          | 0 = 8 symbols,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                          | 1 = 16 symbols,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                          | 2 = 32 symbols,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                          | 3 = 64 symbols, etc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                          | 10 = every thousand symbols.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                          | Valid range 0 to 14.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                          | REG34(4:0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| AGC internal /                           | 0 = internal AGC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| external                                 | 1 = external AGC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                          | When selecting internal AGC mode, the<br>user is responsible for avoiding<br>saturation at or prior to the A/D<br>converter.                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                          | The internal AGC maximum gain is 256<br>in amplitude (48 dB in power).<br>Therefore, it is recommended to keep<br>the input samples amplitude between                                                                                                                                                                                                                                                                                                                                                                                                 |

|                           | maximum and maximum/256. In the input dynamic range is larger, please adjust the INTERNAL_AGC_005 process within <i>RECEIVER1.vhd</i> .                                                          |  |  |  |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                           | REG34(7)                                                                                                                                                                                         |  |  |  |

| Input selection           | 0 = digital real 12-bit unsigned samples,<br>right connector, COM-3504 transceiver.<br>Use in the case of IF input signal.                                                                       |  |  |  |

|                           | <ul> <li>1 = digital complex 2*12-bit unsigned<br/>samples, right connector, COM-3504<br/>transceiver</li> <li>Use in case of baseband (near-zero<br/>center frequency) input signal.</li> </ul> |  |  |  |

|                           | 7 = internal loopback mode, from modulator.                                                                                                                                                      |  |  |  |

|                           | REG35(2:0)                                                                                                                                                                                       |  |  |  |

| Viterbi FEC d             | ecoder                                                                                                                                                                                           |  |  |  |

| Parameters                | Configuration                                                                                                                                                                                    |  |  |  |

| Constraint                | 0001 = (K = 7, R = 1/2, Intelsat)                                                                                                                                                                |  |  |  |

| length K and rate R       | 0010 = (K = 7, R = 2/3, Intelsat)                                                                                                                                                                |  |  |  |

|                           | 0011 = (K = 7, R = 3/4, Intelsat)                                                                                                                                                                |  |  |  |

|                           | 0100 = (K = 7, R = 5/6, Intelsat)                                                                                                                                                                |  |  |  |

|                           | 0101 = (K = 7, R = 7/8, Intelsat)                                                                                                                                                                |  |  |  |

|                           | REG37(4:1)                                                                                                                                                                                       |  |  |  |

| Differential<br>Decoding  | 0 = disabled                                                                                                                                                                                     |  |  |  |

| Decouning                 | 1 = enabled                                                                                                                                                                                      |  |  |  |

|                           | REG37(5)                                                                                                                                                                                         |  |  |  |

| Bypass FEC<br>decoding    | 0 = decoding enabled                                                                                                                                                                             |  |  |  |

| C C                       | 1 = bypass<br>PEC37(6)                                                                                                                                                                           |  |  |  |

| V.35/Intelsat             | $\frac{\text{REG37(6)}}{0 = \text{enabled}}$                                                                                                                                                     |  |  |  |

| IESS 308                  | 1 = bypass                                                                                                                                                                                       |  |  |  |

| descrambling<br>after FEC | REG37(7)                                                                                                                                                                                         |  |  |  |

| decoding                  |                                                                                                                                                                                                  |  |  |  |

| HDLC                      | 0 = enabled                                                                                                                                                                                      |  |  |  |

| decoding                  | 1 = bypass                                                                                                                                                                                       |  |  |  |

|                           | REG37(0)                                                                                                                                                                                         |  |  |  |

| Output selection          | 0 = high-speed USB, 8-bit parallel                                                                                                                                                               |  |  |  |

| 3010011011                | 1 = LAN/TCP-IP, port 1024 (through<br>Ethernet adapter), 8-bit parallel                                                                                                                          |  |  |  |

|                           | 2 = 1-bit synchronous serial                                                                                                                                                                     |  |  |  |

|                           | 3 = exclusively to the BER                                                                                                                                                                       |  |  |  |

|                           | measurement                                                                                                                                                                                      |  |  |  |

|                           | REG36(2:0)                                                                                                                                                                                       |  |  |  |

| Enable test<br>points     | Enable (1)/Disable (0) test points on J6                                                                                                                                                         |  |  |  |

| Points                    | connector<br>REG36(7)                                                                                                                                                                            |  |  |  |

|                           |                                                                                                                                                                                                  |  |  |  |

| Network Interface             |                                                                     |  |

|-------------------------------|---------------------------------------------------------------------|--|

| Parameters                    | Configuration                                                       |  |

| IP address<br>(when           | 4-byte IPv4 address.                                                |  |

| connected to<br>Gbit Ethernet | Example : 0x AC 10 01 80 designates address 172.16.1.128            |  |

| PHY like                      | The new address becomes effective immediately (no need to reset the |  |

| COM-5102,<br>COM-5104)        | ComBlock).                                                          |  |

|                               | REG41: MSB                                                          |  |

|                               | REG42                                                               |  |

|                               | REG43                                                               |  |

|                               | REG44: LSB                                                          |  |

(Re-)Writing to the last control register REG44 is recommended after a configuration change to enact the change.

# **Configuration example 1**

#### Modulator:

2 Msymbols/s modulation, BPSK, convolutional encoding K=7 R=1/2, PRBS-11 test sequence, baseband (0Hz) complex (I/Q) modulated output signal.

#### Demodulator:

2 Msymbols/s, BPSK, convolutional encoding K=7 R=1/2, internal AGC with response speed 8, internal loopback mode, demodulated data directly to BER measurement.

IP address 172.16.1.128

MAC address: 00 01 02 03 04 05

| COM1505 PS                                                      | SK Mo    | dem, Conv   | olutio | onal FEC, T | CP-IP I   | Network I | <b>X</b> |

|-----------------------------------------------------------------|----------|-------------|--------|-------------|-----------|-----------|----------|

| -Registers-                                                     | All regi | ster values | in HE  | ĸ           |           |           |          |

| Reg 0                                                           | D0       | Reg 13      | 00     | Reg 26      | <b>B8</b> | Reg 39    | 00       |

| Reg 1                                                           | 69       | Reg 14      | 00     | Reg 27      | 1E        | Reg 40    | 00       |

| Reg 2                                                           | 03       | Reg 15      | 00     | Reg 28      | 05        | Reg 41    | AC       |

| Reg 3                                                           | 05       | Reg 16      | 00     | Reg 29      | 00        | Reg 42    | 10       |

| Reg 4                                                           | 00       | Reg 17      | 00     | Reg 30      | 00        | Reg 43    | 01       |

| Reg 5                                                           | 03       | Reg 18      | 00     | Reg 31      | 00        | Reg 44    | 80       |

| Reg 6                                                           | 30       | Reg 19      | 00     | Reg 32      | 00        | Reg 45    | 00       |

| Reg 7                                                           | 75       | Reg 20      | 00     | Reg 33      | 00        | Reg 46    | 01       |

| Reg 8                                                           | 00       | Reg 21      | 00     | Reg 34      | 08        | Reg 47    | 02       |

| Reg 9                                                           | 00       | Reg 22      | 00     | Reg 35      | 07        | Reg 48    | 03       |

| Reg 10                                                          | 00       | Reg 23      | 00     | Reg 36      | 03        | Reg 49    | 04       |

| Reg 11                                                          | 00       | Reg 24      | 00     | Reg 37      | 02        |           |          |

| Reg 12                                                          | 02       | Reg 25      | 52     | Reg 38      | 00        |           |          |

| Configuration<br>Configuration option currently loaded: , rev 1 |          |             |        |             |           |           |          |

|                                                                 | App      | y I         |        | Ok          | C         | ancel     |          |

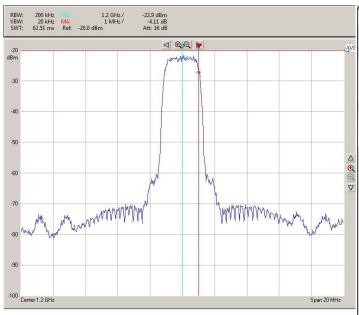

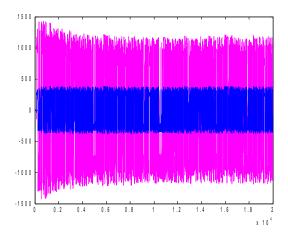

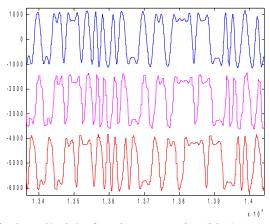

*Typical RF output spectrum (after D/A conversion and direct RF modulation)*

## **Configuration example 2**

#### Modulator:

144 Ksymbols/s modulation, BPSK, convolutional encoding K=7 R=1/2, from LAN/TCP-IP, baseband (0Hz) complex (I/Q) modulated output signal.

#### Demodulator:

144 Ksymbols /s, BPSK, convolutional encoding K=7 R=1/2, internal AGC with response speed 8, internal loopback mode, demodulated data to LAN/TCP-IP

IP address 172.16.1.128 MAC address: 00 01 02 03 04 05

| COM1505 P                                                       | SK Mo      | dem, Conv    | oluti | onal FEC, T | CP-IP | Network I | <b>X</b> |

|-----------------------------------------------------------------|------------|--------------|-------|-------------|-------|-----------|----------|

| Registers                                                       |            |              |       |             |       |           |          |

| 8                                                               | All reg    | ister values | in HE | х           |       |           |          |

| Reg 0                                                           | <b>A</b> 2 | Reg 13       | 00    | Reg 26      | 5F    | Reg 39    | 00       |

| Reg 1                                                           | EE         | Reg 14       | 00    | Reg 27      | 5E    | Reg 40    | 00       |

| Reg 2                                                           | 03         | Reg 15       | 00    | Reg 28      | 00    | Reg 41    | AC       |

| Reg 3                                                           | 09         | Reg 16       | 00    | Reg 29      | 00    | Reg 42    | 10       |

| Reg 4                                                           | 00         | Reg 17       | 00    | Reg 30      | 00    | Reg 43    | 01       |

| Reg 5                                                           | 01         | Reg 18       | 00    | Reg 31      | 00    | Reg 44    | 80       |

| Reg 6                                                           | 30         | Reg 19       | 00    | Reg 32      | 00    | Reg 45    | 00       |

| Reg 7                                                           | 75         | Reg 20       | 00    | Reg 33      | 00    | Reg 46    | 01       |

| Reg 8                                                           | 00         | Reg 21       | 00    | Reg 34      | 08    | Reg 47    | 02       |

| Reg 9                                                           | 00         | Reg 22       | 00    | Reg 35      | 07    | Reg 48    | 03       |

| Reg 10                                                          | 00         | Reg 23       | 00    | Reg 36      | 01    | Reg 49    | 04       |

| Reg 11                                                          | 00         | Reg 24       | 00    | Reg 37      | 02    |           |          |

| Reg 12                                                          | 02         | Reg 25       | 31    | Reg 38      | 00    |           |          |

| Configuration<br>Configuration option currently loaded: , rev 1 |            |              |       |             |       |           |          |

|                                                                 | Арр        | ly           |       | Ok          | 0     | ancel     |          |

# **Configuration example 3**

Same as above with 70 MHz IF input (requires an external anti-aliasing bandbass filter) Set REG32/31/30/29 to B3 33 33 (-30 MHz).

# **Status Registers**

The baseline code is written so that 8-bit status registers SREGx are read by an external microcontroller through an 8-bit address/data bus. See process UC\_READ\_001.

#### Digital status registers are read-only.

| PSK/QAM/A                                   | PSK/QAM/APSK Demodulator Monitoring                                                                                                                                                                                                                                                                                                          |  |  |  |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Parameters                                  | Monitoring                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Front-end<br>AGC                            | 8-bit unsigned value prior to DAC<br>conversion to RX_AGC1. Inverted scale:<br>0 is for the maximum gain.<br>SREG10                                                                                                                                                                                                                          |  |  |  |

| Carrier<br>frequency<br>offset<br>(fcdelta) | Residual frequency offset with respect to<br>the nominal carrier frequency.<br>24-bit signed integer (2's complement)<br>expressed as<br>fcdelta * $2^{24}$ / $f_{clk_rx}$ .<br>SREG11 = LSB                                                                                                                                                 |  |  |  |

|                                             | SREG11 = LSB<br>SREG12                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                             |                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Carrier<br>tracking loop<br>lock status     | SREG13 = MSB<br>Lock is declared if the standard deviation<br>of the phase error is less than 25deg rms.<br>0 = unlocked                                                                                                                                                                                                                     |  |  |  |

|                                             | 1 = locked                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                                             | SREG14(0)                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| Inverse SNR                                 | A measure of noise over signal power.                                                                                                                                                                                                                                                                                                        |  |  |  |

|                                             | 0 represents a noiseless signal. Valid only when demodulator is locked.                                                                                                                                                                                                                                                                      |  |  |  |

|                                             | SREG15                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Viterbi FEC d                               | ecoder monitoring                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Parameters                                  | Monitoring                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Synchronized                                | (FEC_DEC_LOCK_STATUS variable)<br>Solid '1' when the Viterbi decoder is<br>locked. '0' or toggling when unlocked.<br>SREG14(1)                                                                                                                                                                                                               |  |  |  |

| Decoder<br>built-in BER                     | The Viterbi decoder computes the BER<br>on the received (encoded) data stream<br>irrespective of the transmitted bit stream.<br>Encoded stream bit errors detected over a<br>1000-bit measurement window (unless<br>modified in <i>com1509pkg.vhd</i> ).<br>SREG16 = bits 7 – 0 (LSB)<br>SREG17 = bits 15 – 8<br>SREG18 = bits 23 – 16 (MSB) |  |  |  |

| HDLC decoder monitoring         |                                                                                                                                  |  |  |  |  |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Parameters                      | Monitoring                                                                                                                       |  |  |  |  |

| Cumulative                      | SREG19: LSB                                                                                                                      |  |  |  |  |

| number of valid<br>bits at HDLC | SREG20:                                                                                                                          |  |  |  |  |

| output                          | SREG21:                                                                                                                          |  |  |  |  |

| •                               | SREG22: MSB                                                                                                                      |  |  |  |  |

| BER Measurer                    | nent                                                                                                                             |  |  |  |  |

| Parameters                      | Monitoring                                                                                                                       |  |  |  |  |

| Bit Errors                      | Bit errors can be counted when a PRBS-<br>11 test sequence is transmitted.                                                       |  |  |  |  |

|                                 | Number of bit errors in a 1,000,000 bit window.                                                                                  |  |  |  |  |

|                                 | 32 bit unsigned.                                                                                                                 |  |  |  |  |

|                                 | SREG23: error_count[7:0] (LSB)                                                                                                   |  |  |  |  |

|                                 | SREG24: error_count[15:8]                                                                                                        |  |  |  |  |

|                                 | SREG25: error_count[23:16]                                                                                                       |  |  |  |  |

|                                 | SREG26: error_count[31:24] (MSB)                                                                                                 |  |  |  |  |

|                                 | The bit errors counter is updated once<br>every periodic measurement window.<br>Reading the value will not reset the<br>counter. |  |  |  |  |

| BER                             | 0 = not synchronized. 2047-bit pattern is                                                                                        |  |  |  |  |

| Synchronization                 | not detected.                                                                                                                    |  |  |  |  |

| status                          | 1 = synchronized                                                                                                                 |  |  |  |  |

|                                 | SREG27(0)                                                                                                                        |  |  |  |  |

| <b>TCP-IP</b> Conne             | ction Monitoring                                                                                                                 |  |  |  |  |

| Parameters                      | Monitoring                                                                                                                       |  |  |  |  |

| TCP-IP                          | Bit $0 = \text{port } 1028 \text{ (M&C) connected}$                                                                              |  |  |  |  |

| connection on                   | Bit $1 = \text{port } 1024 \text{ (data) connected}$                                                                             |  |  |  |  |

| port 1024                       | 1 for connected, 0 otherwise                                                                                                     |  |  |  |  |

| (data stream)                   | SREG28(1:0)                                                                                                                      |  |  |  |  |

| LAN PHY ID                      | Expect 0x22 when the PHY IC is Micrel KSZ9021.                                                                                   |  |  |  |  |

|                                 | SREG29(LSB)                                                                                                                      |  |  |  |  |

| MAC address                     | Unique 48-bit hardware address (802.3).<br>In the form SREG30:SREG31:SREG32:<br>:SREG35                                          |  |  |  |  |

|                                 | Since the MAC address is unique, it can<br>also be used as a unique identifier in a<br>radio network with many nodes.            |  |  |  |  |

Note: multi-words status registers such as frequency offset or BER, are latched upon reading status register SREG10.

# Troubleshooting checklist

1. Place modem in loopback mode (REG35 = 0x07) while sending a PRBS-11 test sequence (REG5 = 0x03). Be sure to direct the demodulated bit stream to the BER measurement (REG36 = 0x03).

Check the status registers for

- a. Demodulator and Viterbi decoder are locked: SREG14 = 0x03

- b. No Viterbi decoder errors: SREG16/17/18 = 0

- c. BER measurement is synchronized: SREG27 = 0x01

- d. No BER errors: SREG23/24/25/26 = 0

- e. Bits are being received at the HDLC decoder output: SREG19/20/21/22 counter keeps increasing at a rate consistent with the modulation rate.

# Operation

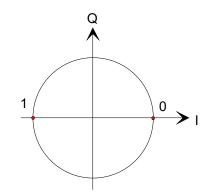

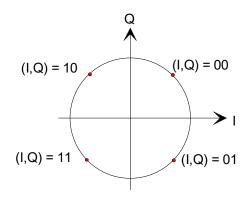

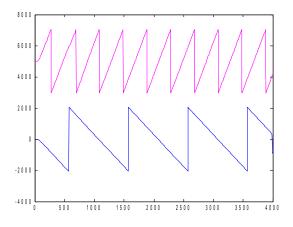

## **Constellation: Symbol Mapping**

The packing of serial data stream into symbols is done with the Most Significant bit first.

#### BPSK

#### **QPSK**

Gray encoding.

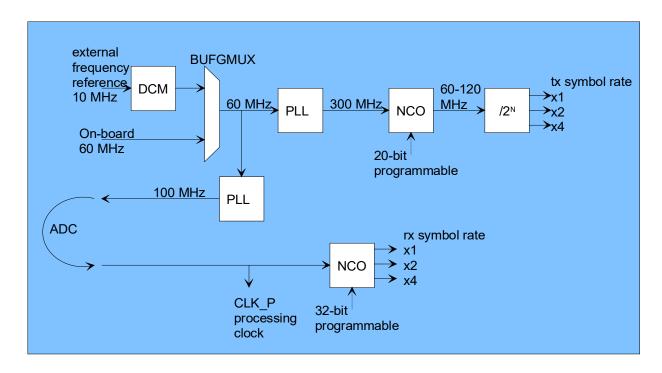

# **Clocks generation**

The software is written to accept a 10 MHz or a 60 MHz clock as frequency reference.

The design includes several clock domains:

CLK\_P: main processing clock (selected to be the same as the ADC sampling clock in this project).