### COM-1509SOFT CONVOLUTIONAL FEC ENCODER / VITERBI DECODER VHDL source code overview / IP core

#### **Overview**

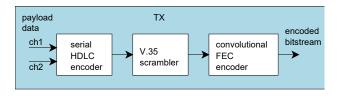

The COM-1509SOFT comprises the following components which can be independently instantiated:

- Convolutional FEC encoder,

- Viterbi decoder

- V.35 scrambler

- V.35 descrambler

- Serial HDLC framing

- Serial HDLC deframing

The entire **VHDL** source code is deliverable.

#### **Decoder key features**

- Single or parallel implementation for either minimum size or maximum (Gbps) speed.

- Flexible dynamic (i.e. at runtime) userselected configuration:

- Hard (1-bit) or soft(4-bit) decision decoding

- o G0,G1,G2 generator polynomials

- o Constraint length K=3,5,7,9

- O Puncturing patterns for rates 2/3,3/4,5/6,7/8

- o 2, 3, 7 parity bits

- Support for erasures (code puncturing)

- Reduced latency: K\*25 bits

- Self-synchronizing to automatically align the incoming encoded stream with the periodic encoding/puncturing pattern

- Out-of-sync indicator to synchronize external demodulator (for removing PSK demod phase ambiguity for example)

#### **Ancillary features:**

- V.35 scrambling and descrambling

- Serial HDLC framing/deframing. Serial HDLC encapsulates payload data in a frame

for transmission over a continuous data stream. 2 virtual channels can be multiplexed over the same stream. A 16-bit CRC is inserted at the end of each frame to detect errors upon reception. HDLC framing transmits empty frames when no payload data is available.

- PRBS11 test sequence generator

- BER testers

- Provided with IP core:

- > VHDL source code

- Matlab .m file to generate stimulus files for VHDL simulation at various signal to noise ratios

- VHDL testbench

### Target Hardware

The code is written in generic standard VHDL and is thus portable to a variety of FPGAs. The code was developed and tested on a Xilinx 7-series FPGA but is expected to work similarly on other targets. No manufacturer-specific primitive is used.

### Overall Block Diagram

### Configuration

### **Synthesis-time configuration parameters**

The following constants are user-defined in the generic section of the component instantiation prior to synthesis. These parameters generally define the size of the embodiment.

| Decoder synthesis-time configuration parameters           |                                                                                                                          |  |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| Parameters                                                | Configuration                                                                                                            |  |

| Number of parallel decoders instantiated NDEC             | Typical values: 1 (for minimum size serial architecture), 2,4,8 (for maximum throughput parallel architecture)           |  |

| Hard/Soft-decision<br>decoding<br>HARD_SOFTN_<br>DECISION | '1' for 1-bit width input '0' for 4-bit width input                                                                      |  |

| Maximum constraint length K_MAX                           | Valid values are 3,5,7,9                                                                                                 |  |

| Maximum number of parity bits  N_PARITY_BITS_MAX          | For example 3 for rate 1/3, or 2 for rate 2/3.                                                                           |  |

|                                                           | Valid range 2 - 7                                                                                                        |  |

|                                                           | Size vectors/arrays accordingly.                                                                                         |  |

|                                                           | If this decoder is only used with 2-bit parity, smaller implementations may be achieved by setting  N_PARITY_BITS_MAX= 2 |  |

| Traceback depth TB_DEPTH                                  | Traceback depth. MUST BE LESS THAN 120. Typically := 6*K_MAX for non-punctured codes or 12*K_MAX for punctured codes.    |  |

| HDLC tx/rx synthesis-time configuration parameters        |                                                                                                                          |  |

| Maximum HDLC frame size FRAME_SIZE_MAX                    | Maximum frame size (in bytes) before deciding to encode and send Valid range 0 - 2047 bytes                              |  |

#### Run-time configuration parameters

The user can set and modify the following controls at run-time through the top level component interface:

| Encoder             |                                                                                  |

|---------------------|----------------------------------------------------------------------------------|

| Parameters          | Configuration                                                                    |

| Constraint length K | 0000 = (K=5, R=1/7)                                                              |

| and rate R          | 0001 = (K = 7, R = 1/2, Intelsat)                                                |

|                     | 0010 = (K = 7, R = 2/3, Intelsat)                                                |

|                     | 0010  (K = 7,  R = 2/3,  Intersat)<br>0011 = (K = 7,  R = 3/4,  Intelsat)        |

|                     | 0100 = (K = 7, R = 5/6, Intelsat)                                                |

|                     | 0101 = (K = 7, R = 7/8, Intelsat)                                                |

|                     | 0110 = (K = 9, R=1/3)                                                            |

|                     | 0111 = (K = 9, R = 1/2)                                                          |

|                     | 1000 = (K = 9, R = 2/3)                                                          |

|                     | $1001 = (TCM, K=7, R=2/3)^1$                                                     |

|                     | $1010 = (TCM, K=7, R=3/4)^1$                                                     |

|                     | $1010 \text{ (ICM, K}^{-7}, \text{ K}^{-5/4})$<br>1011 = (K = 7, R = 1/2, CCSDS) |

|                     | 1100 = (K = 7, R = 2/3, CCSDS)                                                   |

|                     | 1100  (K  7,  K  2/3,  CCSDS)<br>1101 = (K = 7, R = 3/4,  CCSDS)                 |

|                     | 1110 = (K = 7, R = 5/6, CCSDS)                                                   |

|                     | 1110  (K = 7,  R = 7/8,  CCSDS)<br>1111 = (K = 7,  R = 7/8,  CCSDS)              |

|                     | CONTROL(4:1)                                                                     |

| Differential        | 0 = disabled                                                                     |

| Encoding            | 1 = enabled                                                                      |

|                     | CONTROL(5)                                                                       |

| Continuous / Block  | Determines whether the                                                           |

| mode                | SOF RESET mode should be                                                         |

| mode                | enabled for resetting the encoder at                                             |

|                     | the start of a block.                                                            |

|                     | 0 = continuous                                                                   |

|                     | 1 = block mode.                                                                  |

|                     | CONTROL(6)                                                                       |

| Output sample       | 00 = 1 bit serial                                                                |

| format              | 00 - 1 bit serial $01 = 2$ bit parallel (I/Q) for                                |

| 10111141            | connection to QPSK modulator.                                                    |

|                     | 10 = 3-bit parallel for connection to                                            |

|                     | 8-PSK modulator.                                                                 |

|                     | 11 = 4-bit parallel for connection to                                            |

|                     | 16-PSK modulator                                                                 |

|                     | This field is ignored when TCM                                                   |

|                     | mode is selected.                                                                |

|                     | CONTROL(9:8)                                                                     |

| Internal pattern    | 00 = test mode disabled                                                          |

| generation (test    | oo test mode disabled                                                            |

| mode)               | 01 = counting sequence:                                                          |

| *                   | When set, the baseband input is                                                  |

|                     | disabled and a periodic pattern is                                               |

|                     | internally generated at the encoder                                              |

|                     | input. The pattern consists of an 8-                                             |

|                     | bit counter, MSB transmitted first.                                              |

|                     | on counter, mod dunishinated hist.                                               |

|                     | 10 = PRBS-11. internal generation                                                |

|                     | of 2047-bit periodic pseudo-random                                               |

|                     | of 2017 of periodic pseudo fundom                                                |

<sup>1</sup> Not supported in decoder

|                                   | bit sequence as modulator input. (overrides external input bit stream). Useful in measuring BER performances in conjunction with the decoder BER tester.                  |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                   | The test pattern bit rate is automatically set by the external sink module (typically a modulator) as part of the flow control mechanism.                                 |

|                                   | CONTROL(11:10)                                                                                                                                                            |

| Decoder                           |                                                                                                                                                                           |

| Generator polynomials G           | Traditionally expressed as a K-bit octal number. For example CCSDS generator polynomials are G0: G(8 downto 0) <= O"171";                                                 |

|                                   | G1: G(17 downto 9) <= O"133";                                                                                                                                             |

| Number of parity                  | Gn: G(62:18) <= (others => '0')                                                                                                                                           |

| bits N_PARITY_BITS                | number of parity bits (i.e. generator polynomials).                                                                                                                       |

| N_I7RRITI_DITS                    | Valid range: 2 - 7                                                                                                                                                        |

|                                   | MUST be less than or equal to the hardware capabilities set by N_PARITY_BITS_MAX defined in the generic section                                                           |

| Constraint length                 | Valid values are 3,5,7,9                                                                                                                                                  |

| K                                 | Must be less than or equal to K_MAX                                                                                                                                       |

| Convolutional encoding rate R1/R2 | Valid values are 1/2, 1/3, 1/7, 2/3, 3/4, 5/6, 7/8                                                                                                                        |

| STANDARD                          | There are some minor variations among standards, such as different puncturing scheme or inversion  0 = Intelsat  1 = CCSDS  2 = DVB rate 1/2 only                         |

|                                   | others = yet TBD                                                                                                                                                          |

| DIFF_ENC_ON                       | input stream is differentially encoded (1) or not (0)                                                                                                                     |

| HIGH_SNR                          | It is sometimes helpful to adjust in-<br>lock/out-of-lock detection<br>thresholds to trade-off probability of<br>missed out of lock and probability<br>of false detection |

| SKIP1BIT_<br>PULSE                | Skip one encoded input bit for each 1 CLK-wide pulse                                                                                                                      |

|                                   | This feature is used to synchronize the input stream with the periodic encoding/puncturing pattern                                                                        |

#### Codes

Convolutional codes are defined by the generator polynomials Gx and puncturing pattern if any. Codes defined in various standards are listed below. 0 marks an erasure during puncturing.

#### K = 5

The generator polynomials for K=5 R=1/7 is  $G_0(x)=1+x+x^2+x^4$   $G_1(x)=1+x^2+x^3+x^4$   $G_2(x)=1+x^2+x^4$   $G_3(x)=1+x^2+x^3+x^4$   $G_4(x)=1+x+x^3+x^4$   $G_5(x)=1+x+x^2+x^4$

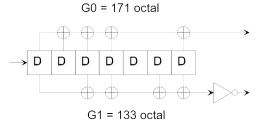

### K = 7 (CCSDS)

The generator polynomials for K=7 R =  $\frac{1}{2}$  are  $G_0(x)=1+x+x^2+x^3+x^6$   $G_1(x)=1+x^2+x^3+x^5+x^6$  171(octal) and 133(octal). The implementation is depicted below:

Basic CCSDS convolutional encoder

The basic encoder inverts the  $G_1$  output. When using puncturing, this inverter is removed.

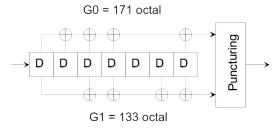

#### CCSDS convolutional encoder with puncturing

Rates other than ½ are implemented by puncturing the rate ½ encoded data stream. The puncturing pattern is as follows (1 denotes transmission, 0 blocking)

| CCSDS puncturing      |             |  |

|-----------------------|-------------|--|

| Constraint length     | K=7         |  |

| Generator Polynomials | G0 = o"171" |  |

|                       | G1 = o"133" |  |

| Puncturing pattern    | G0 1        |  |

| rate 1/2              | G1 1        |  |

| Puncturing pattern    | G0 10       |  |

| rate 2/3              | G1 11       |  |

| Puncturing pattern    | G0 101      |  |

| rate 3/4              | G1 110      |  |

| Puncturing pattern    | G0 10101    |  |

| rate 5/6              | G1 11010    |  |

| Puncturing pattern    | G0 1000101  |  |

| rate 7/8              | G1 1111010  |  |

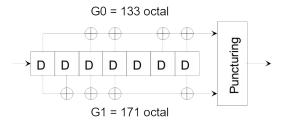

### K = 7 (Intelsat)

The generator polynomials for  $K = 7 R = \frac{1}{2}$  are  $G_0(x) = 1 + x^2 + x^3 + x^5 + x^6$

$$G_1(x) = 1 + x + x^2 + x^3 + x^6$$

133(octal) and 171(octal). The implementation is depicted below:

Rates other than ½ are implemented by puncturing the rate ½ encoded data stream. The puncturing pattern is as follows (1 denotes transmission, 0 blocking)

| olocking)             |             |               |  |

|-----------------------|-------------|---------------|--|

| Intelsat puncturing   |             |               |  |

| Constraint length     | K=7         |               |  |

| Generator Polynomials | G0 = o"133" |               |  |

|                       | G1 = o"171" |               |  |

| Puncturing pattern    | G0          | 1             |  |

| rate 1/2              | G1          | 1             |  |

| Puncturing pattern    | G0          | 1 1           |  |

| rate 2/3              | G1          | 1 0           |  |

| Puncturing pattern    | G0          | 1 1 0         |  |

| rate 3/4              | G1          | 1 0 1         |  |

| Puncturing pattern    | G0          | 1 1 0 1 0     |  |

| rate 5/6              | G1          | 10101         |  |

| Puncturing pattern    | G0          | 1111010       |  |

| rate 7/8              | G1          | 1 0 0 0 1 0 1 |  |

#### K = 9 R = 1/3

The generator polynomials for K = 9 R = 1/3 are  $G_0(x) = 1 + x^2 + x^3 + x^5 + x^6 + x^7 + x^8$ .  $G_1(x) = 1 + x + x^3 + x^4 + x^7 + x^8$ .  $G_2(x) = 1 + x + x^2 + x^5 + x^8$ .

### $K = 9 R = \frac{1}{2}, \frac{2}{3}$

The generator polynomials for K = 9 R = 1/2 are  $G_0(x) = 1 + x + x^2 + x^3 + x^5 + x^7 + x^8$ .  $G_1(x) = 1 + x^2 + x^3 + x^4 + x^8$ .

The rate 2/3 is implemented by puncturing the rate ½ encoded data stream. The puncturing pattern is as follows (1 denotes transmission, 0 blocking):

Rate

$$2/3$$

$G_0$  11  $G_1$  01

## Treillis Coded Modulation (TCM) Encoder<sup>1</sup>

As per Intelsat IESS-310 for rate 2/3 8-PSK.

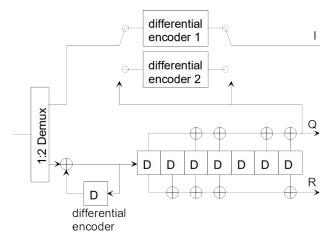

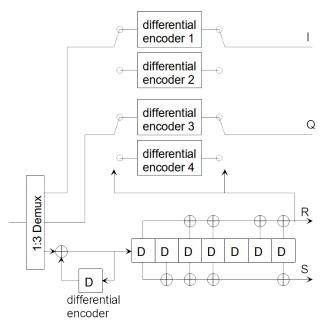

TCM encoder, rate 2/3 for 8-PSK

TCM encoder, rate 3/4 for 16-PSK

### $K = 6 (DVB)^2$

The generator polynomials for K = 6  $R = \frac{1}{2}$  are  $G_0(x) = 1 + x + x^2 + x^3 + x^6$   $G_1(x) = 1 + x^2 + x^3 + x^5 + x^6$  171(octal) and 133(octal).

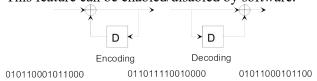

### **Differential Encoding**

Differential encoding can be used prior to FEC encoding as specified in Intelsat IESS-308/309. This feature can be enabled/disabled by software.

This mode compensates for any bit inversion occurring in the transmission channel (for example at a BPSK demodulator which cannot resolve the inherent 180deg phase ambiguity).

### **Differential Decoding**

Differential decoding can be used following FEC decoding as specified in Intelsat IESS-308/309. This feature can be enabled/disabled by software.

This mode compensates for any bit inversion occurring in the transmission channel (for example at a BPSK demodulator which cannot resolve the inherent 180deg phase ambiguity). This ambiguity resolution mechanism has a cost: the bit error rate is doubled.

#### I/Os

#### **CLK**: input

The synchronous clock. The user must provide a global clock (use BUFG). The CLK timing period must be constrained in the constraint file (.xdc) associated with the project.

#### **SYNC\_RESET**: input

Synchronous reset. The reset MUST be exercised at least once to initialize the internal variables.

#### **DATAIN(31:0)**:

32-bit input packing eight soft-quantized samples. Input samples are soft-quantized with 4-bits. Format is offset binary whereby 0000 represents a 'strong' 0, 1111 a strong '1', 0111 the weakest '0' and 1000 the weakest '1'.

When using hard-decision decoding, encoded bits are placed at location at indices 3+i\*4 (31,27,...7,3) in the vector. Other locations are ignored.

Packing order for the eight samples is from the most significant side to the least significant side of this array e.g. (DATAIN(31:28) is the first received soft-decision sample)

#### **DATAIN VALID:**

1 CLK-wide pulse indicating that DATAIN is valid.

#### **DATAIN READY:**

A flow-control signal indicating whether the decoder is ready to accept new DATAIN input samples.

There are two types of decoder outputs: 1-bit serial (DATAOUT1b / DATAOUT1b\_VALID) or 8-bit parallel (DATAOUT8b / DATAOUT8b\_VALID) Bit order in 8-bit parallel mode is MSb first.

<sup>2</sup> Not supported in encoder

### **Monitoring**

#### **Bit Error Rate Measurement**

The decoder estimates the bit error rate **BER(31:0)** on the encoded input bit stream by comparing the actual received bit stream with an estimate of the transmitted bit stream. This estimate is generated by re-encoding the nearly error-free decoded bit stream.

The algorithm is based on the proposition that the decoded bit stream is nearly error-free. If the decoded bit stream were error-free, then the reencoded bit stream would be the actual transmitted encoded bit stream before bit errors occur in the transmission channel.

The bit error rate is computed over a window of 1000 input bits. This measurement window length **BER\_WINDOW\_LENGTH** is a constant set in *VA.vhd*. The synchronization thresholds **BER\_THRESHOLD\_xx** are set on the basis of a 1000-bit window.

Read the **BER** when **BER VALID** is '1'.

### **Self Synchronization**

When the decoder detects that the bit error is greater than a set threshold, it attempts to resynchronize. Different thresholds are used for the various encoding rates. See the **BER THRESHOLD** xx constants in VA.vhd.

IN\_SYNC: out std\_logic;

OUT\_OF\_SYNC: out std\_logic;

1 CLK-wide pulses every BER\_WINDOW\_LENGTH

bits to indicate either synchronization (when BER is

below threshold) or lack of synchronization (BER above

threshold)

OUT\_OF\_SYNC pulse indicates that the input coding groups are not aligned with the transmitted coding groups, i.e. received bit in the G0 bin not actually generated by G0, etc. This information is typically used by external circuitry to realign the received encoded bit stream with the expected parity groups or puncturing pattern, or to correct for PSK demodulator phase ambiguities, etc.

**LOCK\_STATUS**: out std\_logic a continuous '1' when measured **BER** is below the set threshold. Toggling when unlocked

#### Standards

Support for the following standards: Intelsat IESS-308/309 Intelsat IESS-310 DVB ETS 300 421<sup>3</sup> DVB ETS 300 744<sup>3</sup> CCSDS 101.0-B-6

3 Not supported in encoder

### I/Os

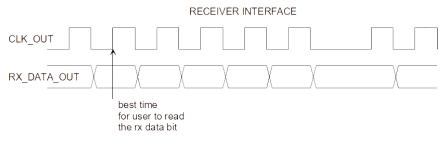

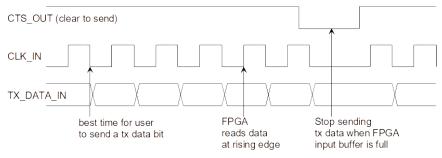

### 1-bit synchronous serial

#### TRANSMITTER INTERFACE

The user should always check the "Clear-To-Send" CTS\_OUT flag before sending additional data bits to the modulator.

1

### Software Licensing

The COM-1509SOFT is supplied under the following key licensing terms:

- 1. A nonexclusive, nontransferable license to use the VHDL source code internally, and

- 2. An unlimited, royalty-free, nonexclusive transferable license to make and use products incorporating the licensed materials, solely in bitstream format, on a worldwide basis.

The complete VHDL/IP Software License Agreement can be downloaded from http://www.comblock.com/download/softwarelicense.pdf

### **Configuration Management**

The current software revision is 005a 101725.

| Directory | Contents                                                                                                                                 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| /doc      | Specifications, user manual, implementation documents                                                                                    |

| /src      | .vhd source code,ngc constraint files, .pkg packages. One component per file.                                                            |

| /sim      | Test benches for VHDL simulation of Viterbi decoder (from input stimulus file), or back to back FEC codec, V35 scrambling, HDLC framing. |

| /matlab   | Matlab .m files to generate encoded input files with various Eb/N0 and to compute expected BER.                                          |

#### Project files:

Xilinx Vivado v2020 project file: /project 1/project 1vivado2020.xpr

More generally, a tcl file can help construct the complete project: /project\_1/project\_1vivado2020.tcl It includes all the constituent components.

### VHDL development environment

The VHDL software was developed using the following development environment:

Xilinx Vivado 2020 for synthesis, place and route and VHDL simulation

### **Device Utilization Summary**

The decoder implementation size depends essentially on three key user-defined parameters in the Viterbi decoder generic section, namely:

- Hard/Soft-decision decoding HARD SOFTN DECISION

- Maximum constraint length K\_MAX

(the actual constraint length K is dynamically configurable at run-time but cannot exceed the hardware capabilities defined by K\_MAX)

- Maximum number of parity bits

N\_PARITY\_BITS\_MAX

(the actual number of parity bits

N\_PARITY\_BITS is dynamically configurable at run-time but cannot exceed the hardware capabilities defined by

N\_PARITY\_BITS\_MAX

Device: Kintex ultrascale+ xcku5p-ffvd900-3-e

| Device. Ithirex ditrascure | Rekusp | 1114700 5 6 |

|----------------------------|--------|-------------|

| Viterbi decoder            |        |             |

| K=5 or 7                   |        |             |

| 2 parity bits              |        |             |

| NDEC = 1                   |        |             |

| 4-bit soft decision input  |        |             |

| traceback depth 84         |        |             |

| LUTs                       | 3526   | 1.6%        |

| Registers                  | 3235   | 0.8%        |

| Block RAM/FIFO 36Kb        | 1.5    | 0.3%        |

| DSP48                      | 0      | 0%          |

| GCLKs                      | 1      | 0.4%        |

| Viterbi decoder           |       |      |

|---------------------------|-------|------|

| K=5 or 7                  |       |      |

| 2 parity bits             |       |      |

| NDEC = 8 parallel         |       |      |

| 4-bit soft decision input |       |      |

| traceback depth 84        |       |      |

| LUTs                      | 20710 | 9.6% |

| Registers                 | 20197 | 4.7% |

| Block RAM/FIFO 36Kb       | 20.5  | 4.3% |

| DSP48                     | 0     | 0%   |

| GCLKs1                    |       | 0.4% |

| Encoder             |     |       |

|---------------------|-----|-------|

| LUTs                | 172 | 0.1%  |

| Registers           | 162 | 0.04% |

| Block RAM/FIFO 36Kb | 0   | 0%    |

| DSP48               | 0   | 0%    |

| GCLKs               | 1   | 0.4%  |

### Clock speed, bit rates

The entire design uses a single global clock CLK. Typical maximum clock frequencies for various FPGA families are listed below:

| Device family - speed grade | f <sub>CLK</sub> | Max<br>encoded/decoded<br>bit rate<br>1 decoder<br>2 parity bits |

|-----------------------------|------------------|------------------------------------------------------------------|

| AMD/Kintex ultrascale+ -3   | 423 MHz          | 423/211 Mbits/s                                                  |

| Xilinx Kintex 7 -2          | 344 MHz          | 344/172 Mbits/s                                                  |

| Xilinx Virtex-6 -2          | 272 MHz          | 272/136 Mbits/s                                                  |

| Design Sources (9)          |                  | /s                                                               |

- VITERBI\_DECODER(Behavioral) (Viterbi\_decoder

- > SERIAL\_DECODING.DATA\_SPLITTER\_001 : DAT/

- ∨ VA\_000 : VA(behavioral) (va.vhd) (71)

- > VA\_TBU2\_001: VA\_TBU2(Behavioral) (va\_tk

- ✓ BER\_MEASUREMENT\_001.BER3\_001 : BER3

- Inst\_BRAM\_DP2 : BRAM\_DP2(Behaviora

- > PC\_16\_001: PC\_16(BEHAVIOR) (PC\_16.)

- BMU\_00x[0].VA\_BMU2\_001 : VA\_BMU2(beh

- BMU\_00x[1].VA\_BMU2\_001 : VA\_BMU2(beh

- BMU\_00x[2].VA\_BMU2\_001 : VA\_BMU2(beh

- BMU\_00x[3].VA\_BMU2\_001 : VA\_BMU2(beh

- ACS\_00X[0].VA\_ACS2\_001 : VA\_ACS2(behave)

- ACS\_00X[1].VA\_ACS2\_001 : VA\_ACS2(behave)

- ACS\_00X[2].VA\_ACS2\_001 : VA\_ACS2(behave)

The maximum <u>decoded</u> bit rate is **f**<sub>CLK</sub> \***NDEC** / **N\_PARITY\_BITS**Where **NDEC** is the number of parallel decoders embodied in the design.

# VHDL components overview Viterbi decoder

VITERBI\_DECODER.vhd is the decoder top component in this hierarchical design. It's role is to segment the continuous input stream of encoded (hard or soft-quantized) bits into fixed-length blocks which can be processed by NDEC parallel decoders. The decoded bit stream is then reassembled into a seamless output stream. This component also adjusts the alignment of the input encoded bit stream with the coding and puncturing periodic pattern. Indeed, the follow-on Viterbi algorithm (VA.vhd) can only work properly if a parity bit encoded by generator polynomial Gx in the transmitter is decoded with the same generator polynomial at the receiver.

*DATA\_SPLITTER.vhd* implements the continuous input stream segmentation.

VA.vhd is the heart of the Viterbi algorithm which includes three key processes: The branch metric unit (VA\_BMU2.vhd), the Add-Compare-Select (VA\_ACS2.vhd) and the traceback unit (VA\_TBU2.vhd).

*VA\_BMU2.vhd* computes the local distance between received soft-quantized bits and the hypothesis being tested. Received bits marked with the erasures flag are ignored in the distance computation.

*VA\_TBU2.vhd* segments the stream of add-compare-select outputs into overlapping blocks of length 2\* **TB\_DEPTH**., long enough for the Viterbi algorithm to converge. The process is repeated every **TB\_DEPTH** bits. The **TB\_DEPTH** decoded bits are then read in the reverse order.

*BER3.vhd* estimates the coded input bit error rate by comparing it with the reconstructed encoded input (obtained by re-encoding the decoded sequence).

INFILE2SIM.vhd reads an input file. This component is used by the testbench to read a soft-quantized or hard-quantized encoded bit stream generated by the viterbi\_dec\_input\_genprbs11.m Matlab program for various Eb/No cases.

SIM2OUTFILE.vhd writes three 12-bit data variables to a tab delimited file which can be subsequently read by Matlab (load command) for plotting or analysis.

#### **Encoder**

- ENCODER\_ROOT(behavioral) (encoder\_ro

- ENCODER\_K5R7\_001 : ENCODER\_K5R7(k

- ENCODER\_K7R2\_001 : ENCODER\_K7R2(t

- ENCODER\_K9R3\_001 : ENCODER\_K9R3(k

- ENCODER\_K9R2\_001 : ENCODER\_K9R2(l:

- > TCM\_23\_001: TCM\_23(behavioral) (tcm\_

- TCM\_34\_001 : TCM\_34(behavioral) (tcm\_

### **Ancillary components**

#### VHDL simulation

Three VHDL testbenches in the /sim directory provide bit-accurate VHDL simulations:

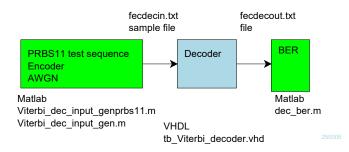

- TB\_VITERBI\_DECODER.vhd is the decoder testbench. Its input consists of soft-quantized noisy samples generated by the supplied Matlab programs viterbi\_dec\_input\_genprbs11.m or viterbi\_dec\_input\_gen.m

- *TB\_ENC\_DEC\_V35.vhd*: end-to-end simulation testbench encompassing convolutional encoder, Viterbi decoder, scrambling, descrambling, PRBS-11 test sequence generation and BER tester.

- TB\_ENC\_DEC\_V35\_HDLC.vhd: end-to-end simulation testbench encompassing convolutional encoder, Viterbi decoder, scrambling, descrambling, serial HDLC framing and deframing, PRBS-11 test sequence generation and BER tester.

Note: when moving the project folder location, be sure to change accordingly the FILENAME file paths in *TB\_VITERBI\_DECODER.vhd* INFILE2SIM and SIM2OUTFILE components generic section.

#### Matlab simulation

The viterbi\_dec\_input\_genprbs11.m

program

- 1. generates a pseudo-random PRBS11 test sequence.

- 2. This test sequence undergoes convolutional encoding.

- 3. Additive White Gaussian noise is then added according to the user-specified Eb/No.

- 4. The resulting sum is quantized with 4-bit soft-quantization and saved in the fecdecin.txt file for subsequent VHDL simulation using the TB VITERBI DECODER.vhd testbench.

The dec\_ber.m program reads a file of decoded data fecdeccout.txt generated by VHDL simulation and compare it with the original PRBS-11 test sequence. It counts the number of bit errors. [Note: it is redundant with the bit error rate tester BER2 within the VHDL testbenches]

#### Reference documents

[1]

### **Acronyms**

| Acronym | Definition                                         |

|---------|----------------------------------------------------|

| AWGN    | Additive White Gaussian Noise                      |

| BRAM    | Block RAM                                          |

| CCSDS   | Consultative Committee For Space Data<br>Systems   |

| BER     | Bit Error Rate                                     |

| BRAM    | Dual-port Block RAM                                |

| CCSDS   | Consultative Committee For Space Data<br>Systems   |

| FEC     | Forward Error Correction                           |

| FPGA    | Field Programmable Gate Array                      |

| HDLC    | High-Level Data Link Control (framing protocol)    |

| LSb     | Least Significant bit                              |

| LUT     | Lookup table (FPGA resource)                       |

| MSb     | Most Significant bit                               |

| PRBS-11 | Pseudo-Random Binary Sequence, 2047-<br>bit period |

| RX      | Receiver                                           |

| TX      | Transmitter                                        |

| VHDL    | VHSIC Hardware Description Language                |

### **ComBlock Ordering Information**

COM-1509SOFT CONVOLUTIONAL FEC ENCODER / VITERBI DECODER, VHDL SOURCE CODE / IP CORE

ECCN: EAR99

MSS • 845-N Quince Orchard Boulevard• Gaithersburg, Maryland 20878-1676 • U.S.A.

Telephone: (240) 631-1111 E-mail: sales@comblock.com