# COM-1518SOFT HIGH-SPEED DIRECT-SEQUENCE SPREAD-SPECTRUM DEMODULATOR VHDL SOURCE CODE / IP CORE

# Overview

The COM-1518SOFT is a digital direct-sequence spread-spectrum demodulator written in VHDL, for intermediate frequency or baseband input signals. It is designed to be embodied within a single low-cost FPGA such as the Xilinx Spartan-6 LX45.

The entire **VHDL source code** is provided.

#### Key features and performance:

- Direct-Sequence Spread-Spectrum (DSSS) demodulation

- Continuous mode operation (i.e. Burst mode is not supported)

- Maximum processing gain: 33 dB Spreading factor: 3 to 2047

- Code period can be (significantly) longer than symbol period: Maximal code period: 65535

- Maximum chip rate: 50% of processing clock frequency.

- o 78 Mchips/s Xilinx Spartan-6 -2

- 99 Mchips/s Xilinx Kintex-7 -2

- Parallel code search for fast code acquisition. The number of parallel search circuits instantiated within can be selected by the user prior to synthesis.

- False code lock prevention.

- Accurate time of arrival pulse generated once per code period (can be used for round-trip delay measurement for example).

- Built-in Bit Error Rate measurement.

# Target Hardware

The code is written in generic VHDL so that it can be ported to a variety of FPGAs. The code was developed and tested on a Xilinx Spartan-6 FPGA.

It can be easily ported to any Xilinx Kintex7, Virtex-6, Spartan-6, Virtex-5 FPGAs and other FPGAs.

## **Device Utilization**

Device: Xilinx Spartan-6 XC6SLX45-2

|             | 30 parallel code     | %           |

|-------------|----------------------|-------------|

|             | acquisition circuits | utilization |

| Flip Flops  | 9221                 | 16%         |

| LUTs        | 9414                 | 34%         |

| RAMB16BWERs | 5                    | 4%          |

| DSP48A1s    | 20                   | 34%         |

| GCLKs       | 1                    | 6%          |

| DCMs/PLLs   | 0                    | 0%          |

#### Device: Xilinx Kintex-7 XC7K70T-2

|             | 30 parallel code     | %           |

|-------------|----------------------|-------------|

|             | acquisition circuits | utilization |

| Flip Flops  | 8999                 | 10%         |

| LUTs        | 12195                | 29%         |

| RAMB16BWERs | 4                    | 2%          |

| DSP48E1s    | 20                   | 8%          |

| GCLKs       | 1                    | 6%          |

| DCMs/PLLs   | 0                    | 0%          |

## **Clock speed**

This design uses a single global clock, namely the ADC sampling clock. Typical maximum clock frequencies for various FPGA families are listed below:

| Device family       | <b>f</b> <sub>elk_rx</sub> | Max. chip rate |

|---------------------|----------------------------|----------------|

| Xilinx Kintex 7 -2  | 198 MHz                    | 99 Mchips/s    |

| Xilinx Virtex-6 -2  | 156 MHz                    | 78 Mchips/s    |

| Xilinx Spartan-6 –3 | 177 MHz                    | 88 Mchips/s    |

MSS • 845-N Quince Orchard Boulevard • Gaithersburg, Maryland 20878 • U.S.A. Telephone: (240) 631-1111 Facsimile: (240) 631-1676 www.ComBlock.com © MSS 2016 Issued 7/22/2016

## Interfaces

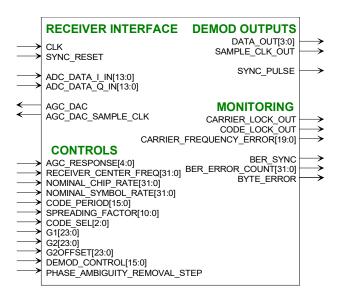

This component's interface comprises four distinct groups:

(a) the receiver interface typically connects to one (IF) or two (baseband) analog-to-digital converters (ADC). Use both I and Q inputs in the case of near-zero center frequency signal. Use the I input only in the case of IF input signal, while the Q input is set to zero.

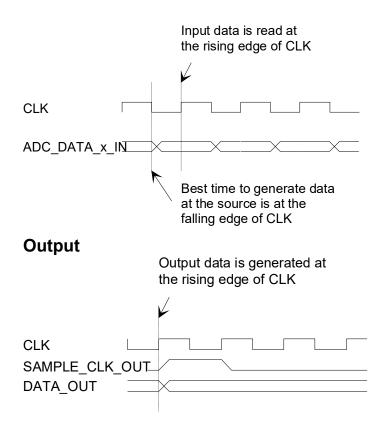

The entire component operates with a single clock CLK, typically the ADC sampling clock.

- (b) The demodulator output consists of 4-bit soft-quantized output. The most significant bit DATA\_OUT(3) represents the demodulated bit, while the remaining bits DATA\_OUT(2:0) rate its quality.

- (c) Controls can be changed at any time. In most cases, the component should be reset with a SYNC\_RESET pulse after a configuration change.

- (d) Monitoring

Input

# Monitoring and Control

# Configuration

The key configuration parameters are brought to the interface so that the user can change them dynamically at run-time. Other, more arcane, parameters are fixed at the time of VHDL synthesis.

### **Pre-synthesis configuration parameters**

The following configuration parameters are set as constants prior to synthesis

| constants prior to synthesis |                                                         |  |

|------------------------------|---------------------------------------------------------|--|

| Configuration                | Description                                             |  |

| parameters in                |                                                         |  |

| DSSS DEMOD2                  |                                                         |  |

| Number of parallel code      | NACQ                                                    |  |

| acquisition circuits         | The larger this number, the                             |  |

|                              | faster the code acquisition<br>time. The FPGA occupancy |  |

|                              | increases significantly as                              |  |

|                              | well.                                                   |  |

|                              |                                                         |  |

|                              | Limitation:                                             |  |

|                              | NACQ must be selected to                                |  |

|                              | be less than half the                                   |  |

|                              | spreading factor.                                       |  |

| Non-coherent Integration     | N_NCID                                                  |  |

| and Dump (I&D) period        | Number of successive                                    |  |

|                              | coherent I&D results                                    |  |

|                              | accumulated non-coherently                              |  |

|                              | (power-wise) to improve the                             |  |

|                              | SNR before making a dectection decision.                |  |

|                              |                                                         |  |

|                              | Trade-off acquisition speed                             |  |

|                              | versus acquisition SNR                                  |  |

|                              | threshold.                                              |  |

### **Run-time configuration parameters**

The user can set and modify the following controls at run-time. All controls are synchronous with the user-supplied global CLK. Most configuration changes should be followed by a SYNC\_RESET pulse.

The FPGA processing clock equals the ADC sampling clock:  $f_{clk_rx}$

| D (                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameters                                                   | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| AGC<br>response time                                         | Users can to optimize AGC response time<br>while avoiding instabilities (depends on<br>external factors such as gain signal<br>filtering at the RF front-end and chip<br>rate). The AGC_DAC gain control signal<br>is updated as follows<br>0 = every chip,<br>1 = every 2 input chips,<br>2 = every 4 input chips,<br>3 = every 8 input chips, etc<br>10 = every 1000 input chips.<br>Valid range 0 to 14.                                                                                                                                                 |

| Nominal<br>Center<br>frequency<br>( <b>f</b> <sub>IF</sub> ) | AGC_RESPONSE(4:0)<br>The nominal center frequency can be null<br>(in the case of a baseband input signal) or<br>non-zero in the case of an IF input signal.<br>If the IF center frequency is sufficiently<br>greater than the modulation bandwidth<br>(chip rate), the Q input can be ignored<br>and force to zero, thus saving an ADC.<br>This field can also be used for fine<br>frequency corrections, for example to<br>correct clock drifts.<br>32-bit signed integer (2's complement<br>representation) expressed as<br>$f_{IF}* 2^{32} / f_{elk_rx}$ |

| Chip rate<br>(fchip rate)                                    | RECEIVER CENTER FREQ(31:0)32-bit integer expressed as<br>fchip rate * 232 / fclk_rx.The maximum practical chip rate is fclk_rx /<br>2.Example for a 150 MHz fclk_rx:<br>60 Mchips/s: 0x666666666666666666666666666666666666                                                                                                                                                                                                                                                                                                                                 |

| Code period              | In ching                                                    |

|--------------------------|-------------------------------------------------------------|

| code period              | In chips.                                                   |

|                          | Valid range 3 – 65535                                       |

|                          |                                                             |

|                          | Can be less than the natural length of the                  |

|                          | selected code. In which case, the code is                   |

|                          | truncated.                                                  |

|                          | CODE_PERIOD(31:0)                                           |

| Code                     | 1 = Gold code                                               |

| selection                | 2 = Maximal length sequence                                 |

|                          | 3 = Barker code (lengths 11 or 13 only)                     |

|                          | 4 = GPS C/A codes (use G2 as GPS PRN number)                |

|                          | CODE SEL(2:0)                                               |

| Gold                     | 24-bit. Describes the taps in the linear                    |

| sequence /               | feedback shift register 1:                                  |

| Maximal                  | Bit 0 is the leftmost tap $(2^{\circ} \text{ in the})$      |

| Length                   | polynomial). The largest non-zero bit is the                |

| Sequence                 | polynomial order n. n determines the code                   |

| generator<br>polynomial  | period $2^n - 1$ .                                          |

| G1                       | Example:                                                    |

|                          | $G1 = 1 + x + x^4 + x^5 + x^6$ is represented as            |

|                          | 0x000039                                                    |

|                          | This field is used only if Gold code or                     |

|                          | Maximal length sequences are selected.                      |

| Gold code                |                                                             |

| generator                | 24-bit. Describes the taps in the linear                    |

| polynomial               | feedback shift register 2: Same format as G1 above.         |

| G2                       | This field is used only if Gold codes are                   |

|                          | selected.                                                   |

|                          | G2(23:0)                                                    |

| Gold code                | A Gold code is generated by adding two                      |

| G1/G2                    | maximal length sequences (as defined by                     |

| phase offset             | their generator polynomials G1 and G2). A                   |

|                          | set of orthogonal Gold codes can be                         |

|                          | created by changing the phase offset                        |

|                          | between the two maximal length                              |

|                          | sequences.                                                  |

| GPS                      | G2OFFSET(23:0)<br>GPS signals from different satellites are |

| satellite ID             | designated by a PRN signal number in the                    |

|                          | range $1 - 37$ .                                            |

|                          | This field is used only if GPS C/A codes                    |

|                          | are selected.                                               |

|                          | G2(5:0)                                                     |

| Symbol rate              | The symbol rate can be set independently                    |

| f <sub>symbol_rate</sub> | of the spreading code period as                             |

| • = ***                  | $\mathbf{f}_{symbol\_rate} * 2^{32} / \mathbf{f}_{clk\_tx}$ |

|                          |                                                             |

|                          | Limitation: the symbol rate must be higher                  |

|                          | than chip rate / 2047.                                      |

|                          | NOMINAL_SYMBOL_RATE(31:0)                                   |

|                          |                                                             |

| <u> </u>         |                                                                                 |

|------------------|---------------------------------------------------------------------------------|

| Spreading        | Approximate (i.e truncated) ratio of chip                                       |

| factor           | rate / symbol rate                                                              |

| (Processing      | Range: 3 – 2047                                                                 |

| gain)            | Note: to effectively achieve this                                               |

|                  | processing gain, the                                                            |

|                  | code period must be longer than one                                             |

|                  | symbol duration.                                                                |

|                  | SPREADING_FACTOR(10:0)                                                          |

| Spectrum         | Invert Q bit. (Inverts the modulated                                            |

| inversion        | spectrum only, not the subsequent                                               |

|                  | frequency translation)                                                          |

|                  | 0 = off                                                                         |

|                  | 1 = on                                                                          |

|                  |                                                                                 |

| DDCV /           | DEMOD CONTROL(0)                                                                |

| BPSK /           | Note: the modulation symbol transitions                                         |

| QPSK<br>decoding | are not necessarily aligned with the chip                                       |

| decounig         | transitions.                                                                    |

|                  |                                                                                 |

|                  | 0 = BPSK                                                                        |

|                  | 1 = QPSK                                                                        |

|                  | DEMOD_CONTROL(1)                                                                |

| Carrier          | 00 = nominal                                                                    |

| frequency        | 01 = 2x  loop gain                                                              |

| loop gain        | 10 = 4x  loop gain                                                              |

|                  | 11 = 8x  loop gain                                                              |

|                  | DEMOD CONTROL(3:2)                                                              |

| AFC enable       | The automatic frequency control circuit                                         |

| TH C chable      |                                                                                 |

|                  | extendeds the frequency acquisition over                                        |

|                  | +/- 10% of the symbol rate. When                                                |

|                  | disabled, the receiver only means of                                            |

|                  | carrier acquisition is the carrier frequency                                    |

|                  | tracking loop which is inherently limited                                       |

|                  | to approximately 1% of the symbol rate.                                         |

|                  | The AFC should only be active during                                            |

|                  | acquisition as it interferes with the Costas                                    |

|                  | Loop operation.                                                                 |

|                  | 00 = automatic AFC selection.                                                   |

|                  | 01 = force AFC disabled. Carrier tracking                                       |

|                  | loop only                                                                       |

|                  | 10 = force AFC enabled.                                                         |

|                  |                                                                                 |

|                  | 11 = reserved (test).                                                           |

| T . 1            | DEMOD_CONTROL(5:4)                                                              |

| Internal vs      | The code can act as a level sensor for an                                       |

| external         | external gain control actuator (for                                             |

| AGC              | example RF or IF receiver gain control) to                                      |

|                  | prevent saturation at the external A/D                                          |

|                  | converter. If so, configure as "external"                                       |

|                  | AGC.                                                                            |

|                  |                                                                                 |

|                  |                                                                                 |

|                  | Otherwise, an internal AGC will prevent                                         |

|                  | Otherwise, an internal AGC will prevent<br>saturation from occurring within the |

|                  | saturation from occurring within the                                            |

|                  |                                                                                 |

|                  | saturation from occurring within the FPGA.                                      |

|                  | saturation from occurring within the<br>FPGA.<br>0 = internal                   |

|                  | saturation from occurring within the FPGA.                                      |

| Phase<br>ambiguity<br>removal | The built-in PSK demodulator exhibits an<br>inherent phase ambiguity (modulo 180 deg<br>for BPSK, 90 deg for QPSK). Subsequent<br>circuits such as FEC decoders can detect<br>when the carrier tracking loop is locked onto<br>the wrong carrier phase. By generating a 1<br>CLK-wide pulse, this demodulator will jump<br>180 deg(BPSK) or 90 deg (QPSK) to the<br>next modulo.<br>PHASE_AMBIGUITY_REMOVAL_STEP |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

# Monitoring

| Carrier lock   | Carrier tracking loop status, based on the                                    |

|----------------|-------------------------------------------------------------------------------|

|                | measured RMS phase error. May wrongly                                         |

|                | indicate lock when no input signal and no                                     |

|                | input noise is present.                                                       |

|                | CARRIER_LOCK_OUT                                                              |

| Code lock      | CODE LOCK OUT                                                                 |

| Carrier        | Measured frequency error relative to the                                      |

| frequency      | nominal center frequency.                                                     |

| error          | 20-bit signed integer (2's complement                                         |

|                | representation) expressed as                                                  |

|                | <b>f</b> <sub>error</sub> * 2 <sup>20</sup> / <b>f</b> <sub>symbol rate</sub> |

|                | · -                                                                           |

|                | CARRIER_FREQUENCY_ERROR(19:0)                                                 |

| Bit error rate | Monitors the BER (number of bit errors                                        |

|                | over 1,000,000 received bits) when the                                        |

|                | modulator is sending a PRBS-11 test                                           |

|                | sequence. Valid only when BER analyzer                                        |

|                | is synchronized.                                                              |

|                |                                                                               |

|                | BER ERROR COUNT(31:0)                                                         |

| BER            | '1' when synchronized with the received                                       |

| analyzer       | PRBS-11 test sequence.                                                        |

| synchronized   | BER_SYNC                                                                      |

| Byte error     | One pulse for each byte error. Helpful in                                     |

|                | visualizing the bit error distribution                                        |

|                | (random? Burst?) with an oscilloscope.                                        |

|                | BYTE ERROR                                                                    |

# Block Diagram: Receiver1

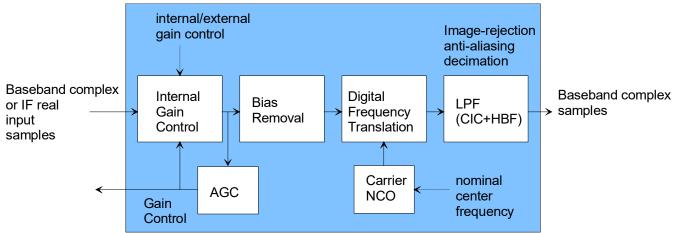

The ADC samples are first processed in the RECEIVER1.vhd component as illustrated above.

The AGC detects saturation or near saturation and adjust the gain control signal accordingly. This gain control is sent to either the internal or external gain control stage as per the configuration. The reaction time of the AGC loop is controlled by the AGC\_RESPONSE parameter.

After DC bias removal, the real (IF) or complex (near baseband) input samples are frequency translated to baseband, as per the RECEIVER\_CENTER\_FREQ parameter.

The resulting baseband signal undergoes up to two types of low-pass filtering (CIC decimation and Half-Band filter), depending on the modulation bandwidth (or more specifically, depending on the ratio of the sampling rate over the chip rate). These low-pass filters are used for (a) image-rejection, in the case of IF inputs, (b) antialiasing prior to decimation.

Resulting baseband complex samples are further sent to the DSSS\_DEMOD2.vhd component, as illustrated below.

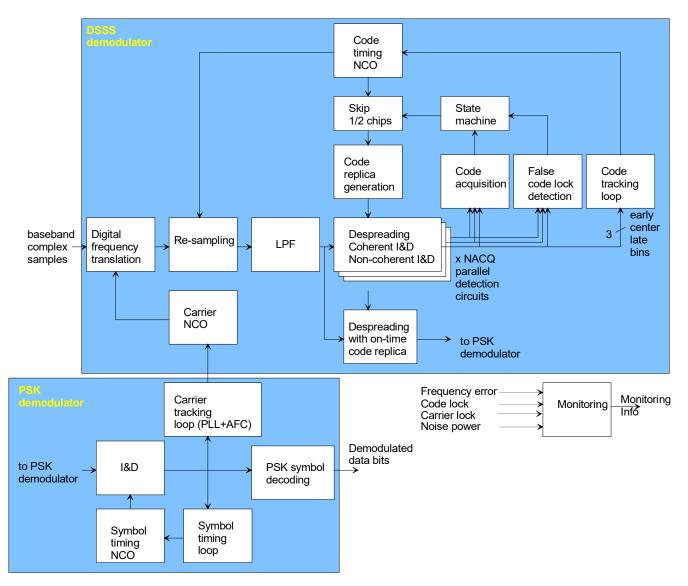

# Block Diagram: DSSS\_Demod2

The *DSSS\_DEMOD2.vhd* component conceptually comprises two distinct and mostly independent sections: (a) a spread-spectrum receiver (code acquisition and despreading) followed by (b) a regular PSK demodulator. Architecturally, this means that the PSK modulation could be replaced with other modulation types without much effort.

**NACQ** parallel code acquisition circuits are used for faster code acquisition. Each circuit consists of a code replica delay, despreading, coherent integration and dump (I&D) over a period of approximately half a symbol period, and non-coherent (i.e. power) I&D over a period of approximately N\_NCID/2 symbols.

During the code acquisition phase, these parallel circuits are used to search NACQ code epochs spaced ½ a chip apart.

During the code tracking phase, three parallel circuits are used to compare the early/on-time/late code epochs for code tracking. The remaining parallel circuits are used to search for false code lock (a consistently better code epoch).

## Software Licensing

The COM-1518SOFT is supplied under the following key licensing terms:

- 1. A nonexclusive, nontransferable license to use the VHDL source code internally, and

- 2. An unlimited, royalty-free, nonexclusive transferable license to make and use products incorporating the licensed materials, solely in bitstream format, on a worldwide basis.

The complete VHDL/IP Software License Agreement can be downloaded from http://www.comblock.com/download/softwarelicense.pdf

## **Configuration Management**

The current software revision is 1.

| Directory | Contents                                                           |

|-----------|--------------------------------------------------------------------|

| /doc      | Specifications, user manual, implementation documents              |

| /src      | .vhd source code, .ucf constraint files<br>One component per file. |

| /sim      | Test benches, Matlab .m signal generation                          |

| /bin      | n/a                                                                |

Key files:

Xilinx ISE project file: com-1518\_ISE141.xise

### VHDL development environment

The VHDL software was developed using the following development environment:

- (a) Xilinx ISE 14.1 with XST as synthesis tool

- (b) Xilinx ISE Isim as VHDL simulation tool

The entire project fits within a Xilinx Spartan-6 LX45. Therefore, the ISE project can be processed using the free Xilinx WebPack tooks.

## Xilinx-specific code

The VHDL source code was written in generic VHDL with few low-level Xilinx primitives. No Xilinx CORE is used. The Xilinx primitives are:

- RAMB16 Sx Sx

## VHDL software hierarchy

| <br>              |                                                                                                                                      |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| <br>com1518_      | ISE141                                                                                                                               |

| xc6slx45-3        |                                                                                                                                      |

|                   | M1518 - Behavioral (src\com1518.vhd)                                                                                                 |

|                   | EASURE_INTERVAL_001 - MEASURE_INTERVAL - Behavioral (src\MEAS                                                                        |

|                   | CEIVER1_001 - RECEIVER1 - Behavioral (src\receiver1.vhd)                                                                             |

|                   | INTERNAL_AGC_002 - MULT18X18SIGNED - BEHAVIOR (src\mult18)                                                                           |

| ·····             | INTERNAL_AGC_003 - MULT18X18SIGNED - BEHAVIOR (src\mult18)                                                                           |

| ···· H.           | POLAR3_001 - POLAR3 - Behavior (src\POLAR3.vhd)                                                                                      |

| ÷ 🖫               | Inst_AGC17 - AGC17 - behavioral (src\agc17.vhd)                                                                                      |

| ÷ 🖫               | BIAS_REMOVAL_001 - BIAS_REMOVAL - behavioral (src\bias_removi                                                                        |

| ÷ 🖌               | DIGITAL_DC_001 - DIGITAL_DC2 - DIGITAL_DC_ARCH (src\digital_dc                                                                       |

| ) <b>H</b>        | NC032_A - NC032 - behavioral (src/NC032.vhd)                                                                                         |

| <sup>40</sup>     | CIC_FILTER_001 - CIC - behavioral (src\CIC.vhd)                                                                                      |

| <sup>4</sup> 8    | CIC_FILTER_002 - CIC - behavioral (src\CIC.vhd)                                                                                      |

|                   | FIRHALFBAND3_11 - FIRHALFBAND3 - Behavioral (src\firhalfband3\                                                                       |

| <sup></sup>       | FIRHALFBAND3_Q1 - FIRHALFBAND3 - Behavioral (src\firhalfband3)                                                                       |

| ···· <sup>H</sup> | Inst_SIM2OUTFILE1 - SIM2OUTFILE - Behavioral (sim/sim2outfile.vh                                                                     |

| ···· ¥            | Inst_SIM2OUTFILE2 - SIM2OUTFILE - Behavioral (sim\sim2outfile.vh                                                                     |

|                   | Inst_SIM2OUTFILE2 - SIM2OUTFILE - Behavioral (sim/sim2outfile.vh                                                                     |

|                   | SS DEMOD2 001 - DSSS DEMOD2 - behavioral (src\DSSS DEMOD\ds                                                                          |

|                   |                                                                                                                                      |

| ÷ 1               | DIGITAL_DC2_001 - DIGITAL_DC2 - DIGITAL_DC_ARCH (src\digital_d                                                                       |

| ····· ¥           | NCO32_001 - NCO32 - behavioral (src\NCO32.vhd)                                                                                       |

| ÷ 🙀               |                                                                                                                                      |

| ···· 🖁            | FIRHALFBAND3_12 - FIRHALFBAND3 - Behavioral (src\firhalfband3)                                                                       |

| ···· 1            | FIRHALFBAND3_Q2 - FIRHALFBAND3 - Behavioral (src\firhalfband3                                                                        |

| ···· 📙            | CODEGEN2_001A - CODEGEN2 - behavior (src\DSSS_DEMOD\codeg                                                                            |

| ···· ¥.           | CODEGEN2_001B - CODEGEN2 - behavior (src\DSSS_DEMOD\codec<br>DESDECAD_ID_00;; DESDECAD_ID_behavior (src\DSSS_DEMOD\de                |

|                   | DESPREAD_ID_00x - DESPREAD_ID - behavior (src\DSSS_DEMOD\de                                                                          |

| Уна<br>Уна        | POWER_002 - MULT18X18SIGNED - BEHAVIOR (src\mult18x18signer                                                                          |

|                   | POWER_003 - MULT18X18SIGNED - BEHAVIOR (src\mult18x18signer                                                                          |

| на<br>Уна         | CODE_TRACKING2_002 - CODE_TRACKING2 - CODE_TRACKING_AF                                                                               |

|                   | ST_NCO32 - NCO32 - behavioral (src/NCO32.vhd)                                                                                        |

| ÷                 | SYMBOL_TRACKING_003 - SYMBOL_TIMING_LOOP5 - BEHAVIOR (s                                                                              |

| ÷- 🔛              | Inst_AGC17 - AGC17 - behavioral (src\agc17.vhd)                                                                                      |

| ···· ¥a           | DESPREAD_AGC_002 - MULT18X18SIGNED - BEHAVIOR (src\mult18)                                                                           |

|                   | DESPREAD_AGC_003 - MULT18X18SIGNED - BEHAVIOR (src\mult18)<br>CARRIER TRACK 003 - CARRIER TRACKING - behavioral (src\DSSS            |

| ÷ ¥.              |                                                                                                                                      |

| ···· H            | POLAR3_002 - POLAR3 - Behavior (src\POLAR3.vhd)                                                                                      |

| ····· Ha          | Inst_SIM2OUTFILE1 - SIM2OUTFILE - Behavioral (sim\sim2outfile.vh<br>Inst_SIM2OUTFILE2 - SIM2OUTFILE - Behavioral (sim\sim2outfile.vh |

| <sup>10</sup>     | Inst_SIM2OUTFILE3 - SIM2OUTFILE - Behavioral (sim/sim2outfile.vh                                                                     |

| <mark>1</mark>    | Inst_SIM2OUTFILE4 - SIM2OUTFILE - Behavioral (sim\sim2outfile.vh                                                                     |

|                   |                                                                                                                                      |

|                   | Inst_SIM2OUTFILE5 - SIM2OUTFILE - Behavioral (sim\sim2outfile.vh                                                                     |

|                   | _TO_P8_CONVERSION_003 - PX_TO_P8_CONVERSION - behavioral (s                                                                          |

|                   | R2_001 - BER2 - behavioral (src\BER2\ber2.vhd)                                                                                       |

| ⊕ <mark>"H</mark> |                                                                                                                                      |

|                   | SOF_TRACK8_001 - SOF_TRACK8 - BEHAVIOR (src\BER2\sof_track8;                                                                         |

| ⊞                 | Inst_PC_16 - PC_16 - BEHAVIOR (src\BER2\PC_16.vhd)                                                                                   |

| Ma 511            | /I2OUTFILE_001 - SIM2OUTFILE - Behavioral (sim\sim2outfile.vhd)                                                                      |

The code is stored with one, and only one, entity per file as shown above.

### **Comparison with Previous Version**

*Key Improvements with respect to COM-1418 Direct-Sequence Spead-Spectrum Demodulator*

- 2x faster: maximum chip rate is fclk/2

- Faster acquisition: parallel acquisition instead of sequential search.

- Symbol duration and alignment are independent of the spreading code period (2 independent tracking loops for code and symbol timing)

- Better performance through reduced dependencies between loops: code acquisition is less dependent on center frequency error.

- Independent AGCs before and after despreading.

- Phase ambiguity resolution under control of external FEC decoder.

## **ComBlock Ordering Information**

#### COM-1518SOFT DSSS DEMODULATOR

ECCN: 5E001.b.4

MSS • 845-N Quince Orchard Boulevard• Gaithersburg, Maryland 20878-1676 • U.S.A. Telephone: (240) 631-1111 Facsimile: (240) 631-1676 E-mail: sales@comblock.com