# Com Block

## COM-1801SOFT PSK/QAM/APSK Modem VHDL source code overview / IP core

## .Overview

The COM-1801SOFT PSK/QAM/APSK modem is a digital modulator and demodulator- written in generic VHDL.

The entire **VHDL source code** is deliverable. It is portable to a variety of FPGA targets.

#### Key features and performance:

- Flexible programmable features:

- Multiple modulation types with 1 to 5 bits per symbol: BPSK, QPSK, 8-PSK, 16-QAM, 16-APSK, 32-APSK.

- Symbol rate up to f<sub>clk</sub>/2 -1%, where f<sub>clk</sub> is the processing clock frequency. 32-bit precision.

- 4-bit soft-decision demodulator output for interface to FEC decoders.

- Framing structure for demodulator frequency acquisition and phase ambiguity removal.

- Performance:

- Near theoretical BER vs Eb/No: demod implementation loss < 0.5dB (QPSK)</li>

- ±50ppm symbol timing tracking

- Carrier frequency acquisition: ±10% of symbol rate at the threshold

- Acquisition threshold < -1dB Eb/No

- Provided with IP core:

- $\circ$  VHDL source code

- Matlab .m file for generating stimulus files for VHDL simulation of the demodulator and for end-to-end BER performance analysis at various signal to noise ratios

- VHDL testbenches (back-to-back modem or stimulus file input)

- PRBS11 test sequence generator, AWGN noise generator, BER tester

## .Configuration

#### **Pre-Synthesis configuration parameters**

The following constants are user-defined in the components generic section prior to synthesis. These parameters generally affect the size of the embodiment.

| Synthesis-time configuration parameters                                                           |                                                                                |  |  |

|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|

| <b>Modulator Parameters</b>                                                                       |                                                                                |  |  |

| <b>SYNC_LENGTH</b> Periodic sync marker<br>length, in number of<br>symbols. Typically 32 or<br>64 |                                                                                |  |  |

| Demodulator Parameters                                                                            |                                                                                |  |  |

| SYNC_LENGTH                                                                                       | Periodic sync marker<br>length, in number of<br>symbols. Typically 32 or<br>64 |  |  |

| BER_INST                                                                                          | '1' to instantiate a Bit<br>Error Rate Tester.                                 |  |  |

#### **Run-time configuration parameters**

The user can set and modify the following controls at run-time through the top level component interface:

| Modulator Parameters | Configuration                                                                                      |

|----------------------|----------------------------------------------------------------------------------------------------|

| SYMBOL_RATE(31:0)    | symbol rate expressed as fsymbol_rate/f <sub>clk</sub> * 2^32                                      |

| GAIN(16:0)           | output amplitude scaling factor. 16-bit unsigned                                                   |

| CENTER_FREQ(31:0)    | modulated signal center<br>frequency. Expressed as<br>fc/ f <sub>clk</sub> * 2^32                  |

| BURST_LENGTH(15:0)   | Payload field length, in number of symbols.                                                        |

|                      | Excludes the sync marker length                                                                    |

|                      | Constraints:<br>Total number of <u>bits</u> per<br>frame must be a multiple<br>of 8.               |

| CONTROL(15:0)        | bits 5:0 modulation type<br>0: BPSK<br>1: QPSK<br>8: 8PSK<br>16: 16QAM<br>24: 16APSK<br>32: 32APSK |

|                      | bit 6: spectrum inversion<br>bit 7: spectrum shaping                                               |

|                    | filter enable                                                                                                                                                      |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | bits 9:8 test mode: 00 no<br>test, 01 = PRBS11, 11 =<br>unmodulated carrier                                                                                        |

|                    | bits 10-12: SRRC rolloff factor                                                                                                                                    |

| SYNC_WORD(63/31:0) | Sync marker, inserted<br>periodically once per<br>frame. Current code<br>supports 32-bit and 64-bit<br>length sync markers.                                        |

| SYNC_EN            | Enable periodic sync<br>marker insertion.<br>Generally enabled as the<br>sync marker is essential in<br>recovering any phase<br>ambiguity at the receiving<br>end. |

| <b>Receiver Parameters</b>     | Configuration                                                                                                                                       |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| AGC_RESPONSE(4:0)              | Adjust the AGC response<br>time. approximately<br>log2(NSymbols).                                                                                   |

| RECEIVER_CENTER_<br>FREQ(31:0) | nominal (i.e. expected)<br>center frequency. 32-bit<br>signed (2's complement)<br>Expressed as<br>$f_c/f_{clk} * 2^{32}$                            |

| CIC_R(15:0)                    | CIC Decimation ratio.<br>The output sampling rate<br>is thus $f_{clk}/R$                                                                            |

|                                | 1 to bypass. 0 is illegal,<br>otherwise, nominal range<br>is 1 to 16384.                                                                            |

|                                | Usage: be careful not to<br>decimate too much as the<br>CIC decimation filter is<br>not very sharp and thus<br>can distort the modulated<br>signal. |

|                                | Rule of thumb: the CIC<br>filter output sampling rate<br>should be >= 4 samples<br>per symbol.                                                      |

| NOMINAL_SYMBOL_<br>RATE(31:0)  | $f_{symbol rate} / f_{elk} * 2^32 =$<br>nominal symbol rate                                                                                         |

| FRAME_LENGTH(15:0)             | Frame length, in symbols,<br>including payload + sync<br>marker.                                                                                    |

| DEMOD_CONTROL      | bits 5:0 modulation type<br>0: BPSK<br>1: QPSK<br>8: 8PSK                                                                  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------|

|                    | 16: 16QAM<br>24: 16APSK<br>32: 32APSK                                                                                      |

|                    | bit 6: spectrum inversion                                                                                                  |

|                    | bit 7: enable(1)/disable(0)<br>sync marker detection and<br>removal at output.<br>Generally enabled.                       |

|                    | bits 10-12: SRRC rolloff factor                                                                                            |

| SYNC_WORD(63/31:0) | Sync marker, inserted<br>periodically once per<br>frame. Current code<br>detects 32-bit and 64-bit<br>length sync markers. |

## .I/Os

## .General

#### CLK: input

Synchronous clock. The modulator and demodulator components typically use distinct synchronous clocks: DAC sampling clock for the modulator and ADC sampling clock for the demodulator.

The synchronous clocks must be global clocks (use BUFG). The timing periods must be constrained in the .xdc constraint file associated with the project.

#### SYNC\_RESET: input

Synchronous reset. The reset MUST be exercised at least once to initialize the internal variables. It must be exercised whenever a control parameter is changed.

When the modulator and demodulator use different synchronous clocks, they must use different synchronous resets.

#### .Modulator

|                                                  | COM1801 PSK_QAM_APSK                                                                                                                           | _MOD                                                             |                              |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------|

| ≁<br>→                                           | CLK<br>SYNC_RESET                                                                                                                              | DATA_I_OUT(17:0)<br>DATA_Q_OUT(17:0)                             | $\uparrow \uparrow \uparrow$ |

| $\rightarrow \rightarrow \rightarrow \leftarrow$ | TX_DATA(7:0)<br>TX_DATA_SAMPLE_CLK<br>TX_SOF INPUT<br>TX_CTS BITS                                                                              | DATA_OUT_VALID<br>TX_EN_OUT<br>MODULATED<br>BASEBAND<br>WAVEFORM | <b>* *</b>                   |

| <b> </b>                                         | SYMBOL_RATE(31:0)<br>GAIN(15:0)<br>TX_WINDOW<br>CENTER_FREQUENCY(31:0)<br>BURST_LENGTH(15:0)<br>CONTROL(15:0)<br>SYNC_WORD(63/31:0)<br>SYNC_EN | MONITORING<br>SATURATION<br>FREQ_REF                             | <b>* *</b>                   |

|                                                  |                                                                                                                                                |                                                                  |                              |

**TX\_DATA(7:0)**: Input data byte. The MSb is sent first.

#### TX\_DATA\_SAMPLE\_CLK: input.

1 CLK-wide pulse indicating that TX\_DATA is valid.

**TX\_SOF**: input Start Of Frame. 1 CLK-wide pulse. The SOF is aligned with **TX\_DATA\_SAMPLE\_CLK**.

#### TX\_CTS: output.

Clear-To-Send flow control. '1' indicates that the modulator is ready to accept another input byte. Thanks to an input elastic buffer, the data source is allowed to send a few more bytes after TX\_CTS goes low.

|                    | 1  |    |    |    |    |

|--------------------|----|----|----|----|----|

| SYNC_RESET         | 0  |    |    |    |    |

| TX_DATA[7:0]       | 55 | 9a | 5a | 8e | 55 |

| TX_DATA_SAMPLE_CLK | 1  |    |    |    |    |

| TX_SOF             | 1  |    |    |    |    |

| TX_CTS             | 0  |    |    |    |    |

Modulator input flow control example

**DATA\_I/Q\_OUT(17:0)**: Modulated baseband output samples (I = in-phase, Q = quadrature). Read when **DATA\_OUT\_VALID** = '1'. Format: 2's complement (signed)

**DATA\_OUT\_VALID**: generally all 1s.

**TX\_EN\_OUT**: goes low to turn off an external power amplifier when the modulator is not receiving any input data.

For more information about the input/output signals, please refer to the PSK\_QAM\_APSK\_MOD.vhd component declaration.

## .Receiver

| <b>→</b>                           | COM1801 PSK_QAM_APSK_DEMOD                                                                                                                                                                                                                                                                             |                                                 |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| <b>`</b>                           | SYNC_RESET DEMOD DATA                                                                                                                                                                                                                                                                                  |                                                 |

| $\downarrow \downarrow \downarrow$ | ADC_DATA_LIN(15:0) INPUT COMPLEX<br>ADC_DATA_Q_IN(15:0) SAMPLES<br>ADC_SAMPLE_CLK_IN SAMPLE_CLK_OUT<br>SOF OUT                                                                                                                                                                                         | $\rightarrow$ $\rightarrow$ $\rightarrow$       |

| <b>+ +</b>                         | AGC_DAC(11:0) AGC DAC EOF_OUT<br>AGC_DAC_SAMPLE_CLK                                                                                                                                                                                                                                                    | <b>→</b>                                        |

| * * * * * * *                      | AGC_RESPONSE(4:0) SOF_LOCK_OUT<br>RECEIVER_CENTER_FREQ(31:0) CARRIER_LOCK_OUT<br>CIC_R(15:0) CARRIER_FREQUENCY_ERROR<br>NOMINAL_SYMBOL_RATE(31:0) RX_SIGNAL_AMPLITUDE<br>FRAME_LENGTH(15:0) SNR<br>DEMOD_CONTROL(15:0) BER_SYNC<br>SYNC_WORD(63/31:0) BER_BYTE_ERROR<br>CONTROLS BER_ERROR_COUNT(31:0) | <b>&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;</b> |

|                                    | 220007                                                                                                                                                                                                                                                                                                 |                                                 |

**ADC\_DATA\_I/Q\_IN(15:0)**: input samples from one or two external ADCs. (one in the case of IF undersampling, two for near-zero frequency complex inputs). If the ADCs have fewer than 16bit precision, align the most significant bit with ADC\_DATA\_IN(15). Format: 2's complement (signed).

**ADC\_SAMPLE\_CLK\_IN**: valid signal for the **ADC\_DATA\_I/Q\_IN** input samples. Generally a solid '1'.

AGC\_DAC(11:0): output to an external DAC to control an external AGC. Read when AGC\_DAC\_SAMPLE\_CLK is '1'

**DATA\_OUT(3:0)**: soft-decision output. The demodulated bit is bit 3. The three lower bits indicate the level of confidence: "0000" for a solid '0', "1111" for a solid '1', "1000" for a '1' barely above the thresold.

**SAMPLE\_CLK\_OUT**: valid signal for the **DATA\_OUT** output.

**SOF\_OUT/EOF\_OUT**: 1 clock-wide pulses marking the Start/End Of Frames. Aligned with the first/last **SAMPLE\_CLK\_OUT** in a frame.

For more information about the input/output signals, please refer to the PSK\_QAM\_APSK\_DEMOD.vhd component declaration.

## .Operation

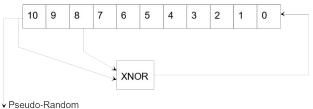

## .PRBS-11 Pseudo-Random Bit Stream

In order to perform bit error rate measurements at the receiver, a pseudo-random binary sequence can be inserted at the transmitter input (thus replacing any user data). BER measurement is made by counting actual errors in the received bit stream. The received bit stream is compared with a locally generated replica of the reference PRBS-11 sequence.

The reference sequence is a periodic 2047-bit long maximum length sequence generated by a 11-tap linear feedback shift register:

Sequence

## .Format Conversion

Serial to parallel conversion occurs at the interface between the modem and the application. The general rule is that the first received bit is placed at the MSb position in the byte.

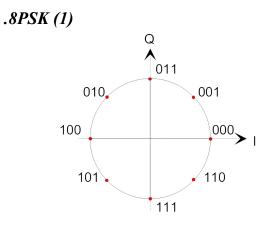

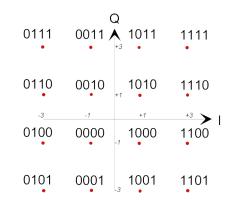

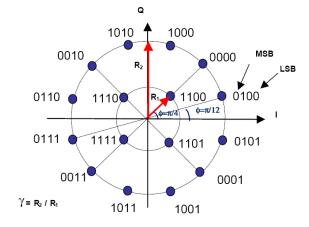

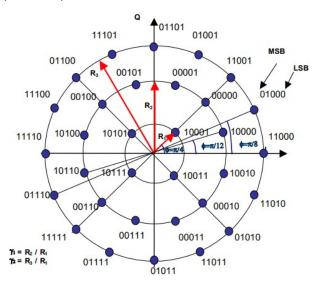

## .Constellation: Symbol Mapping

The packing of serial data stream into symbols is done with the Most Significant bit first.

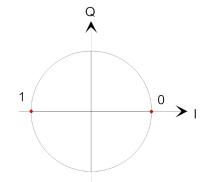

#### .BPSK

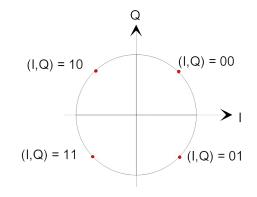

#### .QPSK

Gray encoding.

.16QAM

#### .16APSK

$\gamma = R2 / R1 = 2.85$ , best for code rate 3/4

#### .32APSK

$\gamma 1 = 2.84, \gamma 2 = 5.27$ , best for code rate 3/4

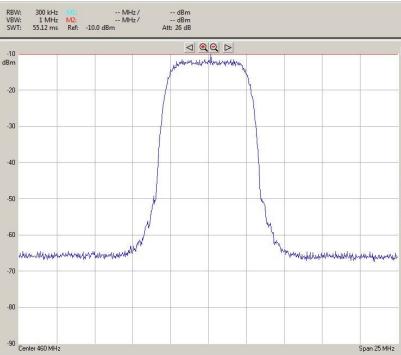

## .Channel Filter Response

The same square-root raised cosine (SRRC) filter type is used at the modulator for spectral shaping and at the receiver for noise rejection. This filter is used for all modulations types. It is applied to both In-phase and Quadrature signals at baseband. The filters vary slightly by their 'rolloff factor'. In order to minimize intersymbol interferences, the same rolloff factor should be used at both the modulator and demodulator. To this effect, users can select one of several rolloff factors: 20%, 25%, 35%.

#### .Framing

32 or 64-bit sync markers can be inserted periodically at the modulator. The purpose is three-fold:

- delineate frames and convey frame boundary information from modulator input to demodulator output.

- estimate input signal frequency error at the demodulator

- remove inherent phase ambiguities at the demodulator.

Enabling sync markers is required for all higher order modulations

Example of sync markers: 32-bit: 0x5A0FBE66, 0x1ACFFC1D 64-bit: 0x034776C7272895B0

The sync marker is user-programmable.

Sync markers are modulated as BPSK, irrespective of the selected modulation scheme for the payload field.

## .Performance

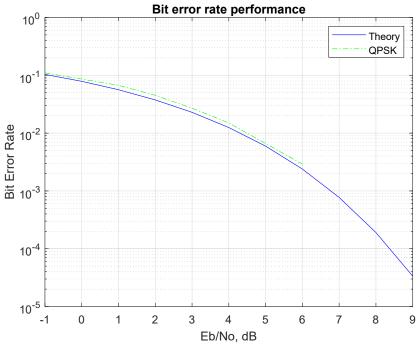

## .BER vs Eb/No

The plot below shows near-theoretical performance for the demodulator without error correction.

Test condition: +0ppm symbol timing error, 0 Hz frequency error

QPSK 10MSymbols/s, root raised cosine filter 20% rolloff

## .Latency

The latency between received signal and demodulated bit output is approximately 20 bits.

## .Software Licensing

This software is supplied under the following key licensing terms:

- 1. A nonexclusive, nontransferable license to use the VHDL source code internally, and

- 2. An unlimited, royalty-free, nonexclusive transferable license to make and use products incorporating the licensed materials, solely in bit stream format, on a worldwide basis.

The complete VHDL/IP Software License Agreement can be downloaded from http://www.comblock.com/download/softwarelicense.pdf

## .Portability

The VHDL source code is written in generic VHDL and thus can be ported FPGAs from various vendors.

## .Configuration Management

The current software revision is 041022.

| Directory | Contents                                                                                                                                                |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| /doc      | Specifications, user manual, implementation documents                                                                                                   |

| /src      | .vhd source code,.pkg packages, .xdc<br>constraint files (Xilinx)<br>One component per file.                                                            |

| /sim      | VHDL test benches                                                                                                                                       |

| /matlab   | Matlab .m file for generating stimulus files<br>for VHDL simulation and for end-to-end<br>BER performance analysis at various signal<br>to noise ratios |

| /bin      | .bit configuration files (for use with<br>ComBlock COM-1800 FPGA development<br>platform)                                                               |

Project files:

Xilinx Vivado v2020.2 project file: project\_1V2020 modem only.xpr

## .VHDL development environment

The VHDL software was developed using the following development environment: Xilinx Vivado 2020.2 for synthesis, place and route and VHDL simulation

The entire project fits within a Xilinx Artix7-100T. Therefore, the ISE project can be processed using the free Xilinx WebPack tools.

## **.Device Utilization Summary**

The modulator size is fixed (not parameterized). Device: Xilinx Artix7-100T

| Resource | Estimation | Available | Utilization |

|----------|------------|-----------|-------------|

| LUT      | 3481       | 63400     | 5.49        |

| LUTRAM   | 76         | 19000     | 0.40        |

| FF       | 4978       | 126800    | 3.93        |

| BRAM     | 15.50      | 135       | 11.48       |

| DSP      | 32         | 240       | 13.33       |

| Ю        | 185        | 285       | 64.91       |

| BUFG     | 1          | 32        | 3.13        |

The receiver size is fixed (not parameterized).

| Resource | Estimation | Available | Utilization |

|----------|------------|-----------|-------------|

| LUT      | 9606       | 63400     | 15.15       |

| LUTRAM   | 81         | 19000     | 0.43        |

| FF       | 9070       | 126800    | 7.15        |

| BRAM     | 1.50       | 135       | 1.11        |

| DSP      | 51         | 240       | 21.25       |

## .Clock frequency

The modulator and demodulator components each use a single global clock CLK.

Typical maximum clock frequencies for various FPGA families are listed below:

| Device family                                       | Modulator | Demodulator |

|-----------------------------------------------------|-----------|-------------|

| Xilinx Artix 7 -1 speed<br>grade                    | 160 MHz   | 160 MHz     |

| Xilinx Kintex<br>ultrascale plus, -1<br>speed grade | 288 MHz   | 280 MHz     |

## .Ready-to-use Hardware

The COM-1801SOFT was developed on, and therefore ready to use on the following commercial off-the-shelf hardware platform:

#### FPGA development platform

<u>COM-1800</u> FPGA (XC7A100T) + ARM + DDR3 SODIMM socket + GbE LAN development platform

## .VHDL components overview .Modulator top level

#### - PSK\_QAM\_APSK\_MOD\_001 : PSK\_QAM\_APSK\_MOD(

- Inst\_LFSR11P : LFSR11P(behavior) (Ifsr11p.vhd) (1)

- BURST\_TX2\_001 : BURST\_TX2(Behavioral) (burst\_tx2.v

- MODULATIONX4PROM\_001 : MODULATIONX4PROM

- FIR\_RRC1\_001 : FIR\_RRC1(Behavioral) (fir\_rrc1.vhd)

- FIR\_RRC1\_002 : FIR\_RRC1(Behavioral) (fir\_rrc1.vhd)

- FIRHALFBAND3\_I1 : FIRHALFBAND3(Behavioral) (firh.

- FIRHALFBAND3\_Q1 : FIRHALFBAND3(Behavioral) (firl

- FIRHALFBAND3\_I2 : FIRHALFBAND3(Behavioral) (firh.

- FIRHALFBAND3\_Q2 : FIRHALFBAND3(Behavioral) (firl

- FIRHALFBAND3\_I3 : FIRHALFBAND3(Behavioral) (firh.

- FIRHALFBAND3\_Q3 : FIRHALFBAND3(Behavioral) (firl

- DELAY4\_001 : DELAY4(behavioral) (delay4.vhd) (1)

- RESAMPLING6\_001i : RESAMPLING6(behavioral) (resa

- RESAMPLING6\_001q : RESAMPLING6(behavioral) (res

- DIGITAL\_DC3\_001 : DIGITAL\_DC3(DIGITAL\_DC\_ARCH)

- NCO32X\_001 : NCO32X(behavioral) (NCO32X.vhd)

- GAIN\_001 : MULT18X18SIGNED(BEHAVIOR) (mult18x

- GAIN\_002 : MULT18X18SIGNED(BEHAVIOR) (mult18x

*PSK\_QAM\_APSK.vhd* generates complex baseband (I/Q) sampled waveform from byte-size input data.

*BURST\_TX2.vhd* stores input data in an elastic input buffer, then packs input bits into symbols (1,2,3,4,5 bits/symbol) at the specified symbol rate. Ia also inserts periodic sync markers when enabled. It also stops the transmitter when the input elastic buffer is empty.

*MODULATIONX4PROM.vhd* is a ROM storing the complex constellation points for each modulation type.

*FIRRRC1.vhd* implements a square root raised cosine FIR filter using classic multipliers and stored FIR filter coefficients. Currently supporting three sets of coefficients for 20%, 25% and 35% rollof factor. Implemented as a 21-tap FIR filter.

*FIRHALFBAND3.vhd* are half-band interpolation filters used to double the sampling rate. Implemented as a 20-tap FIR filter.

*RESAMPLING6.vhd* interpolates the modulated signal up to the DAC sampling rate. Implemented as a Farrow structure for parabolic interpolation (alpha = 0.5)

*DIGITAL\_DC3.vhd* translates the modulated signal to a non-zero frequency. The 32-bit precision of the NCO frequency setting provides the user with a fine control over the output signal center frequency.

*SIGNED\_SIN\_COS\_TBL3.vhd* stores sine and cosine functions in ROM. It is used to convert phase to complex I/Q baseband output samples.

*COM1801\_TOP.vhd*: is mostly a use example when the modem is implemented on a ComBlock COM-1800 FPGA development platform. Please note that this top component can't be simulated as it makes many references to other components outside the scope of the modem proper (TCP stack, turbo codec, etc)

#### .Receiver top level

The receiver is comprised of two high-level components:

- PSK\_QAM\_APSK\_DEMOD\_001 : PSK\_QAM\_APSK\_DEMOD(B)

- > RECEIVER1\_001 : RECEIVER1B(Behavioral) (receiver1b.vhd) (

- > PSK\_QAM\_APSK\_DEMOD2\_001 : PSK\_QAM\_APSK\_DEMOD2(

- S1\_TO\_P8\_CONVERSION\_001 : S1\_TO\_P8\_CONVERSION(Beh)

- > BER\_GEN.BER2\_001 : BER2(behavioral) (ber2.vhd) (4)

*RECEIVER1B.vhd* performs non modulationspecific tasks such as AGC, DC bias removal, frequency translation to baseband, anti-aliasing filtering and decimation.

- PSK\_QAM\_APSK\_DEMOD\_001 : PSK\_QAM\_APSK\_DEMOD(Behaviora

- RECEIVER1\_001 : RECEIVER1B(Behavioral) (receiver1b.vhd) (9)

- Inst\_AGC17 : AGC17(behavioral) (agc17.vhd) (1)

- > AGC21\_001 : AGC21(behavioral) (agc21.vhd) (4)

- BIAS\_REMOVAL\_001 : BIAS\_REMOVAL(behavioral) (bias\_removal

DIGITAL\_DC\_001 : DIGITAL\_DC3(DIGITAL\_DC\_ARCH) (digital\_dc3

- CIC\_FILTER\_001 : CIC(behavioral) (CIC.vhd)

- CIC\_FILTER\_002 : CIC(behavioral) (CIC.vhd)

- > AGC21\_002 : AGC21(behavioral) (agc21.vhd) (4)

- FIRHALFBAND3\_I1 : FIRHALFBAND3(Behavioral) (firhalfband3.vh

- FIRHALFBAND3 Q1 : FIRHALFBAND3(Behavioral) (firhalfband3.v

*PSK\_QAM\_APSK\_DEMOD2.vhd* performs the demodulation, including carrier tracking (for coherent demodulation), symbol timing tracking, AGC, channel filtering and sync marker detection.

PSK\_QAM\_APSK\_DEMOD2\_001 : PSK\_QAM\_APSK\_DEMOD2(behaviora

- OIGITAL\_DC3\_001 : DIGITAL\_DC3(DIGITAL\_DC\_ARCH) (digital\_dc3

- FREQ\_SCAN\_002 : FREQ\_SCAN(behavioral) (freq\_scan.vhd)

- RESAMPLING\_002 : RESAMPLING2(behavioral) (resampling2.vhd)

- HALFBANDDECIMATIONFILT\_001 : HALFBANDDECIMATIONFILT(I

- HALFBANDDECIMATIONFILT\_002 : HALFBANDDECIMATIONFILT()

- FIR\_RRC1\_001 : FIR\_RRC1(Behavioral) (fir\_rrc1.vhd)

- FIR\_RRC1\_002 : FIR\_RRC1(Behavioral) (fir\_rrc1.vhd)

- AGC18\_001 : AGC18(behavioral) (agc18.vhd) (4)

- FRAME\_SYNC\_001 : FRAME\_SYNC(BEHAVIOR) (frame\_sync.vhd) (1

- → FAST\_FREQUENCY\_DETECTION\_001 : FAST\_FREQUENCY\_DETECTIC

- DIGITAL\_DC3\_002a : DIGITAL\_DC3(DIGITAL\_DC\_ARCH) (digital\_dc

- SYMBOL\_TRACKING\_003 : SYMBOL\_TIMING\_LOOP61(BEHAVIOR)

- SYNC\_DET\_EN\_001.MF001I : MATCHED\_FILTERNx1(Behavioral) (m

- SYNC\_DET\_EN\_001.MF001Q : MATCHED\_FILTERNx1(Behavioral) (r

- SYNC\_DET\_EN\_001.SOF\_TRACK2\_001 : SOF\_TRACK2(BEHAVIOR) (5

- SYNC\_DET\_EN\_001.POLAR3\_001 : POLAR3(Behavior) (POLAR3.vhd

- MONITORING\_001.POLAR3\_002 : POLAR3(Behavior) (POLAR3.vhd)

- SYMBOL\_DECODING2\_001 : SYMBOL\_DECODING2(BEHAVIOR) (s)

- CARRIER\_TRACK2\_003 : CARRIER\_TRACKING2(behavioral) (carrier

- SNR\_001 : SIGNAL\_NOISE\_RATIO(BEHAVIOR) (snr.vhd)

Note: several components are included for special custom applications but <u>not used</u> in the baseline code:

FREQUENCY\_SCAN.vhd, FAST\_FREQUENCY\_DETECTION.vhd,

FRAME\_SYNC.vhd performs the initial frame synchronization detection: it detects the periodic sync marker and estimates the frequency error. Designed to acquire a maximum center frequency error of +/- 10% of the symbol rate at the worst case Eb/No of -1 dB when configured for a 64-bit sync marker.

## .Ancillary components

*LFSR11P.vhd* is a pseudo-random sequence generator used for test purposes. It generates a PRBS11 test sequence commonly used for bit error rate testing at the receiving end of a transmission channel.

*BER2.vhd* is a bit error rate tester expecting to receive a PRBS11 test sequence. It synchronizes with the received bit stream and count errors over a 80,000 bit window.

BER2\_001 - BER2 - behavioral (src\BER2\ber2\br/strong)

MATCHED\_FILTER4x8\_001 - MATCHED\_FILTER4x8 - behavioral (src\BER2\matched\_filter4x8.vhd)

SOF\_TRACK8\_001 - SOF\_TRACK8 - BEHAVIOR (src\BER2\sof\_track8.vhd)

Inst\_PC\_16 - PC\_16 - BEHAVIOR (src\BER2\PC\_16.vhd)

*AWGN.vhd* generates a precise Additive White Gaussian Noise. The noise bandwidth is 2\*symbol rate.

*INFILE2SIM.vhd* reads an input file. This component is used by the testbench to read a modulated samples file generated by the siggen\_psk\_qam\_apsk.m Matlab program for various Eb/No and frequency offset cases.

*SIM2OUTFILE.vhd* writes three 12-bit data variables to a tab delimited file which can be subsequently read by Matlab (load command) for plotting or analysis.

*BRAM\_DP2.vhd* is a generic dual-port memory, used as input and output elastic buffers. Memory is inferred (no Xilinx primitive is used).

## .VHDL simulation

VHDL testbenches are located in the /sim directory.

The tbPSK\_QAM\_APSK\_modem.vhd connects the modulator and demodulator back to back. Endto-end BER tests can be performed as the modulator includes a built-in pseudo-random sequence generator and the receiver includes a built-in Bit Error Rate Tester.

The tbPSK\_QAM\_APSK\_demod.vhd testbench reads a tab-delimited stimulus files of modulated I/Q baseband complex input samples. The sampled waveform input.txt can be generated by the matlab program siggen\_psk\_qam\_apsk.m The testbench demodulates the signal and measures the resulting BER.

## .Matlab simulation

Matlab programs are located in the /matlab directory.

The siggen\_psk\_qam\_apsk.m program generates a stimulus file sim/input.txt for use as input to the demodulator VHDL simulation (tbPSK\_QAM\_APSK\_demod.vhd). The stimulus file includes a continuous stream of pseudo-random (PRBS11) data bits, PSK/QAM/APSK modulation, sync marker insertion, additive white Gaussian noise, channel filtering, frequency translation and quantization.

Care must be taken to match the modulator configuration in siggen\_psk\_qam\_apsk.m and the demodulator configuration in tbPSK\_QAM\_APSK\_demod.vhd.

This setup allows end-to-end BER testing, as the demodulator PSK\_QAM\_APSK\_DEMOD.vhd includes a built-in bit error rate tester.

## .Acronyms

| Acronym | Definition                                         |

|---------|----------------------------------------------------|

| ADC     | Analog to Digital Converter                        |

| AGC     | Automatic Gain Control (loop)                      |

| APSK    | Amplitude and Phase-Shift Keying modulation        |

| AWGN    | Additive White Gaussian Noise                      |

| BRAM    | Dual-port Block RAM                                |

| BER     | Bit Error Rate                                     |

| CCSDS   | Consultative Committee for Space Data<br>Systems   |

| CIC     | Cascaded Integrator Comb filter                    |

| DAC     | Digital to Analog Converter                        |

| DVB     | Digital Video Broadcast                            |

| FIR     | Finite Impulse Response filter                     |

| FPGA    | Field Programmable Gate Arrays                     |

| LSb     | Least Significant bit                              |

| LSB     | Least Significant Byte                             |

| M&C     | Monitoring and Control                             |

| MSb     | Most Significant bit                               |

| MSB     | Most Significant Byte                              |

| NCO     | Numerically Controlled Oscillator                  |

| N/A     | Not Applicable                                     |

| PSK     | Phase-Shift Keying modulation                      |

| PRBS-11 | Pseudo-Random Binary Sequence, 2047-<br>bit period |

| QAM     | Quadrature Amplitude Modulation                    |

| ROM     | Read-Only Memory                                   |

| SCPC    | Single Channel Per Carrier                         |

| SRRC    | Square Root Raised Cosine filter                   |

## .ComBlock Ordering Information

COM-1801SOFT PSK/QAM/APSK Modem, VHDL source code / IP core

## .Contact Information

MSS • 845-N Quince Orchard Boulevard • Gaithersburg, Maryland 20878-1676 • U.S.A. Telephone: (240) 631-1111 E-mail: info@comblock.com