# COM-1806 WIDEBAND SIGNAL CAPTURE & PLAYBACK 1GB

# Key Features

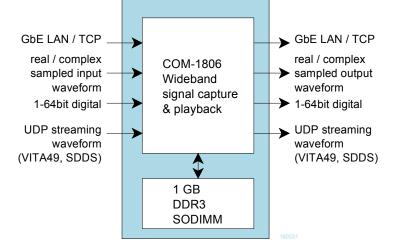

- Combines the functions of high-speed data acquisition and wideband arbitrary waveform generator into a small 3"x3" module.

- Stores 1GBytes of binary data in DDR3 SDRAM.

- Upload the following high-speed inputs:

- File transfer from a PC over GbE<sup>1</sup> LAN TCP or UDP

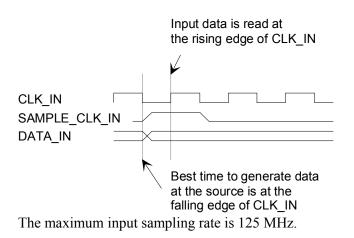

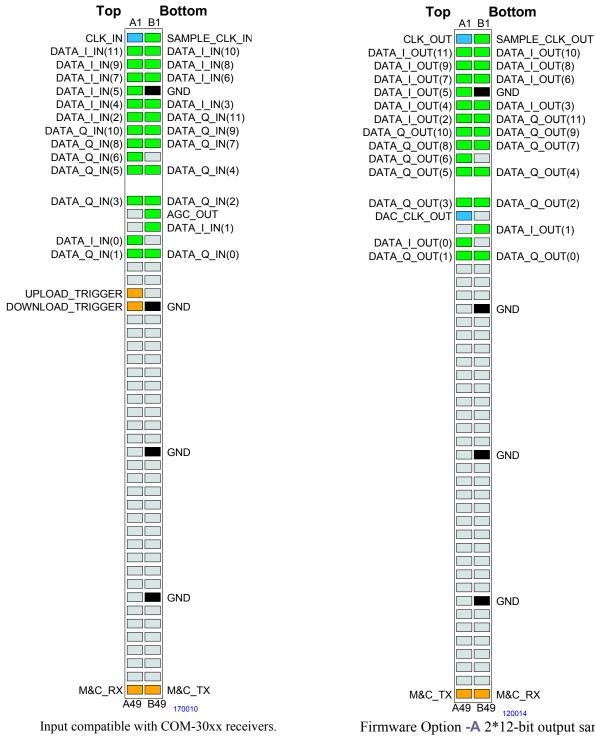

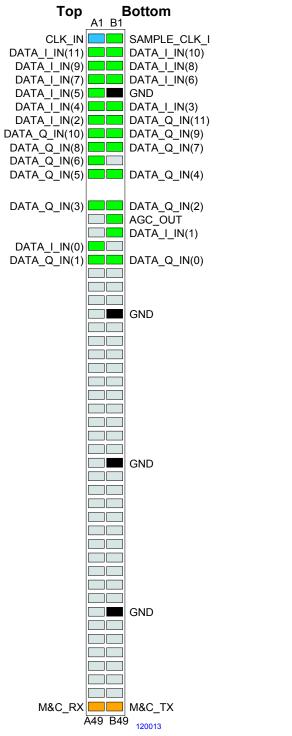

- Digitized real or complex waveform 2\*12-bit up to 125 Msamples/s

- Digital LVTTL 0-3.3V inputs from 1 to 64-bit per sample, up to 125 Msamples/s.

- VITA 49 or NASA SDDS formatted streaming waveforms over GbE LAN UDP (future).

- Download SDRAM contents to the following high-speed outputs:

- File transfer to a PC over GbE LAN TCP or UDP

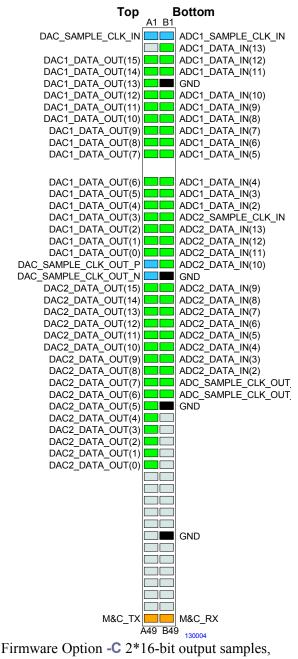

- Digitized real or complex waveform 2\*16-bit up to 125 Msamples/s

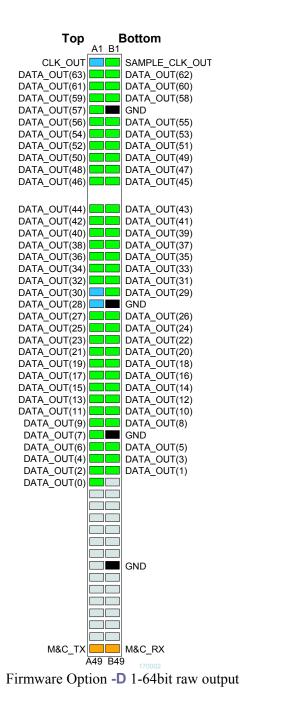

- Digital LVTTL 0-3.3V outputs from 1 to 64-bit per sample, up to 125 Msamples/s.

- VITA 49 or NASA SDDS formatted streaming waveforms over GbE LAN UDP (future).

- Upload to SDRAM and download from SDRAM memory can be made concurrent.

- I/O samples widths supported: 1,2,4,8,16,32,64 bits.

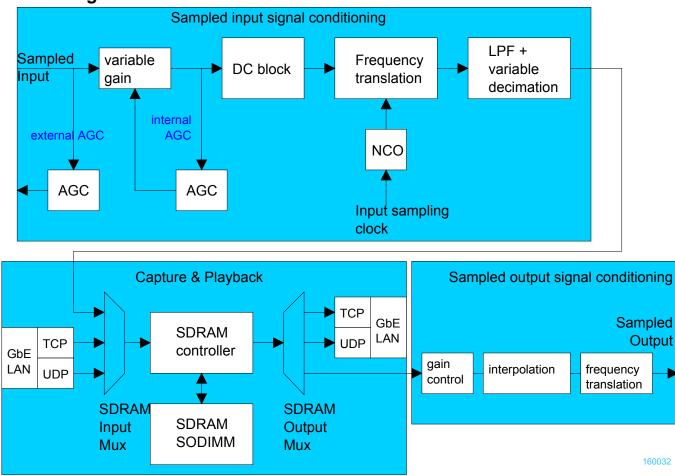

- Input signal conditioning includes AGC, DC block, frequency translation, variable decimation with anti-aliasing filtering for lower sampling rates and longer capture time.

<sup>&</sup>lt;sup>1</sup> Gigabit Ethernet LAN

MSS • 845-N Quince Orchard Boulevard • Gaithersburg, Maryland 20878 • U.S.A. Telephone: (240) 631-1111 Facsimile: (240) 631-1676 <u>www.ComBlock.com</u> © MSS 2019 Issued 10/7/2019

- Output signal conditioning includes variable interpolation and frequency translation.

- Input for an external, higher-stability 10 MHz frequency reference.

- Single run or continuous (circular) playback.

- User control over memory segmentation (upload/download start addresses, upload/download window sizes).

- Import from and export to tab-delimited text files or binary files.

- ComScope –enabled: key internal signals can be captured in real-time and displayed on host computer.

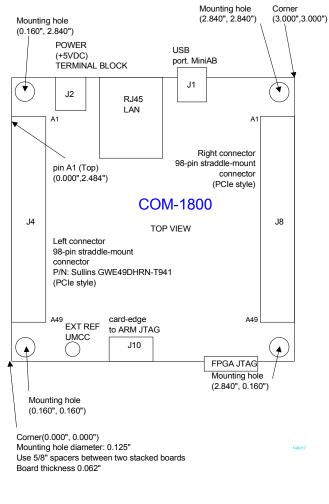

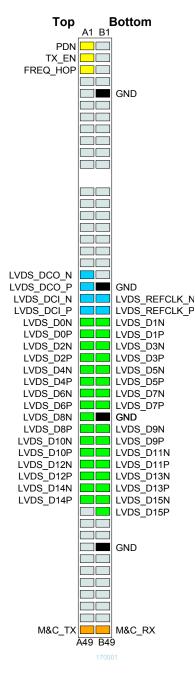

- High-speed 98-pin connectors (left, right). Single 5V supply with reverse voltage and overvoltage protection. Interfaces with 3.3V LVTTL logic.

#### Terminology:

This document uses a memory-centric terminology to describe the data flow:

**Upload** designates the transfer of data TO the COM-1806 SDRAM memory.

**Download** refers to the data transfer FROM the SDRAM.

Note: data transfer path and control path can be multiplexed over the same medium (LAN) or independent (for example high-speed data transfer over LAN and control over USB). Data transfer over USB is not supported.

For the latest data sheet, please refer to the **ComBlock** web site: <u>www.comblock.com/download/com1806.pdf</u>. These specifications are subject to change without notice.

For an up-to-date list of **ComBlock** modules, please refer to <u>http://www.comblock.com/product\_list.html</u>.

bottom side

## **Typical Applications**

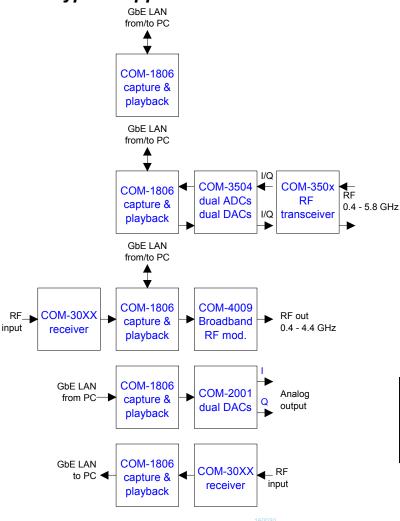

- COM-1806 as stand-alone module, captures a data stream from the GbE LAN, stores it in DDR3 memory for subsequent playback.

- COM-1806+COM-4009 = RF signal generator using a baseband waveform file uploaded from PC via high-speed LAN.

- COM-1806+COM-3504 = Simultaneous complex (I/Q) analog baseband capture (2\*12-bit) and playback (2\*16-bit). An additional COM-350x RF transceiver extends the functionality to RF signals.

- COM-1806+COM-2001 = Simple arbitrary waveform generator 2\*10-bit 125 MSamples/s. Input waveform file can be uploaded from a PC via gigabit Ethernet LAN.

- COM-1806+COM-30xx = RF signal capture and subsequent file download to a PC via gigabit Ethernet LAN.

In this product release a few features in grey are not yet implemented. Future firmware updates will also include

- VITA-49 GbE format

- NASA SDDS GbE format

### **Block Diagram**

## Configuration

Complete assemblies can be monitored and controlled centrally over a built-in USB or gigabit Ethernet LAN or other media available through adjacent ComBlocks.

The module configuration is stored in non-volatile memory.

### **Configuration (Basic)**

The easiest way to configure the COM-1806 is to use the **ComBlock Control Center** software supplied with the module on CD. In the **ComBlock Control Center** window detect the ComBlock module(s) by clicking the *Detect* button, next click to highlight the COM-1806 module to be configured, next click the *Settings* button to display the *Settings* window shown below.

ComBlock Control Center

File Operations Functions Help

🔆 🛰 🗗 🍇 🚺 🔛 🚇

COM1806A Wideband signal capture and playback

| COM1806 Wideband signal capture and playback Basic Settings                | ×                                                                                                      |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| put signal conditioning Upload Download Output signal conditioning General |                                                                                                        |

| ampled input signal conditioning                                           |                                                                                                        |

| Sampled input from: Left connector J6, 2*10/12-bit unsigned (COM-30xx) $$  | Real input                                                                                             |

| Sampling clock to external ADC/Receiver: 104000000 Samples/s               | Measured input sampling rate: 39999896 Samples/s                                                       |

| DC block                                                                   | Input nominal center frequency: -1000000.032 Hz                                                        |

| 🗌 Internal AGC 🛛 External AGC                                              | External gain control: 0 [0-4095]                                                                      |

| Decimation ratio: 1 [1-16384]                                              |                                                                                                        |

|                                                                            |                                                                                                        |

| Restore Default Apply changes                                              | Ok Advanced Cancel                                                                                     |

| ComScope, COM1806A Wideband signal capture and playback                    |                                                                                                        |

|                                                                            | ce Settings                                                                                            |

| TraceSignalRepresentationSampling Clock11V8-bit SignedVNominal (see specs) | Decimation     Visible     Plot style     Color     Export       V     1:1 (Off)     V     Lines     V |

| -0 20 40 60 80 100 120 140 160 180 200 220 240                             |                                                                                                        |

|                                                                            | $) \land \land \land \land \land \land \land \land$                                                    |

| 27<br>2<br>-23<br>-48<br>-73<br>-98                                        |                                                                                                        |

| COM1806 Wideband signal capture and playback Basic Settings                              | ×                                                            |

|------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Input signal conditioning Up/Download to/from SDRAM Output signal conditioning           | Network                                                      |

| Upload to DDR3 SDRAM                                                                     | Download from DDR3 SDRAM                                     |

| Input selection: LAN/TCP server, port 1024 v                                             | Output selection: LAN/TCP server, port 1026 V                |

| Upload file: C:\Users\HP10\Documents\MATLAB\input.txt                                    | Download to file: C:\Users\HP10\Documents\input2.txt         |

| ☑ Input text file, tab-delimited                                                         | Matlab-compatible output text file                           |

| Input width: 8 v bits                                                                    | Output width: 8 v bits Download start address: 0 Dec v Bytes |

| Upload start address: 0 Dec 🗸 Bytes                                                      | Download window length: 10000 Dec V Bytes                    |

| Upload window length: 131256 Dec 🗸 Bytes                                                 | Download transaction: No transaction                         |

| Upload transaction: Upload start upon external trigger 🗸                                 | Regulate download sampling rate: 999999.978 Samples/s        |

| 19%                                                                                      |                                                              |

| Starting upload                                                                          |                                                              |

| Restore Default Apply                                                                    | Ok Advanced Cancel                                           |

|                                                                                          |                                                              |

| COM1806 Wideband signal capture and playback Basic Settings                              | ×                                                            |

| Input signal conditioning Upload to SDRAM Download from SDRAM Output signal conditioning | Network                                                      |

| Sampled output signal Conditioning                                                       |                                                              |

| Sampling clock to external DAC: 🔽 160000000 Samples/s                                    | Frequency translation: -1000000 Hz                           |

|                                                                                          |                                                              |

|                                                                                          |                                                              |

|                                                                                          |                                                              |

| Interpolation ratio: 2 [1-16384]                                                         | Output gain: 1.25 [0.0-4.0]                                  |

|                                                                                          |                                                              |

|                                                                                          |                                                              |

|                                                                                          |                                                              |

|                                                                                          |                                                              |

|                                                                                          |                                                              |

| Restore Default Apply changes                                                            | Ok Advanced Cancel                                           |

|                                                                                          |                                                              |

| COM1806 Wideband signal capture and playback Basic Settings                              | ×                                                            |

| Input signal conditioning Upload to SDRAM Download from SDRAM Output                     | ut signal conditioning Network                               |

| Network                                                                                  |                                                              |

| External frequency reference                                                             | IP-address: 176 16 1 128                                     |

| Multicast IP address: 225 0 0 1                                                          | Subnet mask: 255 255 255 0                                   |

| Gateway address: 172 16 1 3                                                              |                                                              |

| Destination IP address: 172 16 1 68                                                      | UDP destination port: 1025                                   |

| MAC address: 00:00:00:00:00                                                              |                                                              |

| ·                                                                                        |                                                              |

| Restore Default Apply changes                                                            | Ok Advanced Cancel                                           |

# **Configuration (Advanced)**

Alternatively, users can access the full set of configuration features by specifying 8-bit control registers as listed below. These control registers can be set manually through the ComBlock Control Center or by software using the ComBlock API (see www.comblock.com/download/M&C\_reference.pdf)

All control registers are read/write.

Definitions for the <u>Control registers</u> and <u>Status</u> registers are provided below.

### **Control Registers**

The module configuration parameters are stored in volatile (SRT command) or non-volatile memory (SRG command). All control registers are read/write.

Undefined control registers or register bits are for backward software compatibility and/or future use. They are ignored in the current firmware version.

The processing clock  $f_{clkp}$  is 125 MHz.

| General                                                                                                                         |  |  |

|---------------------------------------------------------------------------------------------------------------------------------|--|--|

| Configuration                                                                                                                   |  |  |

| 0 = internal TCXO as frequency reference.                                                                                       |  |  |

| 1 = external. Use the 10 MHz clock<br>externally supplied through the J6<br>SMA connector as frequency<br>reference.<br>REG0(7) |  |  |

|                                                                                                                                 |  |  |

| Sampled input signal conditioning        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameters                               | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Sampled input<br>selection               | 0 = undefined<br>1 = COM-3504 right connector,<br>2*12bit unsigned<br>2 = COM-30XX left connector,<br>2*12-bit unsigned<br>3 = COM-30XX right connector,<br>2*12-bit unsigned<br>4 = Internally-generated<br>unmodulated carrier.                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                                          | REG0(2:0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Generate ADC<br>sampling clock           | In some cases, the external<br>receiver/analog-to-digital converter<br>may require a sampling clock. The<br>COM-1806 generates such a<br>programmable frequency clock on<br>pin J4.A14.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                                          | 0 = disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                                          | 1 = enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                                          | REG1(7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| ADC sampling rate<br>f <sub>clk_rx</sub> | In some cases, the external<br>receiver/analog-to-digital converter<br>may require a sampling clock. The<br>COM-1806 generates such a<br>programmable frequency clock on<br>pin J4.A14 by defining the<br>parameters below:<br>Expressed as $f_{elk_rx} = 125$ MHz *<br>M / (D * O)) where<br>D is an integer divider in the range 1<br>- 106<br>M is a multiplier in the range 2.0 to<br>64.0 by steps of 0.125. Fixed point<br>format 7.3<br>O is a divider in the range 2.0 to<br>128.0 by steps of 0.125. Fixed point<br>format 8.3<br>Note: the graphical use interface<br>computes the best values for M, D |  |

|                                          | and O.<br>Maximum <b>f</b> <sub>elk_rx</sub> : 160 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|                                          | REG1(6:0) = D<br>REG2 = M(7:0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|                        | ,                                                                                                                                                                                                  |                                                |                                                                                                                                                                                                                                                                              |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | REG3(1:0) = M(9:8)                                                                                                                                                                                 |                                                | Valid range 0 to 14.<br>REG8(4:0)                                                                                                                                                                                                                                            |

|                        | REG4 = O(7:0)                                                                                                                                                                                      |                                                |                                                                                                                                                                                                                                                                              |

|                        | REG5(2:0) = O(10:8)                                                                                                                                                                                | Nominal Center frequency $(\mathbf{f}_{c rx})$ | As the signal capture is best                                                                                                                                                                                                                                                |

| Real or complex input? | 0 = complex (I,Q) baseband input<br>samples<br>1 = real samples on I-channel input.                                                                                                                | frequency (i <sub>c_rx</sub> )                 | implemented at baseband (near-zero<br>center frequency), the input signal<br>must first be translated in frequency.                                                                                                                                                          |

|                        | Q-channel input is zeroed. Use in the case of IF input.                                                                                                                                            |                                                | Enter the expected center frequency of the input signal. 32-bit integer                                                                                                                                                                                                      |

|                        | REG6(0)                                                                                                                                                                                            |                                                | expressed as                                                                                                                                                                                                                                                                 |

| DC block               | The bias removal circuit removes<br>any spurious DC bias that may be<br>introduced by an external A/D<br>convert. Disable this function if the<br>input signal includes a legitimate<br>DC offset. |                                                | <ul> <li>f<sub>c_rx</sub> * 2<sup>32</sup> / f<sub>input_sampling</sub>.</li> <li>where f<sub>input_sampling</sub> is the input sampling rate.</li> <li>In the case of IF undersampling, the residual intermediate frequency can be removed here. For example, in</li> </ul> |

|                        | 0 = disable<br>1 = enable                                                                                                                                                                          |                                                | the case of a 150 MHz IF signal<br>sampled at 120 Msamples/s, the 30<br>MHz residual frequency is removed                                                                                                                                                                    |

|                        |                                                                                                                                                                                                    |                                                | here by entering 0x40000000.                                                                                                                                                                                                                                                 |

|                        | REG6(1)                                                                                                                                                                                            |                                                |                                                                                                                                                                                                                                                                              |

| Internal AGC           | Enable or disable the input                                                                                                                                                                        |                                                | REG9(LSB) – REG12(MSB)                                                                                                                                                                                                                                                       |

| enable                 | automatic gain control<br>0 = disabled (unit gain)<br>1 = enabled                                                                                                                                  | CIC decimation<br>ratio <b>R</b>               | Combined low-pass filter /<br>decimation. The decimation ratio R<br>is set here.                                                                                                                                                                                             |

|                        |                                                                                                                                                                                                    |                                                | Valid range 1 to 16384. 0 is illegal.                                                                                                                                                                                                                                        |

|                        | REG6(2)                                                                                                                                                                                            |                                                | Usage: be careful not to decimate                                                                                                                                                                                                                                            |

| External AGC enable    | 0 = gain control fixed at a preset<br>level (see below)                                                                                                                                            |                                                | too much as the CIC decimation<br>filter is not very sharp and thus can                                                                                                                                                                                                      |

|                        | 1 = enabled                                                                                                                                                                                        |                                                | distort the modulation signal.                                                                                                                                                                                                                                               |

|                        | The analog gain control output is on pin J4.B13                                                                                                                                                    |                                                | For most applications, select $R = 1$ .                                                                                                                                                                                                                                      |

|                        | REG6(3)                                                                                                                                                                                            |                                                | REG13: $LSB^2$                                                                                                                                                                                                                                                               |

| External AGC gain      | Gain settings for an external variable gain amplifier. This setting                                                                                                                                |                                                | REG14(6:0): MSB                                                                                                                                                                                                                                                              |

|                        | is used when the external AGC is<br>disabled. It is also the initial gain<br>value before the AGC takes over.                                                                                      | Enable Half-Band<br>Filter                     | Bypass (0) / Enable (1) Half-Band<br>Filter following the CIC decimation<br>filter.                                                                                                                                                                                          |

|                        | Unsigned 12-bit number. 4095                                                                                                                                                                       |                                                |                                                                                                                                                                                                                                                                              |

|                        | represents the minimum gain, 0 the maximum gain.                                                                                                                                                   |                                                | REG14(7)                                                                                                                                                                                                                                                                     |

|                        | REG6(7:4): LSB<br>REG7: MSB                                                                                                                                                                        |                                                |                                                                                                                                                                                                                                                                              |

| External AGC           | Users can to optimize AGC response                                                                                                                                                                 |                                                |                                                                                                                                                                                                                                                                              |

| response time          | time while avoiding instabilities                                                                                                                                                                  |                                                |                                                                                                                                                                                                                                                                              |

|                        | (depends on external factors such as                                                                                                                                                               |                                                |                                                                                                                                                                                                                                                                              |

|                        | gain signal filtering at the RF front-end                                                                                                                                                          |                                                |                                                                                                                                                                                                                                                                              |

|                        | and chip rate). The AGC_DAC gain                                                                                                                                                                   |                                                |                                                                                                                                                                                                                                                                              |

|                        | control signal is updated as follows                                                                                                                                                               |                                                |                                                                                                                                                                                                                                                                              |

|                        | 0 = every decimated sample,<br>1 = every 2 decimated samples,                                                                                                                                      |                                                |                                                                                                                                                                                                                                                                              |

|                        | 2 = every 4 decimated samples,<br>2 = every 4 decimated samples,                                                                                                                                   |                                                |                                                                                                                                                                                                                                                                              |

|                        | 3 = every decimated samples, etc                                                                                                                                                                   |                                                |                                                                                                                                                                                                                                                                              |

|                        | 10 = every 1000 decimated samples.                                                                                                                                                                 | $^{2}$ LSB = Least Sig                         | nificant Byte                                                                                                                                                                                                                                                                |

<sup>2</sup> LSB = Least Significant Byte MSB = Most Significant Byte

| Upload to SDRAM          |                                                                                             |  |

|--------------------------|---------------------------------------------------------------------------------------------|--|

| Parameters               | Configuration                                                                               |  |

| Input selection          | 1 = LAN/TCP server, port 1024                                                               |  |

|                          | 2 = LAN/UDP packets                                                                         |  |

|                          | 3 = sampled input waveform after                                                            |  |

|                          | conditioning (1 or 2*16-bit)                                                                |  |

|                          | 4 = digital inputs (no conditioning),                                                       |  |

|                          | left connector                                                                              |  |

|                          | 5 = digital inputs (no conditioning),<br>right connector                                    |  |

|                          | 6 = VITA 49 formatted waveform<br>from LAN/UDP(future)                                      |  |

|                          | 7 = NASA SDDS formatted                                                                     |  |

|                          | waveform from LAN/UDP (future)                                                              |  |

|                          | REG15(3:0)                                                                                  |  |

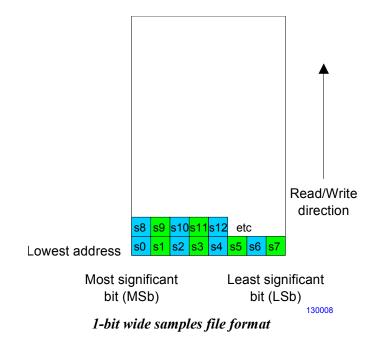

| Upload sample data width | Number of bits in each input sample<br>saved into SDRAM. Valid entries:<br>1,2,4,8,16,32,64 |  |

|                          | Must be consistent with the input                                                           |  |

|                          | selection above. For example,                                                               |  |

|                          | LAN/TCP-IP data is always 8-bit wide.                                                       |  |

|                          | wide.                                                                                       |  |

|                          | REG16(6:0)                                                                                  |  |

| Upload start<br>address  | It is possible to upload the entire                                                         |  |

| address                  | memory or a fraction thereof. The upload section is identified by its                       |  |

|                          | start address and length.                                                                   |  |

|                          | Unit: number of SDRAM 64-bit                                                                |  |

|                          | words.                                                                                      |  |

|                          | REG17 (LSB) – REG20 (MSB)                                                                   |  |

| Upload window            | Upload window length.                                                                       |  |

| length                   | Unit: number of SDRAM 64-bit                                                                |  |

|                          | words.                                                                                      |  |

|                          | Wrapping around is not allowed, i.e.                                                        |  |

|                          | window start address + length must<br>be less than the memory upper                         |  |

|                          | address.                                                                                    |  |

|                          | REG21 (LSB) – REG24 (MSB)                                                                   |  |

| Upload transaction       | 0 = no change                                                                               |  |

|                          | 1 = immediate upload start. Upload                                                          |  |

|                          | will continue until the specified                                                           |  |

|                          | number of bytes in the upload                                                               |  |

|                          | window length is received.                                                                  |  |

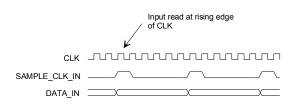

|                          | 2 = start upload upon receiving a<br>trigger pulse over the                                 |  |

|                          | UPLOAD_TRIGGER pin. Starts at                                                               |  |

|                          | the falling edge of the pulse.                                                              |  |

|                          | 3 = immediately stop any on-going                                                           |  |

|                          | upload transaction.                                                                         |  |

|                          | REG25(2:0)                                                                                  |  |

| Parameters                | Configuration                                                                                                          |

|---------------------------|------------------------------------------------------------------------------------------------------------------------|

| Download start<br>address | It is possible to download the entire<br>memory or a fraction thereof. The<br>download section is identified by its    |

|                           | start address and length.<br>Unit: number of SDRAM 64-bit                                                              |

|                           | words.                                                                                                                 |

|                           | REG27 (LSB) – REG30 (MSB)                                                                                              |

| Download window           | Download window length.                                                                                                |

| length                    | Unit: number of SDRAM 64-bit words.                                                                                    |

|                           | Wrapping around is not allowed, i.e<br>window start address + length must<br>be less than the memory upper<br>address. |

|                           | REG31 (LSB) – REG34 (MSB)                                                                                              |

| Download                  | 0 = no change                                                                                                          |

| transaction               | 1 = single download, immediate<br>start                                                                                |

|                           | 2 = continuous (circular) download<br>immediate start                                                                  |

|                           | 3 = single download, external<br>trigger                                                                               |

|                           | 4 = continuous (circular) download<br>external trigger                                                                 |

|                           | 5 = immediately stop current transaction.                                                                              |

|                           | The trigger is a pulse over the<br>DOWNLOAD_TRIGGER pin.<br>Starts at the falling edge of the                          |

|                           | pulse.                                                                                                                 |

|                           | REG35(2:0)                                                                                                             |

| Output selection          | 1 = LAN/TCP server, port 1026                                                                                          |

|                           | 2 = LAN/UDP packets                                                                                                    |

|                           | 3 = sampled output waveform<br>through output conditioning (1 or<br>2*16-bit)                                          |

|                           | 4 = digital outputs (no conditioning), right connector                                                                 |

|                           | 5 = VITA 49 formatted waveform t<br>LAN/UDP(future)                                                                    |

|                           | 6 = NASA SDDS formatted<br>waveform to LAN/UDP (future)                                                                |

|                           | REG36(3:0)                                                                                                             |

| Output data width                                | During download, the SDRAM                                                                                                                                                     | Sampled output signal conditioning |                                                                                                                                                      |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                  | contents is segmented into samples                                                                                                                                             | Parameters                         | Configuration                                                                                                                                        |

|                                                  | of various bit-widths as specified<br>here. Supported data widths are:                                                                                                         | Output DAC sampling rate           | In many cases, the external Digital to<br>Analog Converter requires a sampling                                                                       |

|                                                  | 1,2,4,8,16,32,64                                                                                                                                                               | <b>f</b> <sub>clk_tx</sub>         | clock. The COM-1806 generates such a programmable frequency clock on                                                                                 |

|                                                  | Must be consistent with the output selection above. For example,                                                                                                               |                                    | pins<br>J8.A1 (options –A and -D)                                                                                                                    |

|                                                  | LAN/TCP-IP data is always 8-bit wide.                                                                                                                                          |                                    | J8.A19/A20 (option –C)<br>J8.B21/B22 (option –E)                                                                                                     |

|                                                  | REG37(6:0)                                                                                                                                                                     |                                    | The DAC sampling rate is expressed<br>as $\mathbf{f}_{\text{clk},\text{tx}} = 125 \text{ MHz} * M / (D * O)$ )                                       |

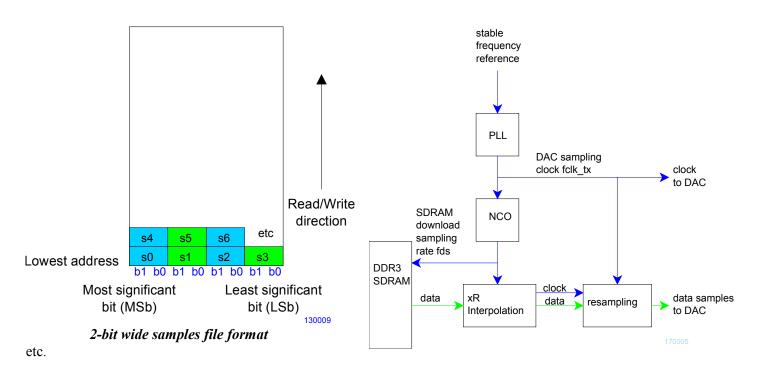

| Download sampling<br>rate <b>f</b> <sub>ds</sub> | Download sampling frequency<br>BEFORE interpolation.                                                                                                                           |                                    | where                                                                                                                                                |

|                                                  | Not applicable when the download output is directed to LAN.                                                                                                                    |                                    | D is an integer divider in the range 1 - 106                                                                                                         |

|                                                  | Used only when the data is pushed<br>out to the next module. (see flow<br>control). Ignored when data is                                                                       |                                    | M is a multiplier in the range 2.0 to 64.0 by steps of 0.125. Fixed point format 7.3                                                                 |

|                                                  | pulled in by the external flow<br>control.<br>The download sampling rate fds is                                                                                                |                                    | O is a divider in the range 2.0 to 128.0 by steps of 0.125. Fixed point format 8.3                                                                   |

|                                                  | expressed as $\mathbf{f}_{ds} / \mathbf{f}_{clk\_tx} * 2^{31}$ , where $\mathbf{f}_{clk\_tx}$ is the output (DAC) sampling frequency.                                          |                                    | Note: the graphical use interface<br>computes the best values for M, D and<br>O.                                                                     |

|                                                  | The download sampling clock is generated with a numerically                                                                                                                    |                                    | Maximum <b>f</b> <sub>elk_tx</sub> : 160 MHz                                                                                                         |

|                                                  | controlled oscillator (NCO) It is<br>therefore affected by jitter uniform                                                                                                      |                                    | REG71(6:0) = D                                                                                                                                       |

|                                                  | over the $\mathbf{f}_{\text{clk}_{\text{tx}}}$ period. Jitter can be                                                                                                           |                                    | REG72 = M(7:0)                                                                                                                                       |

|                                                  | alleviated by selecting a power of                                                                                                                                             |                                    | REG73(1:0) = M(9:8)                                                                                                                                  |

|                                                  | two ratio $\mathbf{f}_{clk\_tx} / \mathbf{f}_{ds}$                                                                                                                             |                                    | REG74 = O(7:0)                                                                                                                                       |

|                                                  | T                                                                                                                                                                              |                                    | REG75(2:0) = O(10:8)                                                                                                                                 |

|                                                  | To minimize jitter, select 1/2 <sup>n</sup> , for<br>example<br>x"80000000" for sampling rate =<br>f <sub>elk_tx</sub> [= no interpolation]<br>x"40000000" for sampling rate = | Interpolation<br>factor            | Download samples can be interpolated<br>up to the output sampling rate $f_{clk_tx}$ to<br>smoothen the output waveform and<br>thus reduce harmonics. |

|                                                  | $f_{elk_tx} / 2$ x"20000000" for sampling rate = $f_{elk_tx} / 4, etc$                                                                                                         |                                    | Zero will bypass all interpolation stages.                                                                                                           |

|                                                  | REG38 (LSB) – REG41 (MSB)                                                                                                                                                      |                                    | The maximum interpolation factor is the ratio of output sampling rate $\mathbf{f}_{clk\_tx}$ to download sampling rate $\mathbf{f}_{ds}$ .           |

|                                                  |                                                                                                                                                                                |                                    | The most accurate output waveform is obtained when that ratio is a power of 2.                                                                       |

|                                                  |                                                                                                                                                                                |                                    | Use 2 to enable one half-band filter.                                                                                                                |

|                                                  |                                                                                                                                                                                |                                    | Use 4 to enable two half-band filters                                                                                                                |

|                                                              | Use 8 or above to enable both half-<br>band filters and a CIC interpolation<br>filter.<br>Valid range 0 or 1 (no interpolation) to<br>2 <sup>23</sup> |

|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                              | REG76 (LSB) – REG78 (MSB)                                                                                                                             |

| Output<br>frequency<br>translation ( <b>f</b> <sub>c</sub> ) | The output signal can be shifted in frequency                                                                                                         |

|                                                              | 32-bit signed integer (2's complement<br>representation) expressed as<br>$f_c * 2^{32} / f_{elk_tx}$                                                  |

|                                                              | REG79 (LSB) – REG82 (MSB)                                                                                                                             |

| Output gain                                                  | This 16-bit gain setting is formatted as<br>a 4.12 fixed-point number. The unit<br>gain is thus 0x1000.                                               |

|                                                              | Beware of possible saturation when increasing the output level.                                                                                       |

|                                                              | REG83 (LSB) – REG84 (MSB)                                                                                                                             |

| Network Interface        |                                                                                                                                                                                                                                                  |  |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameters               | Configuration                                                                                                                                                                                                                                    |  |

| MAC addresses<br>LSB     | In order to ensure the uniqueness of<br>MAC addresses, users can define<br>bits 7:1 through REG236(7:1).<br>The MAC addresses upper bits are<br>automatically tied to the nearly<br>unique FPGA DNA_ID.                                          |  |

| IP address               | REG236(7:0).4-byte IPv4 address.Example : 0x AC 10 01 80designates the default address172.16.1.128Note3REG44 (MSB) – REG47 (LSB)                                                                                                                 |  |

| Subnet mask              | REG48 (MSB) – REG51(LSB)                                                                                                                                                                                                                         |  |

| Gateway IP address       | REG52 (MSB) – REG55(LSB)                                                                                                                                                                                                                         |  |

|                          | 4-byte IPv4 address used for SDDS<br>input stream.<br>Example : 0x E1 00 00 01 designates<br>address 225.0.0.1<br>Use 0.0.0.0 to signify that multicasting<br>is not supported.<br>REG56 (MSB) – REG59 (LSB)                                     |  |

| address                  | 4-byte IPv4 address<br>Destination IP address for UDP frames.<br>Example : 0x AC 10 01 80 designates<br>address 172.16.1.128<br>The new address becomes effective<br>immediately (no need to reset the<br>ComBlock).<br>REG60 (MSB) – REG63(LSB) |  |

| UDP tx destination ports | Output UDP frames are routed to this user-<br>defined port number:<br>REG64(LSB) – REG65(MSB)                                                                                                                                                    |  |

Note1: All upload transactions are enacted upon writing to temporary control register REG25 [use the SRT command. See API].

Note2: All download transaction are enacted upon writing to temporary control register REG35 [use the SRT command. See API].

Note3: Some changes are enacted upon reset or writing to the last control register (REG84).

# Monitoring

## **Status registers**

| D.                                            | ComBlock Control Center                         |

|-----------------------------------------------|-------------------------------------------------|

| <u>File</u> Operations Functions <u>H</u> elp |                                                 |

| 🔆 🔌 📽 🎸 🚺 🖢 🖽                                 |                                                 |

| COM1806C Wildebal                             | tus register contents for the selected comblock |

### Status registers (SREG) are read-only.

|               | Monitoring                                 |

|---------------|--------------------------------------------|

|               |                                            |

|               | At power-up, the hardware platform         |

| check         | performs a quick self check. The result is |

|               | stored in status registers SREG0-7         |

|               | Properly operating hardware will result in |

|               | the following sequence being displayed:    |

|               | SREG0-SREG7 = 01 F1 1D xx 1F 93 10 22      |

| Clocks status | SREG8(0): 1 when frequency reference       |

|               | (TCXO or external 10 MHz) is present       |

|               |                                            |

|               | SREG8(1): 25 MHz PLL lock                  |

|               | SREG8(2): 125 MHz PLL lock                 |

|               | SREG8(3): Tx sampling clock PLL lock       |

|               | SREG8(4): Rx sampling clock PLL lock       |

|               | Steless(1). Tex sumpting clock T EE lock   |

| Memory status | SDRAM memory ready                         |

| status        | SREG8(6)                                   |

| Input         | The input sampling rate is measured and    |

| sampling rate | displayed here. The frequency              |

| sumpting fute |                                            |

|               | measurement accuracy is a function of the  |

|               | internal clock stability.                  |

|               |                                            |

|               | The measurement is expressed in Hz.        |

|               |                                            |

|               | SREG9 (LSB) – SREG12(MSB)                  |

| External gain | SREG13 (LSB)                               |

| (controlled   | SREG14(3:0) (MSB)                          |

| by external   |                                            |

| AGC)          |                                            |

| SDRAM         | Current SDRAM write pointer address.       |

| write pointer | Used to monitor the upload progress.       |

| address       | When finished, the write pointer will      |

|               | point to the last address written to.      |

|               | Unit: number of SDRAM 64-bit words.        |

|               |                                            |

|               | SREG15 (LSB) – SREG18 (MSB)                |

| SDRAM read    | Current SDRAM read pointer address.        |

| pointer       | Used to monitor the download progress.     |

| address       | When finished, the read pointer will point |

|               | to the last address read.                  |

|               |                                            |

|               | Unit: number of SDRAM 64-bit words.        |

|               |                                            |

|               | SREG19 (LSB) – SREG22 (MSB)                |

| Upload      | 16-bit checksum obtained by summing all              |  |

|-------------|------------------------------------------------------|--|

| checksum    | 16-bit words uploaded to the SDRAM.                  |  |

|             | Wait until the upload completion to read             |  |

|             | this checksum.                                       |  |

|             | SREG23 (LSB) – SREG24 (MSB)                          |  |

| Download    | 16-bit checksum obtained by summing all              |  |

| checksum    | 16-bit words downloaded from the                     |  |

|             | SDRAM. Wait until the single download                |  |

|             | completion to read this checksum. The                |  |

|             | download checksum should match the                   |  |

|             | upload checksum if the sizes and start               |  |

|             | addresses match for the upload and the               |  |

|             | single download. Does not work with                  |  |

|             | continuous download.                                 |  |

|             | SREG25 (LSB) – SREG26 (MSB)                          |  |

| Saturation  | Saturation in the output signal                      |  |

|             | conditioning path. 0 when no saturation.             |  |

|             | These flags are reset upon reading this              |  |

|             | status register.                                     |  |

|             | SREG27                                               |  |

| TCP-IP Con  | nection Monitoring                                   |  |

| Parameters  | Monitoring                                           |  |

| MAC address | Unique 48-bit hardware address (802.3).              |  |

|             | In the form SREG32:SREG33:SREG34:                    |  |

|             | :SREG37                                              |  |

| TCP-IP      | Bit $0 = \text{port } 1028 \text{ (M\&C) connected}$ |  |

| server      | Bit 1 = port 1024 (upload data) connected            |  |

| connection  | Bit $2 = port 1026$ (download data)                  |  |

| status      | connected                                            |  |

|             | 1 for connected to a remote client, 0                |  |

|             | otherwise                                            |  |

|             | SREG38(2:0)                                          |  |

Note: reading status register SREG7 latches multibyte status words.

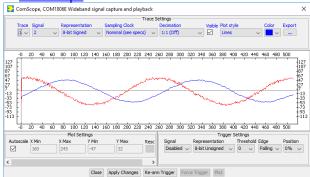

# ComScope Monitoring

Key internal signals can be captured in real-time and displayed on a host computer using the ComScope feature of the ComBlock Control

Center. Click on the button to open the ComScope panel.

The COM-1806 signal traces and trigger are defined as follows:

| Trace 1 signals                                                                    | Format                    | Nominal<br>sampling<br>rate | Buffer<br>length<br>(samples)  |

|------------------------------------------------------------------------------------|---------------------------|-----------------------------|--------------------------------|

| 1: Input signal I-<br>channel                                                      | 8-bit<br>signed<br>(8MSB) | Input<br>sampling<br>rate   | 512                            |

| 2: Input signal (I-<br>channel) after AGC,<br>frequency translation,<br>decimation | 8-bit<br>signed<br>(8MSB) | Input<br>sampling<br>rate/R | 512                            |

| 3: Replay signal (I-<br>channel) before<br>output conditioning                     | 8-bit<br>signed<br>(8MSB) | Output<br>sampling<br>rate  | 512                            |

| Trace 2 signals                                                                    | Format                    | Nominal<br>sampling<br>rate | Capture<br>length<br>(samples) |

| 1: Input signal Q-<br>channel                                                      | 8-bit<br>signed<br>(8MSB) | Input<br>sampling<br>rate   | 512                            |

| 2: Input signal (Q-<br>channel) after AGC,<br>frequency translation,<br>decimation | 8-bit<br>signed<br>(8MSB) | Input<br>sampling<br>rate/R | 512                            |

| 3: Replay signal (Q-<br>channel) before<br>output conditioning                     | 8-bit<br>signed<br>(8MSB) | Output<br>sampling<br>rate  | 512                            |

| Trigger Signal 1: UPLOAD TRIGGER                                                   | <b>Format</b><br>Binary   |                             |                                |

Signals sampling rates can be changed under software control by adjusting the decimation factor and/or selecting the  $f_{elkp}$  processing clock as real-time sampling clock.

In particular, selecting the  $f_{clkp}$  processing clock as real-time sampling clock allows one to have the same time-scale for all signals.

The ComScope user manual is available at www.comblock.com/download/comscope.pdf.

# Operation

## Upload from a file

Objective: transfer a file contents into SDRAM memory.

**Step 1**: Create a file containing the data samples.

The file can be binary (see the <u>file format section</u> on how to pack samples into the binary file) or text file with two tab-delimited columns of 16-bit signed integers (i.e. in the range -32768 to +32767). The GUI automatically performs the conversion from tab-delimited text to binary prior to storage in SDRAM.

**Step 2**: Using the ComBlock Control Center (Graphical User Interface). Highlight the COM-1806 and click the Settings button. Select the up/download tab and select

- Transfer medium (LAN TCP)

- File location

- Start upload address: where the first byte will be stored. Must be an integer multiple of 64 bits.

- Upload window length: the actual length will be automatically adjusted if the file size is smaller than the specified window length.

Note: in the case of an input text file, the upload window length value shown is the text file size. However, the actual number of bytes uploaded will be computed after text to binary conversion. An upload completion message will show the actual upload window length.

• Upload transaction = Immediate upload start.

| COM1806 Wideband          | signal capture and playback Ba    | sic Settings               |

|---------------------------|-----------------------------------|----------------------------|

| Input signal conditioning | Up/Download to/from SDRAM         | Output signal conditioning |

| Upload to DDR3 SDRAM      |                                   |                            |

| Input selection: LAN      | TCP server, port 1024             | ~                          |

| Upload file: 1            | users\Alain\Documents\1MATLAB\    | outputFile.txt             |