# COM-1808SOFT\_TX DVB-S2 Transmitter VHDL source code overview / IP core

### Overview

The COM-1808SOFT\_TX is a DVB-S2 compliant transmitter written in generic VHDL.

The entire **VHDL source code** is deliverable. It is portable to a variety of FPGA targets.

#### Key features and performance:

- Flexible programmable features:

- input streams attributes (dynamic: can change every BBFRAME):

16200/64800b frame length, FEC encoding rate, modulation type

- input streams attributes: stream type (transport stream, generic stream) packetized, generic bit stream), user packet length, input stream synchronization, null packet detection

- modulation attributes: symbol rate, frequency offset, SRRC filter roll-off, common to all input streams.

- Provided with IP core:

- VHDL source code

- GNU radio project and Matlab conversion .m program for generating DVB-S2 waveforms.

- VHDL testbench

- PRBS11 test sequence generator, AWGN noise generator

## Supported features

| Feature                                                                        | Supported                                                                                                                                                                                                             |  |  |

|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Inputs                                                                         | <ul> <li>Single or multiple<br/>MPEG Transport<br/>Stream. 188-Byte fixed<br/>length frames, Byte-<br/>wide.</li> <li>Single or multiple<br/>Generic Stream<br/>(packetized or<br/>continuous). Byte-wide.</li> </ul> |  |  |

|                                                                                | • BBFRAMEs at the mode adaptation input interface.                                                                                                                                                                    |  |  |

| Payload bit rate example                                                       | 858 Mbits/s (8-PSK, rate 9/10,<br>Xilinx Ultrascale+ -2)                                                                                                                                                              |  |  |

| Input stream<br>synchronizer                                                   | Yes                                                                                                                                                                                                                   |  |  |

| Null packet deletion                                                           | Yes                                                                                                                                                                                                                   |  |  |

| Error correction<br>encoding                                                   | LDPC + BCH                                                                                                                                                                                                            |  |  |

| Encoding rate                                                                  | 1/4, 1/3, 2/5, 1/2, 3/5, 2/3, 3/4,<br>4/5, 5/6, 8/9, 9/10                                                                                                                                                             |  |  |

| Coding and modulation                                                          | CCM, VCM, ACM                                                                                                                                                                                                         |  |  |

| FEC frame                                                                      | normal (64800 bits)<br>short (16200 bits)                                                                                                                                                                             |  |  |

| Modulation                                                                     | QPSK, 8-PSK, 16APSK,<br>32APSK                                                                                                                                                                                        |  |  |

| Maximum<br>modulation symbol<br>rate (Xilinx<br>ultrascale+<br>-2 speed grade) | 318 MSymbols/s<br>636 MSamples/s                                                                                                                                                                                      |  |  |

| SRRC filter roll-off                                                           | 0.35, 0.25 and 0.20                                                                                                                                                                                                   |  |  |

| Output                                                                         | complex (I,Q) baseband samples, 16-bit precision. DDR                                                                                                                                                                 |  |  |

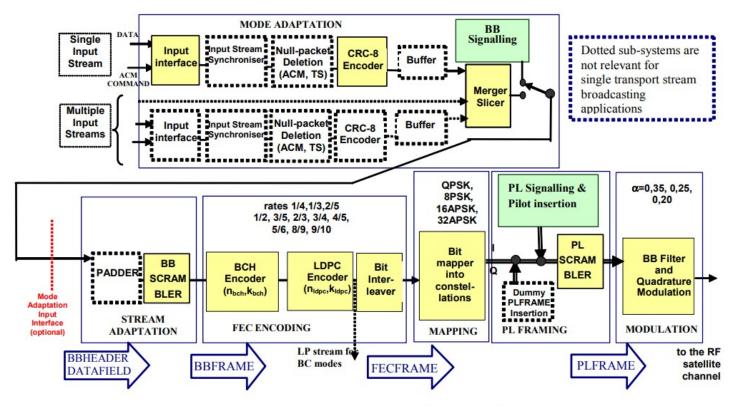

Figure 1: Functional block diagram of the DVB-S2 System

Extract from reference document [1]

# Configuration

#### Synthesis-time configuration parameters

The following constants are user-defined in the *DVBS2\_TX.vhd* component generic section or *DVB2\_TX\_PKG* package section prior to synthesis. These parameters generally affect the size of the transmitter embodiment.

| Synthesis-time<br>configuration parameters | Configuration                                                                                                                                             |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXT_MODE_ADAPT                             | Optional mode Adaptation<br>input interface with in-<br>band signaling. When<br>enabled, the input streams<br>interface is disabled. See<br>[1] Annex I.2 |

| N_TS                                       | Number of parallel input<br>streams (transport streams<br>or generic streams)                                                                             |

| AWGN_INST                                  | Additive White Gaussian<br>Noise generator<br>instantiation (1).<br>(0) during operations to<br>save space in FPGA (and<br>to increase clock speed.       |

| POWER_<br>MEASUREMENT_INST                 | Signal and noise power<br>measurements at the<br>transmitter output.<br>1 to instantiate,<br>0 otherwise                                                  |

#### **Run-time configuration parameters**

The user can set and modify the following controls at run-time through the top level component interface:

| Modulator Parameters<br>(common to all input<br>streams) | Configuration                                                                                                                              |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| MOD_SYMBOL_RATE<br>(32:0)                                | Symbol rate expressed as<br>2^32* symbol rate<br>/ DAC sampling rate<br>f <sub>CLK_TXg</sub><br>Maximum symbol rate =<br>DAC sampling rate |

| MOD_CENTER_FREQ<br>(31:0)                                | Modulated signal center frequency. Expressed as $2^{32} * \text{fc}/f_{\text{CLK TXg}}$                                                    |

| MOD_RO(2:0)                                              | Square root raised cosine<br>filter roll-off factor:<br>0= 35%, 1 = 25%,<br>2 = 20%, 4 = 15%,<br>5 = 10%, 6 = 5%                           |

| MOD_CONTROL(7:0)                                         | bit 0: spectrum inversion<br>enabled (1) or not (0)<br>bit 1: unmodulated carrier<br>output test mode                                      |

| MOD_SIGNAL_<br>SCALING(15:0)                             | Output amplitude scaling<br>factor. 16-bit unsigned                                                                                        |

| AWGN_SIGNAL_<br>SCALING(15:0)                            | Additive White Gaussian<br>Noise level (amplitude)<br>16-bit unsigned                                                                      |

| Individual<br>stream<br>configuration,<br>fixed at reset | Configuration                                                                                          |  |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

| STREAMS_<br>TYPE (1:0)                                   | TS/GS field (2 bits): Transport<br>Stream Input or Generic Stream<br>Input (packetized or continuous)  |  |

|                                                          | 11 = transport stream, 188B frame<br>00 = generic stream, packetized,<br>user-defined fixed length UPL |  |

| STREAMS_UPL<br>(15:0)                                    | 01 = generic bit stream<br>User Packet Length in bits, in the<br>range 0 to 65 535                     |  |

|                                                          | fixed 188 Bytes for transport stream,<br>up to 65535 bits for generic stream                           |  |

|                                                          | If UPL is greater than 65535 bits, use generic bit stream.                                             |  |

|                                                          | For packetized stream, UPL includes the sync byte                                                      |  |

| STREAMS_<br>ISSYI                                        | Input stream synchronization indicator. See [1] annex D.2                                              |  |

| STREAMS_NPD                                              | Null packet detection.<br>Generally enabled for transport<br>stream and/or ACM                         |  |

Note: when using the optional mode adaptation input interface, these configuration parameters are embedded within the 10-Byte header of the input BBFRAME.

| DDFKAME.                                                                           |                                                                                                                                                                                            |

|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Individual<br>stream<br>configuration,<br>dynamic (can<br>change every<br>BBFRAME) | Configuration                                                                                                                                                                              |

| STREAMS_FL<br>(1:0)                                                                | Frame length<br>0: DVB-S2 normal frame<br>n <sub>ldpc</sub> =64800<br>1: DVB-S2 and DVB-S2X short<br>frame n <sub>ldpc</sub> =16200<br>2: DVB-S2X medium frame<br>n <sub>ldpc</sub> =32400 |

| STREAMS_<br>MODULATION<br>(5:0)                                                    | Constellation<br>1: DVB-S2 QPSK<br>2: DVB-S2 8-PSK<br>3: DVB-S2 16-APSK<br>4: DVB-S2 32-APSK                                                                                               |

| STREAMS_<br>CODING(4:0)                                                            | Coding rate (LDPC code identifier)<br>0: rate 1/4 or 1/5<br>[normal,short,medium frames]<br>1: rate 1/3 [normal,short,medium                                                               |

| frames]                           |

|-----------------------------------|

| 2: rate 2/5 [normal,short frames] |

| 3: rate 1/2 [normal,short frames] |

| 4: rate 3/5 [normal,short frames] |

| 5: rate 2/3 [normal,short frames] |

| 6: rate 3/4 [normal,short frames] |

| 7: rate 4/5 [normal,short frames] |

| 8: rate 5/6 [normal,short frames] |

| 9: rate 8/9 [normal,short frames] |

| 10: rate 9/10 [normal frames]     |

| 11: rate 11/45 [short,medium      |

| frames]                           |

| 12: rate 4/15 [short frames]      |

| 13: rate 14/45 [short frames]     |

| 14: rate 7/15 [short frames]      |

| 15: rate 8/15 [short frames]      |

| 16: rate 26/45 [short frames]     |

| 17: rate 32/45 [short frames]     |

Note: when using the optional mode adaptation input interface, these configuration parameters are embedded within the 2-Byte transport header before each BBFRAME.

### I/Os

#### General

Two independent clock domains are used in *DVBS2\_TX.vhd*:

**CLK** for mode adaptation, BCH encoding, LDPC encoding and bit interleaving. These functions process 8-bit wide data samples.

**CLK\_TXg** for modulation and DAC sampling interface. Because the output interface is DDR, the actual DAC sampling rate is twice the **CLK\_TXg** frequency.

Of course, each clock timing period must be constrained in the constraint file (.xdc for Xilinx Vivado) associated with the project.

There is no need for inter-clock timing constraints between **CLK** and **CLK\_TXg**. (use set\_false\_path tcl command in the constraint file).

These two clocks must be global clocks (i.e. use BUFG before supplying the clock to the transmitter).

Two sync resets (SYNC\_RESET and

**SYNC\_RESET\_CLK\_TX**) must be supplied, one for each clock domain. The recommended use is to keep the resets high until both clocks are stable (i.e. PLL or MMCM locked).

#### Transmitter

| COM1808_TX DVB-S2 T<br>CLK<br>SYNC_RESET<br>CLK_TXg<br>SYNC_RESET_CLK_TX<br>DATA_IN<br>DATA_IN_VALID(N_TS-1:0)<br>SOF_IN INPUT<br>CDATA_IN_CTS STREAMS                                                             | DATA_I1_OUT(15:0)<br>DATA_I2_OUT(15:0)<br>DATA_Q1_OUT(15:0)<br>DATA_Q2_OUT(15:0) | <b>***</b> |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------|

| <ul> <li>STREAMS_TYPE</li> <li>STREAMS_UPL</li> <li>STREAMS_ISSYI</li> <li>STREAMS_NPD CONTROLS</li> <li>STREAMS_FL</li> <li>STREAMS_CODING</li> <li>STREAMS_MODULATION</li> <li>STREAMS_OTHER_CONTROLS</li> </ul> | MONITORING<br>MOD_SIGNAL_POWER<br>AWGN_POWER(23:0)<br>SATURATION(5:0)            | > > >      |

| <ul> <li>MAII_DATA_IN</li> <li>MAII_DATA_IN_VALID</li> <li>MAII_SOF_IN</li> <li>MAII_DATA_IN_CTS</li> </ul>                                                                                                        | ATION                                                                            |            |

| <ul> <li>MOD_SYMBOL_RATE(32:0)</li> <li>MOD_CENTER_FREQ(31:0)</li> <li>MOD_SIGNAL_SCALING(15:0)</li> <li>MOD_CONTROL(7:0)</li> <li>MOD_RO(2:0)</li> <li>AWGN_SCALING(15:0)</li> </ul>                              | MODULATION<br>CONTROLS                                                           |            |

#### Data Path

**DATA\_IN** is an array of **N\_TS** byte-wide input streams. Bit order: MSb first.

#### **DATA\_IN\_VALID(N\_TS-1:0)**: input.

1 CLK-wide pulses indicating that the associated **DATA\_IN** stream input Byte is valid.

**SOF\_IN(N\_TS-1:0)**: optional input Start Of Frame. 1 CLK-wide pulse. The SOF is aligned with **DATA\_IN\_VALID**. Required for transport streams and generic packetized streams.

#### **DATA\_IN\_CTS**: output.

Clear-To-Send flow control. '1' indicates that the transmitter is ready to accept another input byte. Thanks to an input elastic buffer, the data source is allowed to send a few more bytes after **DATA\_IN\_CTS** goes low, so timing is generally not critical.

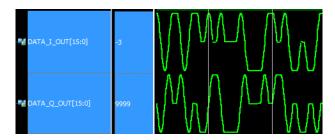

**DATA\_I/Q\_OUT(15:0)**: Modulated baseband output samples (I = in-phase, Q = quadrature). Double Data Rate output: two output samples every clock. Format: 2's complement (signed)

# Operations

### **Baseband Frame Assembly**

User packets are packed to completely fill the data field of the BBFRAME up to its kbch bit size. Thus, there is no need to add zero padding. The start of the data field is not necessarily aligned with the start of a user packet.

### **Multiple packetized streams**

The following rules are used to pack user packets into BBFRAMEs:

- a given BBFRAME contains user packets from a single stream only

- the stream multiplexer uses a round-robin method to assign a stream to the next BBFRAME, provided there is enough data in the stream buffer to fill the kbch bits of the next BBFRAME.

# Design considerations

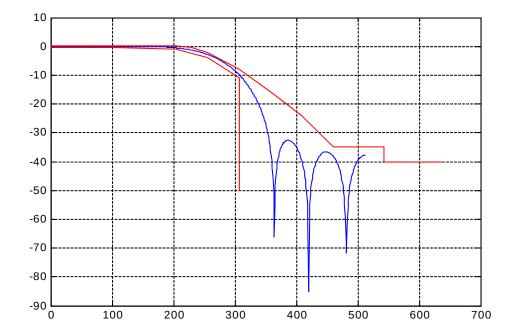

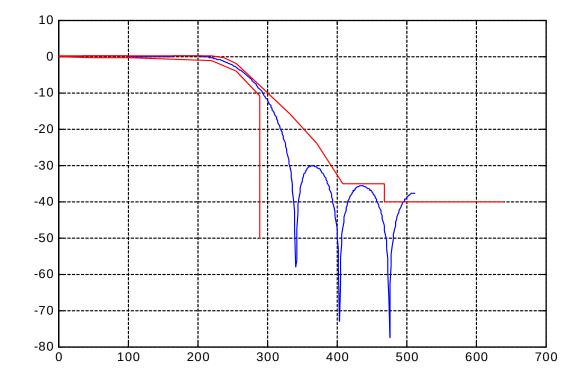

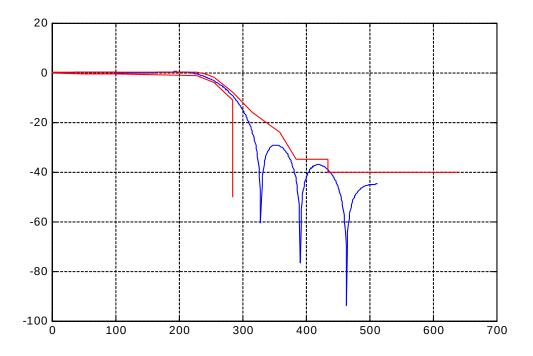

#### **Channel Filter**

The two parallel channel filters (processing the complex modulated samples) are implemented as 14-tap FIR filters. Compliance with the specified mask in [1] Appendix A is shown below. Note that some additional filter (either RF at the maximum symbol rate, or digital half-band filter at lower symbol rates are needed to guarantee low out-of-band levels).

$$Alpha = 0.35$$

The Matlab program <code>/matlab/dvbs2\_firrcos.m</code> is used to generate the FIR coefficients and verify compliance with the spectral mask

# Software Licensing

This software is supplied under the following key licensing terms:

- 1. A nonexclusive, nontransferable license to use the VHDL source code internally, and

- 2. An unlimited, royalty-free, nonexclusive transferable license to make and use products incorporating the licensed materials, solely in bit stream format, on a worldwide basis.

The complete VHDL/IP Software License Agreement can be downloaded from http://www.comblock.com/download/softwarelicense.pdf

# Portability

The VHDL source code is written in generic VHDL and thus can be ported FPGAs from various vendors.

# **Configuration Management**

The current software revision is 011224.

| Directory | Contents                                                                                                                                                                                   |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /doc      | Specifications, user manual, implementation documents                                                                                                                                      |

| /src      | .vhd source code,.pkg packages, .xdc<br>constraint files (Xilinx)<br>One component per file.                                                                                               |

| /sim      | VHDL test benches                                                                                                                                                                          |

| /matlab   | Gnuradio project and Matlab .m conversion<br>file for generating stimulus files for VHDL<br>simulation and for end-to-end BER<br>performance analysis at various signal to<br>noise ratios |

| /bin      | .bit configuration files (for use with<br>ComBlock COM-1800 FPGA development<br>platform)                                                                                                  |

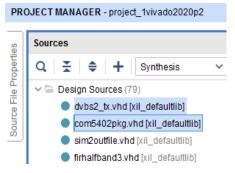

Project files:

Xilinx Vivado v2020 project files: project\_1vivado2020p2.xpr project\_1vivado2020p2.tcl

### VHDL development environment

The VHDL software was developed using the following development environment: Xilinx Vivado 2020 for synthesis, place and route and VHDL simulation

The entire transmitter project fits easily within a Xilinx Artix7-100T. Therefore, the ISE project can be processed using the free Xilinx WebPack tools.

### **Device Utilization Summary**

Transmitter device utilization (no AWGN) Device: Xilinx xcku5p-ffvb676-2-i

| Resource | Estimation | Available | Utilization |

|----------|------------|-----------|-------------|

| LUT      | 18145      | 216960    | 8.36        |

| LUTRAM   | 138        | 99840     | 0.14        |

| FF       | 10617      | 433920    | 2.45        |

| BRAM     | 32.50      | 480       | 6.77        |

| DSP      | 100        | 1824      | 5.48        |

| IO       | 273        | 280       | 97.50       |

| BUFG     | 2          | 256       | 0.78        |

## Clock and decoding speed

The entire design two global clocks CLK (encoding) and CLK\_TXg (modulation). Typical maximum clock frequencies for representative FPGA families are listed below:

| Device family                                   | Transmitter         |

|-------------------------------------------------|---------------------|

| Xilinx Kintex7<br>ultrascale+ -2 speed<br>grade | CLK_Txg:<br>318 MHz |

| grade                                           | CLK:                |

|                                                 | 345 MHz             |

# VHDL components overview Modulator top level

DVBS2\_TX(Behavioral) (dvbs2\_tx.vhd) (12)

- > LFSR11P\_001 : LFSR11P(behavior) (lfsr11p.vhd) (1)

- MODE\_ADAPTATION\_001 : MODE\_ADAPTATION(Behavioral) (mode

PRBS15\_8b\_001 : PRBS15\_8b(behavior) (prbs15\_8b.vhd)

- > BCHENC\_001 : BCHENCO(behavioral) (bchenco.vhd) (1)

- > OVBS2\_LDPC\_ENC\_001 : DVBS2\_LDPC\_ENC(behavioral) (dvbs2\_I

- > O X\_CLK\_DOMAINS\_NODATALOSS\_001 : CROSS\_CLK\_DOMAINS\_N

- > DVBS2\_INTERLEAVER\_001 : DVBS2\_INTERLEAVER(Behavioral) (c

- > DVBS2\_MODULATOR\_001 : DVBS2\_MODULATOR(Behavioral) (dvb

- > POWER\_MEASUREMENT\_001.POWER\_MEASUREMENT\_001 : PO'

- > POWER\_MEASUREMENT\_001.POWER\_MEASUREMENT\_002 : PO'

- > AWGN\_ON.AWGN\_001 : AWGN(behavior) (awgn.vhd) (46)

- > AWGN\_ON.POWER\_MEASUREMENT\_002b : POWER\_MEASUREM

*DVBS2\_TX.vhd* is the transmitter top level component. Inputs consist of one or several streams (transport, generic). The output is a DDR complex baseband modulated signal with two samples per CLK\_TXg clock. The maximum modulation rate is thus f<sub>elk TXg</sub> symbols/s.

The *MODE\_ADAPTATION.vhd* component implements [1] section 5.1, namely "Input Interfacing, Input Stream Synchronization (optional), Null-packet deletion (for TS input streams and ACM only), CRC-8 encoding for error detection (for packetized input streams only), input stream merging (for multiple input streams only) and input stream slicing in DATA FIELDs. Finally, base-band signaling is inserted, to notify the receiver of the adopted Mode Adaptation format. "

The *MODE\_ADAPTATION\_INPUT\_INTERFACE* component handles a Byte-stream input from an external mode adaptation block. It is instantiated when **EXT\_MODE\_ADAPT** is enabled. See [1] Annex I.2.

The *PRBS15\_8B.vhd* component generates the BB frame scrambling sequence.

*BCHENCO.vhd* is the BCH error correction encoding (outer coding), as per [1] section 5.3.1.

*SIGNED\_SIN\_COS\_TBL3.vhd* stores sine and cosine functions in ROM. It is used to convert phase to complex I/Q baseband output samples.

*COM1808\_TOP.vhd*: is mostly a use example when the DVBS2 transmitter is implemented on a ComBlock COM-1800 FPGA development platform.

Note for Xilinx Vivado: when creating the project, the compile order is unimportant, except for the two highlighted files which may require a higher priority:

#### Ancillary components

*LFSR11P.vhd* is a pseudo-random sequence generator used for test purposes. It generates a PRBS11 test sequence commonly used for bit error rate testing at the receiving end of a transmission channel.

*AWGN.vhd* generates a precise Additive White Gaussian Noise. The noise bandwidth is 2\*symbol rate.

*BRAM\_DP2.vhd* is a generic dual-port memory, used as input and output elastic buffers. Memory is inferred (no Xilinx primitive is used).

*INFILE2SIM.vhd* reads an input file. This component is used by the testbench to read a modulated samples file generated by the siggen\_fskl.m Matlab program for various Eb/No and frequency offset cases.

*SIM2OUTFILE.vhd* writes three 12-bit data variables to a tab delimited file which can be subsequently read by Matlab (load command) for plotting or analysis.

### VHDL simulation

VHDL testbenches are located in the /sim directory.

The tb\_dvbs2\_tx.vhd sends two transport streams through the transmitter to illustrate the streams multiplexing. The output consists of modulated complex baseband samples.

The tb\_dvbs2\_tx2.vhd sends a single DVBS2 generic packetized stream of length STREAMS\_UPL with variable coding and modulation (VCM): coding and modulation change frequently. The output consists of modulated complex baseband samples.

The tb\_dvbs2\_txrx.vhd connects the transmitter and receiver back to back for end-to-end VHDL simulation. It's use should be restricted to symbol rates below CLK\_TXg/8 as the coarse resampling between the CLK\_TXg transmitter sampling clock and CLK\_ADCg receiver sampling clock is too coarse for the higher symbol rates. The transmitter includes a built-in pseudo-random sequence generator and the receiver includes a built-in Bit Error Rate Tester.

### GNU radio + Matlab simulation

GNU radio project(s) and Matlab programs are located in the /matlab directory.

The dvbs2\_tx312MS.grc is a GNU radio configuration file to generate a DVB-S2 modulation waveform. It is used primarily to verify a receiver compliance with the DVB-S2 standard.

The read\_waveform.m program opens a *waveform.dat* complex samples file generated by GNU radio, reformats it to 2 columns of signed integers 12-bit precision then saves it to the input.txt file. It can also add white Gaussian noise to the waveform as needed.

The dvbs2\_firrcos.m matlab program helps selecting the minimum size FIR filter to comply with the standard spectral masks for various root raised cosine filter rolloff factors.

#### **Reference documents**

[1] DVB-S2 specifications, ETSI EN 302 307-1 V1.4.1 (2014-11)

[2] DVB-S2 Extensions (DVB-S2X) specifications ETSI EN 302 307-2 V1.1.1 (2015-02)

#### Acronyms

| Definition                      |

|---------------------------------|

| Adaptive Coding and Modulation  |

| Additive White Gaussian Noise   |

| Constant Coding and Modulation  |

| Clear-To-Send flow control flag |

| Dual Data Rate                  |

| Digital Video Broadcasting      |

| Field Programmable Gate Array   |

| Generic Stream                  |

| Gigabit Ethernet                |

| Least Significant bit in a word |

| Moving Pictures Experts Group   |

| Most Significant bit in a word  |

| Radio Frequency                 |

| Square Root Raised Cosine       |

| (filter)                        |

| Transport Stream                |

| Transmit                        |

| Variable Coding and Modulation  |

|                                 |

### **ComBlock Ordering Information**

COM-1808SOFT\_TX DVB-S2 transmitter, VHDL source code / IP core

ECCN: EAR99

### **Contact Information**

MSS • 845-N Quince Orchard Boulevard • Gaithersburg, Maryland 20878-1676 • U.S.A. Telephone: (240) 631-1111 E-mail: info@comblock.com