# Com Block

# COM-1827SOFT CPM Modulator VHDL source code overview / IP core

# Overview

The COM-1827SOFT CPM MOD is a Continuous Phase Modulator written in generic VHDL.

The entire **VHDL source code** is deliverable. It is portable to a variety of FPGA targets.

#### Key features and performance:

- CPM is a set of constant amplitude phase modulations well suited for operation through power amplifiers near saturation.

- Flexible programmable features:

- Symbol rate up to  $f_{clk}/4$ , where  $f_{clk}$  is the processing clock frequency.

- FSK, MSK, GFSK, GMSK, PCM/FM, SOQPSK-MIL and SOQPSK-TG

- Provided with IP core:

- VHDL source code

- Matlab .m file for generating stimulus files for comparison purposes.

- VHDL testbenches (back-to-back modem or stimulus file input)

- PRBS11 test sequence generator, AWGN noise generator

# Configuration

#### **Run-time configuration parameters**

The user can set and modify the following controls at run-time through the top level component interface:

| Modulator Parameters | Configuration                                                                                                                                                                                     |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYMBOL_RATE          | symbol rate expressed as<br>symbol_rate/ f <sub>clk</sub> * 2^32                                                                                                                                  |

| MODULATION_INDEX     | modulation index h.<br>unsigned fixed-point<br>format 4.12.                                                                                                                                       |

|                      | Typical values for h are 0.5 (0x0800),                                                                                                                                                            |

|                      | 0.7 (0x0B33)                                                                                                                                                                                      |

| GAIN                 | output amplitude scaling factor. 15-bit unsigned                                                                                                                                                  |

| CENTER_FREQ          | modulated signal center<br>frequency. Expressed as<br>fc/ f <sub>clk</sub> * 2^32                                                                                                                 |

| BURST_LENGTH         | A synchronization word is<br>inserted periodically<br>between frames (to<br>resolve any phase<br>ambiguity at the receiver).<br>This just includes the data<br>field, not the 32-bit<br>preamble. |

|                      | Constraint:<br>BURST_LENGTH is a<br>multiple of 8 bits.                                                                                                                                           |

|                      | composite limit:<br>preamble+sync+BURST_<br>LENGTH < 8191                                                                                                                                         |

| CONTROL | bits 2:0 modulation order<br>M = 3 for SOQPSK, 0<br>otherwise               |  |

|---------|-----------------------------------------------------------------------------|--|

|         | bits 7:4 frequency shaping filter selection                                 |  |

|         | 0 = FSK                                                                     |  |

|         | 1 = PCM/FM                                                                  |  |

|         | 2 = GMSK/GFSK BT=0.7                                                        |  |

|         | 3 = GMSK/GFSK BT=0.5                                                        |  |

|         | 4 = GMSK/GFSK BT=0.3                                                        |  |

|         | 5 = SOQPSK-MIL                                                              |  |

|         | 6 = SOQPSK-TG                                                               |  |

|         | 8 = GMSK/GFSK<br>BT=0.25                                                    |  |

|         | bits 9:8 test mode: 00 no<br>test, 01 = PRBS11, 11 =<br>unmodulated carrier |  |

|         | bit 10: always '1' to enable<br>sync word insertion                         |  |

|         | bit 11: spectrum<br>inversion. invert Q. on (1)<br>or off (0)               |  |

## I/Os

#### General

#### **CLK**: input

The synchronous clock. The user must provide a global clock (use BUFG). The CLK timing period must be constrained in the .xdc file associated with the project.

#### SYNC\_RESET: input

Synchronous reset. The reset MUST be exercised at least once to initialize the internal variables. It must be exercised whenever a control parameter is changed.

#### Modulator

| COM1827_TX CPM N                                                                                                                                                                         | IODULATOR                                                                              |                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------|

| <ul> <li>→ CLK</li> <li>→ SYNC_RESET</li> <li>→ TX_DATA(7:0)</li> <li>→ TX_DATA_SAMPLE_CLK</li> <li>→ TX_SOF</li> <li>INPUT</li> <li>← TX_CTS</li> <li>BITS</li> </ul>                   | DATA_I_OUT(15:0)<br>DATA_Q_OUT(15:0)<br>TX_EN_OUT<br>MODULATED<br>BASEBAND<br>WAVEFORM | $\rightarrow \rightarrow \rightarrow$ |

| <ul> <li>→ SYMBOL_RATE(31:0)</li> <li>→ MODULATION_INDEX(15:0)</li> <li>→ GAIN(15:0)</li> <li>→ CENTER_FREQUENCY(31:0)</li> <li>→ BURST_LENGTH(12:0)</li> <li>→ CONTROL(15:0)</li> </ul> | SATURATION<br>SYMBOL_CLKx4_OUT<br>MONITORING                                           | <b>→</b>                              |

|                                                                                                                                                                                          |                                                                                        |                                       |

**TX\_DATA(7:0)**: Input data byte. The MSb is sent first.

#### TX\_DATA\_SAMPLE\_CLK: input.

1 CLK-wide pulse indicating that TX\_DATA is valid.

**TX\_SOF**: optional input Start Of Frame. 1 CLKwide pulse. The SOF is aligned with **TX\_DATA\_SAMPLE\_CLK**.

#### TX\_CTS: output.

Clear-To-Send flow control. '1' indicates that the modulator is ready to accept another input byte. Thanks to an input elastic buffer, the data source is allowed to send a few more bytes after TX\_CTS goes low.

| к                | 1  |    |    |      |           |  |

|------------------|----|----|----|------|-----------|--|

| NC_RESET         | 0  |    |    |      |           |  |

| _DATA[7:0]       | 55 | 9a | 5a | X 8e | <u>55</u> |  |

| _DATA_SAMPLE_CLK | 1  |    |    |      |           |  |

| _SOF             | 1  |    |    |      |           |  |

| _cts             | 0  |    |    |      |           |  |

Modulator input flow control example

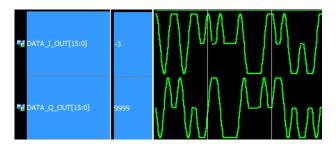

**DATA\_I/Q\_OUT(15:0)**: Modulated baseband output samples (I = in-phase, Q = quadrature). One output sample every clock. Format: 2's complement (signed)

**TX\_EN\_OUT**: goes low to turn off an external power amplifier when the modulator is not receiving any input data.

## Design considerations

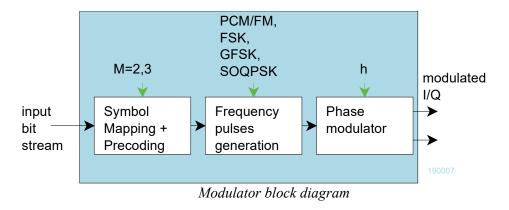

## Frequency pulse generation

An FIR filter shapes the frequency pulses. The FIR coefficients are stored in a lookup table, sampled at 4 samples/symbol. See CPM\_FILTERSx4.vhd. The table is large enough to store multiple frequency pulse shapes: rectangular pulse for MSK, Gaussian pulse for GMSK, raised cosine for PCM/FM, etc.

The Matlab program /matlab/siggen\_fsk1.m is used to generate the FIR coefficients.

# Performance

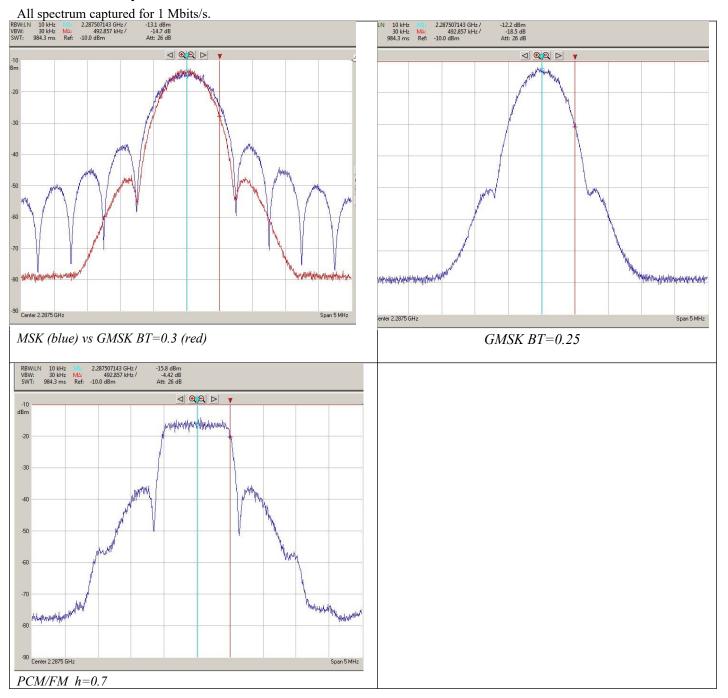

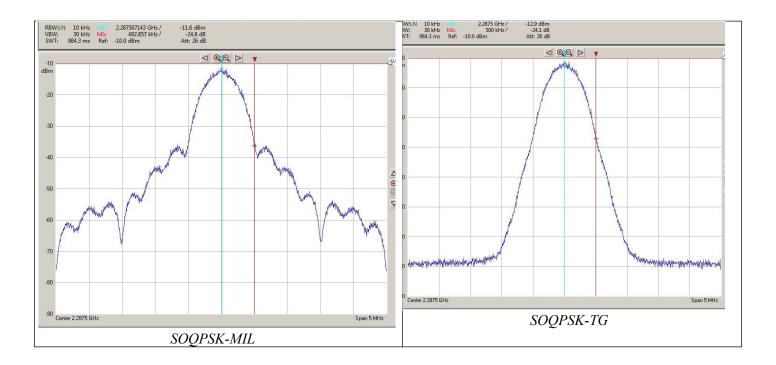

## **Transmitted spectrum**

# Software Licensing

This software is supplied under the following key licensing terms:

- 1. A nonexclusive, nontransferable license to use the VHDL source code internally, and

- 2. An unlimited, royalty-free, nonexclusive transferable license to make and use products incorporating the licensed materials, solely in bit stream format, on a worldwide basis.

The complete VHDL/IP Software License Agreement can be downloaded from http://www.comblock.com/download/softwarelicense.pdf

# Portability

The VHDL source code is written in generic VHDL and thus can be ported FPGAs from various vendors. See the limitation below.

# **Configuration Management**

The current software revision is 2a.

| Directory | Contents                                                                                                                                                |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| /doc      | Specifications, user manual, implementation documents                                                                                                   |

| /src      | .vhd source code,.pkg packages, .xdc<br>constraint files (Xilinx)<br>One component per file.                                                            |

| /sim      | VHDL test benches                                                                                                                                       |

| /matlab   | Matlab .m file for generating stimulus files<br>for VHDL simulation and for end-to-end<br>BER performance analysis at various signal<br>to noise ratios |

| /bin      | .bit configuration files (for use with<br>ComBlock COM-1800 FPGA development<br>platform)                                                               |

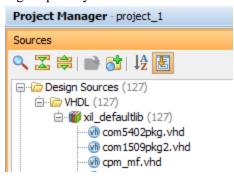

Project files:

Xilinx Vivado v2020 project file: project\_1.xpr

# VHDL development environment

The VHDL software was developed using the following development environment:

(a) Xilinx Vivado 2020 for synthesis, place and route and VHDL simulation

The entire project fits easily within a Xilinx Artix7-100T. Therefore, the ISE project can be processed using the free Xilinx WebPack tools.

# **Device Utilization Summary**

The modulator size is fixed (not parameterized).

| Modulator      |      | % of Xilinx<br>Artix7-<br>100T |

|----------------|------|--------------------------------|

| Registers      | 1868 | 1%                             |

| LUTs           | 2078 | 3%                             |

| Block RAM/FIFO | 10   | 7%                             |

| DSP48          | 11   | 4%                             |

| GCLKs          | 1    | 3.1%                           |

## Clock and decoding speed

The entire design uses a single global clock CLK. Typical maximum clock frequencies for various FPGA families are listed below:

| Device family                     | Modulator |

|-----------------------------------|-----------|

| Xilinx Artix 7 -1 speed grade     | 160 MHz   |

| Xilinx Kintex-7 -2<br>speed grade |           |

# Ready-to-use Hardware

The COM-1827SOFT was developed on, and therefore ready to use on the following commercial off-the-shelf hardware platform:

#### FPGA development platform

<u>COM-1800</u> FPGA (XC7A100T) + ARM + DDR3 SODIMM socket + GbE LAN development platform

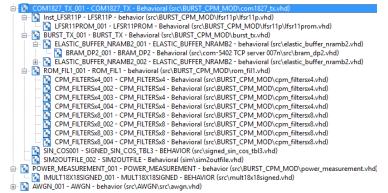

# VHDL components overview

#### Modulator top level

*COM1827\_TX.vhd* generates complex baseband continuous phase-modulated samples from byte-size input data.

The *BURST\_TX.vhd* component stores input data in an elastic input buffer, then packs input bits into symbols (1,2,3 bits/symbol) at the specified symbol rate. It also stops the transmitter when the input elastic buffer is empty.

*BRAM\_DP2.vhd* is a generic dual-port memory, used as input and output elastic buffers. Memory is inferred (no Xilinx primitive is used).

*ROM\_FIL1.vhd* implements an FIR filter to shape the frequency pulses. The FIR filter coefficients for various modulation schemes (Gaussian, raised cosine, etc) are stored in the *CPM\_FILTERSx4.vhd* ROM.

*SIGNED\_SIN\_COS\_TBL3.vhd* stores sine and cosine functions in ROM. It is used to convert phase to complex I/Q baseband output samples.

*COM1827\_TOP.vhd*: is mostly a use example when the CPM modem is implemented on a ComBlock COM-1800 FPGA development platform. Please note that this top component can't be simulated as it makes many references to other components outside the scope of the modem proper (TCP stack, turbo codec, etc)

Note for Xilinx Vivado: when creating the project, the file priority order is unimportant, except for the three packages below which must be placed with a higher priority order:

#### Ancillary components

*LFSR11P.vhd* is a pseudo-random sequence generator used for test purposes. It generates a PRBS11 test sequence commonly used for bit error rate testing at the receiving end of a transmission channel.

*AWGN.vhd* generates a precise Additive White Gaussian Noise. The noise bandwidth is 2\*symbol rate.

*INFILE2SIM.vhd* reads an input file. This component is used by the testbench to read a modulated samples file generated by the siggen\_fskl.m Matlab program for various Eb/No and frequency offset cases.

*SIM2OUTFILE.vhd* writes three 12-bit data variables to a tab delimited file which can be subsequently read by Matlab (load command) for plotting or analysis.

## VHDL simulation

VHDL testbenches are located in the /sim directory.

The tbcom1827\_modemonly.vhd connects the modulator and a demodulator back to back.

End-to-end BER tests can be performed as the com1827\_tx.vhd transmitter includes a built-in pseudo-random sequence generator and the com1827\_rx.vhd receiver includes a built-in Bit Error Rate Tester.

# Matlab simulation

Matlab programs are located in the /matlab directory.

The siggen\_fskl.m program generates a stimulus file input.txt for use as input to a demodulator VHDL simulation (tbcom1827\_demodonly.vhd). The stimulus file includes a continuous stream of pseudo-random (PRBS11) data bits, convolutional code encoding, continuous phase modulation, additive white Gaussian noise, channel filtering, frequency translation and quantization.

## **Specifications**

[1] IRIG-106 "Telemetry Standard RCC Document 106-07, Chapter 2", for SOQPSK TG

[2] MIL-STD-188-181B for SOQPSK-MIL

## **ComBlock Ordering Information**

COM-1827SOFT CPM modulator, VHDL source code / IP core

ECCN: EAR99

## **Contact Information**

MSS • 845-N Quince Orchard Boulevard • Gaithersburg, Maryland 20878-1676 • U.S.A. Telephone: (240) 631-1111 E-mail: info@comblock.com