# **COM-1827SOFT PCM/FM DEMODULATOR VHDL source code overview / IP core**

#### Overview

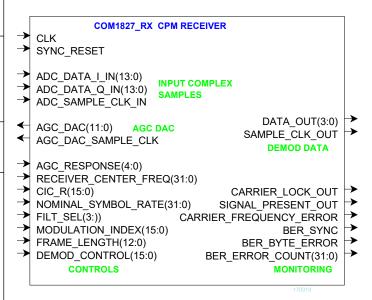

The COM-1827SOFT PCM/FM DEMOD is a PCM/FM demodulator- written in generic VHDL.

The entire **VHDL source code** is deliverable. It is portable to a variety of FPGA targets.

#### **Key features and performance:**

- PCM/FM is a constant envelope modulation well suited for operation through power amplifiers near saturation.

- Flexible programmable features:

- Nominal modulation index h [0.5 to 0.8]

- O Symbol rate up to  $\mathbf{f}_{elk}/4$ , where  $\mathbf{f}_{elk}$  is the processing clock frequency.

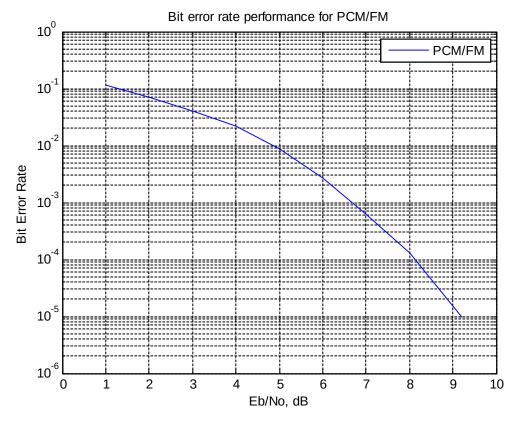

- Excellent BER performance using multisymbol detection and 4-state trellis decoding (SOVA). 4-bit soft-decision demodulator output for best FEC decoder performance.

- Performance:

- o BER < 10<sup>-5</sup> at 9.2dB Eb/No

- ±50ppm symbol timing tracking

- AFC for carrier frequency acquisition of 10% of symbol rate

- o Acquisition threshold < 2dB Eb/No

- Provided with IP core:

- VHDL source code

- Matlab .m file for generating stimulus files for VHDL simulation of the demodulator and for end-to-end BER performance analysis at various signal to noise ratios

- VHDL testbench (stimulus file input, or back-to-back modem when used in conjunction with the CPM modulator IP core)

- o BER tester

# Configuration

#### **Run-time configuration parameters**

The user can set and modify the following controls at run-time through the top level component interface:

| Interface:              |                                                                                                                                      |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Receiver Parameters     | Configuration                                                                                                                        |

| AGC_RESPONSE            | Adjust the AGC response time. approximately log2(NSymbols).                                                                          |

| RECEIVER_CENTER_FREQ    | nominal (i.e. expected)<br>center frequency.<br>Expressed as<br>fc/demodulator processing<br>clock * 2^32                            |

|                         | This frequency is subtracted from the input signal center frequency.                                                                 |

|                         | Add -fclk/4 when used in conjunction with IF undersampling.                                                                          |

| CIC_R                   | CIC Decimation ratio. The output sampling rate is thus fclk/R                                                                        |

|                         | 1 to bypass. 0 is illegal, otherwise, nominal range is 1 to 16384.                                                                   |

|                         | Usage: be careful not to decimate too much as the CIC decimation filter is not very sharp and thus can distort the modulated signal. |

|                         | Rule of thumb: the CIC filter output sampling rate should be > 4 samples per symbol.                                                 |

| NOMINAL_SYMBOL_<br>RATE | fsymbol rate / fclk * 2^32 = nominal symbol rate                                                                                     |

| M_SEL                   | modulation order M<br>selection. Always 0 for<br>PCM/FM                                                                              |

|                  | 0: M=2                                                                                                                                               |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| FILT_SEL         | Filter selection:                                                                                                                                    |  |

|                  | 1 = PCM/FM                                                                                                                                           |  |

| MODULATION_INDEX | modulation index h.<br>unsigned fixed-point<br>format 4.12.                                                                                          |  |

|                  | h is typically 0.7<br>(0x0B33) for PCM/FM                                                                                                            |  |

| FRAME_LENGTH     | Optional frame length,<br>including payload + 32-bit<br>sync word                                                                                    |  |

| DEMOD_CONTROL    | bit 0: spectrum inversion enabled(1)/disabled(0)                                                                                                     |  |

|                  | bit 1: AFC enabled(1)/disabled(0).                                                                                                                   |  |

|                  | bit 2: freeze AGC                                                                                                                                    |  |

|                  | bit 3: optional sync word<br>detection enabled<br>(1)/disabled(0)                                                                                    |  |

|                  | bit 4: FFT : always<br>disabled (0) for PCM/FM                                                                                                       |  |

|                  | bit 5: enable(1)/disable(0)<br>sync word removal at<br>output. Generally remove,<br>except when another sync<br>detection follows after the<br>demod |  |

#### I/Os

#### General

**CLK**: input

The synchronous clock. The user must provide a global clock (use BUFG). The CLK timing period must be constrained in the .xdc file associated with the project.

#### **SYNC RESET**: input

Synchronous reset. The reset MUST be exercised at least once to initialize the internal variables. It must be exercised whenever a control parameter is changed.

#### Receiver

ADC\_DATA\_I/Q\_IN(13:0): input samples from one or two external ADCs. (one in the case of IF undersampling, two for near-zero frequency complex inputs). If the ADCs have fewer than 14-bit precision, align the most significant bit with ADC\_DATA\_IN(13). Format: 2's complement (signed).

AGC\_DAC(11:0): output to an external DAC to control an external AGC. Read when AGC\_DAC\_SAMPLE\_CLK is '1'

**DATA\_OUT(3:0)**: soft-decision output. The demodulated bit is bit 3. The three lower bits indicate the level of confidence: "0000" for a solid '0', "1111" for a solid '1', "1000" for a '1' barely above the thresold.

## Design considerations

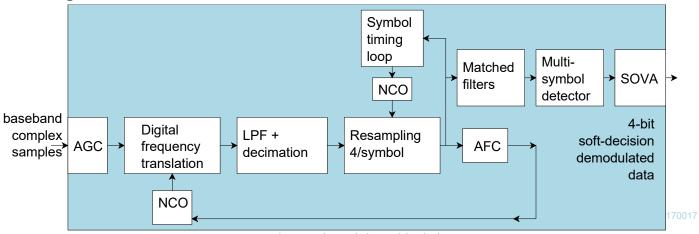

Non-coherent demodulator block diagram

# Modulated signal key properties

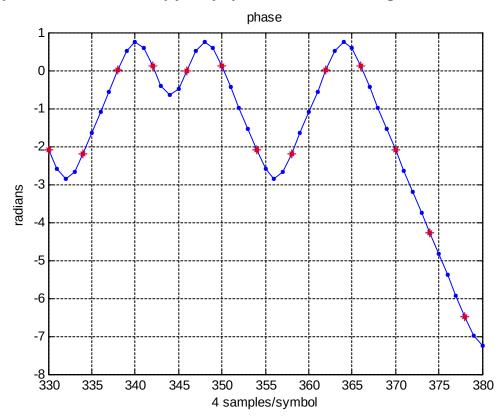

The plot below illustrates the key phase properties of the modulated signal:

- 1. Symbol centers are shown as red \*.

- 2. The phase change from one symbol center to another is close to 0, h\*pi or -h\*pi.

These properties are the basis for the following demodulator algorithm:

- 1. matched filters are computed over one symbol period spanning from one symbol center to the next.

- 2. This symbol period is associated with two data bits (since L=2)

- 3. Four matched filters are computed over each symbol, for the data hypothesis 00,01,10,11.

These four hypothesis represent the four states in the trellis diagram.

## **Multi-Symbol detection**

The matched filters are coherently accumulated. Each new set of four matched filters outputs is summed coherently (complex sum) with the previous set of accumulated values rotated by 0,+pi\*h,-pi\*h according to the 8 branches of the trellis diagram. The set of 8 accumulated values is reduced to four by selecting the ones with the largest magnitude for each state. The accumulated values are scales by 0.5 at each symbol to ensure stability of the algorithm.

A 4-state trellis decoding follows the multi-symbol detection. The 8 branch metrics are the magnitude of the accumulated values.

## **Performance**

#### BER vs Eb/No

The plot below shows near-theoretical performance for the PCM/FM demodulator without error correction.

# Software Licensing

This software is supplied under the following key licensing terms:

- 1. A nonexclusive, nontransferable license to use the VHDL source code internally, and

- 2. An unlimited, royalty-free, nonexclusive transferable license to make and use products incorporating the licensed materials, solely in bit stream format, on a worldwide basis.

The complete VHDL/IP Software License Agreement can be downloaded from <a href="http://www.comblock.com/download/softwarelicense.pdf">http://www.comblock.com/download/softwarelicense.pdf</a>

# **Portability**

The VHDL source code is written in generic VHDL and thus can be ported FPGAs from various vendors.

# Configuration Management

The current software revision is 1c.

| Directory | Contents                                                                                                                                       |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|

| /doc      | Specifications, user manual, implementation documents                                                                                          |

| /src      | .vhd source code,.pkg packages, .xdc<br>constraint files (Xilinx)<br>One component per file.                                                   |

| /sim      | VHDL test benches                                                                                                                              |

| /matlab   | Matlab .m file for generating stimulus files for VHDL simulation and for end-to-end BER performance analysis at various signal to noise ratios |

| /bin      | .bit configuration files (for use with ComBlock COM-1800 FPGA development platform)                                                            |

Project files:

Xilinx ISE 14 project file: com-1827.xise Xilinx Vivado v2015.2 project file: project\_1.xpr

# VHDL development environment

The VHDL software was developed using the following development environment:

- (a) Xilinx ISE 14.7 for synthesis, place and route

- (b) Xilinx Vivado 2015.2 for synthesis, place and route and VHDL simulation

The entire project fits easily within a Xilinx Artix7-100T. Therefore, the ISE project can be processed using the free Xilinx WebPack tools.

## **Device Utilization Summary**

The encoder size is fixed (not parameterized).

Device: Xilinx Artix7-100T

| Device. Allina Altia/-1001       |       |                                |  |  |

|----------------------------------|-------|--------------------------------|--|--|

| Receiver 4-bit soft-quantization |       | % of Xilinx<br>Artix7-<br>100T |  |  |

| Registers                        | 10171 | 8%                             |  |  |

| LUTs                             | 13614 | 21%                            |  |  |

| Block RAM/FIFO                   | 9     | 6%                             |  |  |

| DSP48                            | 69    | 28%                            |  |  |

| GCLKs                            | 3     | 9%                             |  |  |

## Clock and decoding speed

The entire design uses a single global clock CLK. Typical maximum clock frequencies for various FPGA families are listed below:

| Device family                  | Demodulator |

|--------------------------------|-------------|

| Xilinx Artix 7 -1 speed grade  | 160 MHz     |

| Xilinx Kintex-7 -2 speed grade |             |

# Ready-to-use Hardware

The COM-1827SOFT was developed on, and therefore ready to use on the following commercial off-the-shelf hardware platform:

#### FPGA development platform

COM-1800 FPGA (XC7A100T) + ARM + DDR3 SODIMM socket + GbE LAN development platform

# VHDL components overview Receiver top level

The receiver is comprised of two high-level components:

RECEIVER1.vhd performs non modulationspecific tasks such as AGC, DC bias removal, frequency translation to baseband, anti-aliasing filtering and decimation.

```

RECEIVER 001 - RECEIVER1B - Behavioral (src\CPM_DEMOD\receiver1b.vhd)

| Inst_AGC17 - AGC17 - behavioral (src\CPM_DEMOD\agc17.vhd)

| Inst_SIM2OUTFILE - SIM2OUTFILE - Behavioral (sim\sim2outfile.vhd)

| AGC21_001 - AGC21 - behavioral (src\CPM_DEMOD\agc21.vhd)

| Inst_SIM2OUTFILE - SIM2OUTFILE - Behavioral (sim\sim2outfile.vhd)

| AGC21_001 - AGC21 - behavioral (src\CPM_DEMOD\agc21.vhd)

| Inst_SIM2OUTFILE - SIM2OUTFILE - Behavioral (src\com-5402 TCP server 007n\src\timer_4us

| Inst_SIM2OUTFILE - BEHAVIOR (src\com-5402 TCP server 007n\src\timer_4us

| Inst_SIM2OUTFILE - BEHAVIOR (src\com-5402 TCP server 007n\src\timer_4us

| Inst_SIM2OUTFILE - BEHAVIOR (src\timer_4us

| Inst_SIM2OUTFILE - B

```

CPM\_DEMOD.vhd performs the continuous phase demodulation, including symbol timing tracking, AGC, matched filtering, multi-symbol detection and trellis decoding.

```

🖮 😘 AGC18_000 - AGC18 - behavioral (src\CPM_DEMOD\agc18.vhd)

POLAR3_001 - POLAR3 - Behavior (src\CPM_DEMOD\polar3\POLAR3.vhd)

POLAR3PHASEPROM_001 - POLAR3PHASEPROM - Behavioral (src\CPM_DEMOL

POLAR3MAGPROM_001 - POLAR3MAGPROM - Behavioral (src\CPM_DEMOD\pc

ONEOVERX 001 - DIVIDER - behavioral (src\divider.vhd)

INTERNAL_AGC_002 - MULT18X18SIGNED - BEHAVIOR (src\mult18x18signed.vhd)

SIN_COSOUT - DIGITAL_DC3 - DIGITAL_DC_ARCH (src\mult18x18signed.vhd)

SIN_COSOUT - SIGNED_SIN_COS_TBL3 - BEHAVIOR (src\signed_sin_cos_tbl3.vhd)

MULT1 - MULT18X18SIGNED - BEHAVIOR (src\mult18x18signed.vhd)

MULT2 - MULT18X18SIGNED - BEHAVIOR (src\mult18x18signed.vhd)

MULT3 - MULT18X18SIGNED - BEHAVIOR (src\mult18x18signed.vhd)

MULT4 - MULT18X18SIGNED - BEHAVIOR (src\mult18x18signed.vhd)

INTERNAL_AGC_003 - MULT18X18SIGNED - BEHAVIOR (src\mult18x18signed.vhd)

🖆 😘 DIGITAL_DC3_001 - DIGITAL_DC3 - DIGITAL_DC_ARCH (src\digital_dc3.vhd)

RESAMPLING31_001 - RESAMPLING31 - behavioral (src\CPM_DEMOD\resampling31.vhc

FREQUENCY_DETECTION_001 - FAST_FREQUENCY_DETECTION - Behavioral (src\C

FFT_CONTROL2_001 - FFT_CONTROL2 - BEHAVIOR (src\CPM_DEMOD\fast_frequence

BRAM2_18Kb_001 - BRAM_DP2 - Behavioral (src\com-7003\src\bram_dp2.vhd)

BRAM2_18Kb_002 - BRAM_DP2 - Behavioral (src\com-7003\src\bram_dp2.vhd)

BRAM2_18Kb_003 - BRAM_DP2 - Behavioral (src\com-7003\src\bram_dp2.vhd)

BRAM2_18Kb_004 - BRAM_DP2 - Behavioral (src\com-7003\src\bram_dp2.vhd)

BRAM2_18Kb_005 - BRAM_DP2 - Behavioral (src\com-7003\src\bram_dp2.vhd)

BRAM2_18Kb_005 - BRAM_DP2 - Behavioral (src\com-7003\src\bram_dp2.vhd)

BRAM2\_18Kb\_006 - BRAM\_DP2 - Behavioral (src\com-7003\src\bram\_dp2.vhd)

BRAM2_18Kb_007 - BRAM_DP2 - Behavioral (src\com-7003\src\bram_dp2.vhd)

BRAM2_18Kb_008 - BRAM_DP2 - Behavioral (src\com-7003\src\bram_dp2.vhd)

FFT_COEFF_001 - FFT_COEFF - BEHAVIOR (src\CPM_DEMOD\fast_frequency_det

SIGNED_SIN_COS_TBL3_001 - SIGNED_SIN_COS_TBL3 - BEHAVIOR (src\signec

SIGNED_SIN_COS_TBL3_002 - SIGNED_SIN_COS_TBL3 - BEHAVIOR (src\signec

FFT_RADIX2_4_001 - FFT_RADIX2_4 - BEHAVIOR (src\CPM_DEMOD\fast_frequence

MULT_001 - MULT18X18SIGNED - BEHAVIOR (src\mult18x18signed.vhd)

MULT_002 - MULT18X18SIGNED - BEHAVIOR (src\mult18x18signed.vhd)

MULT_003 - MULT18X18SIGNED - BEHAVIOR (src\mult18x18signed.vhd)

MULT_004 - MULT18X18SIGNED - BEHAVIOR (src\mult18x18signed.vhd)

MULT_005 - MULT18X18SIGNED - BEHAVIOR (src\mult18x18signed.vhd)

MULT_006 - MULT18X18SIGNED - BEHAVIOR (src\mult18x18signed.vhd)

➡ POLAR3 002a - POLAR3 - Behavior (src\CPM DEMOD\polar3\POLAR3.vhd)

```

## **Ancillary components**

LFSR11P.vhd is a pseudo-random sequence generator used for test purposes. It generates a PRBS11 test sequence commonly used for bit error rate testing at the receiving end of a transmission channel.

BER2.vhd is a bit error rate tester expecting to receive a PRBS11 test sequence. It synchronizes with the received bit stream and count errors over a 80,000 bit window.

```

BER2_001 - BER2 - behavioral (src\BER2\ber2\vhd)

MATCHED_FILTER4x8_001 - MATCHED_FILTER4x8 - behavioral (src\BER2\matched_filter4x8.vhd)

SOF_TRACK8_001 - SOF_TRACK8 - BEHAVIOR (src\BER2\sof_track8.vhd)

Inst_PC_16 - PC_16 - BEHAVIOR (src\BER2\PC_16.vhd)

```

AWGN.vhd generates a precise Additive White Gaussian Noise. The noise bandwidth is 2\*symbol rate.

INFILE2SIM.vhd reads an input file. This component is used by the testbench to read a modulated samples file generated by the siggen\_fskl.m Matlab program for various Eb/No and frequency offset cases.

SIM2OUTFILE.vhd writes three 12-bit data variables to a tab delimited file which can be subsequently read by Matlab (load command) for plotting or analysis.

#### VHDL simulation

VHDL testbenches are located in the /sim directory.

com1827\_rx.vhd receiver includes a built-in Bit Error Rate Tester.

The tbcom1827\_demodonly.vhd testbench reads a tab-delimited stimulus files of modulated I/Q baseband complex input samples.

#### Matlab simulation

Matlab programs are located in the /matlab directory.

The siggen\_fsk1.m program generates a stimulus file input.txt for use as input to either the demodulator VHDL simulation (tbcom1827\_demodonly.vhd) or the demod\_pcmfm\_baseline.m Matlab program. The stimulus file includes a continuous stream of pseudo-random (PRBS11) data bits, convolutional code encoding, PCM/FM modulation, additive white Gaussian noise, channel filtering, frequency translation and quantization.

Care must be taken to match the modulator configuration in siggen\_fsk1.m and the demodulator configuration in tbcom1827 demodonly.vhd.

This setup allows end-to-end BER testing, as the demodulator com1827\_rx.vhd includes a built-in bit error rate tester.

The demod\_pcmfm.m program applies key demodulation techniques to the stimulus file input.txt and computes the BER. It does not include AFC, AGC and symbol timing tracking loops.

#### Reference documents

[1] http://www.ijeeee.org/Papers/307-A0021.pdf

## Implementation Overview

#### Symbol tracking loop

The loop is designed to acquire and track symbol timing errors of +/-50ppm for SNR of 0dB or above.

The algorithm first computes the phase difference between two successive complex samples at 4 x the sampling rate. The phase difference is analoguous to a frequency. One sample is used to de-rotate the following sample. The resulting I value (FREQ2 in the code) is proportional to the phase difference between these two complex samples.

The symbol tracking loop is a first order Gardner loop. It finds the center of the FREQ2 symbols, and by way of consequence the zero crossing point as well.

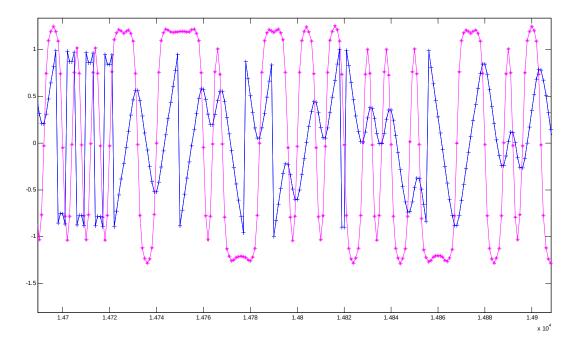

Blue trace = phase of received complex baseband samples (in radians). PCM/FM case, h=0.7, noiseless.

Y axis scale: 1 = pi Purple trace = FREQ2.

There are several delays between the *RESAMPLING3.vhd* and *the SYMBOL\_TIMING\_LOOP5.vhd* components worth noting:

- 1. the FREQ2 signal lags the actual received baseband signal by 1.5/4 symbol. This is clearly visible in the above plot.

- 2. the FREQ3 signal seen by the symbol tracking loop lags the actual received baseband signal by 1/2 symbol.

- 3. the *FIRHALFBAND3.vhd* filters used to reduce the noise power prior to symbol tracking, introduce a group delay of 10 samples = 2.5 symbols.

Both delays are compensated for in the code.

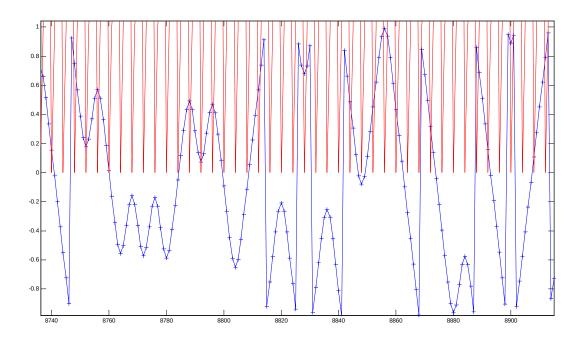

Verification: when the symbol timing loop is tracking properly, the SYMBOL3\_CLK is aligned with the peak phase of the complex DATA3 X baseband signal.

Blue trace: phase/pi of complex DATA3\_I/DATA3\_Q signal after frequency down-conversion and resampling at 4x symbol rate.

Red trace: SYMBOL3 CLK

### **Matched filter**

For implementation simplicity, the matched filter is computed in two steps:

- 1. A partial correlation over one symbol period is computed: the received complex baseband signal is correlated with the conjugate of the expected (ideal) signal over one symbol period. The phase of the expected signal over one symbol period is stored in a lookup table CPM\_PHASEx4.vhd. The stored phase is sampled at four samples/symbol, just like the received signal. For different phase waveforms are stored, one for each received symbol hypothesis, since the modulator filter spans L=2 symbols.

- 2. A multi-symbol detector extends the correlation over a 3-symbol period. Over a period of 3 symbols, there are 16 possible symbol hypothesis. The partial correlations are rotated and summed accordingly. The highest magnitude indicates the most likely symbols sequence. The 16 magnitude values are used as branch metrics for the subsequent 8-state trellis decoding.

Matched filter phases are stored in CPM\_PHASEx4.vhd

Partial matched filter is computed in CPM\_MF.vhd

The multi-symbol detection: CPM MSD3.vhd

#### **AFC**

The demodulator comprises an automatic frequency control (AFC) loop to acquire and track the residual frequency offset of the modulated signal. See *afc2.vhd* component.

The algorithm follows the one described in document [1].

- 1. take two complex baseband samples separated by one symbol. These samples are taken after frequency correction.

- 2. One sample is used to de-rotate the other sample. The resulting I value (FREQ1 in the code) is proportional to the phase difference between these two samples.

Most of the changes are due to the actual modulation. However, any frequency error will generate a bias.

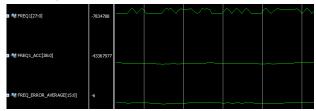

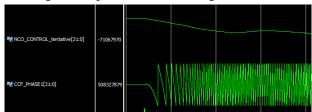

3. Average FREQ1 over 1024 symbols, as a way to remove most of the modulation since bits are expected to be randomly distributed between 0s and 1s.

4. The average is accumulated to create the NCO control value, after appropriate scaling. The AFC rate of convergence depends on the scaling.

Some ripple is expected in the NCO control value because of imbalances in the data stream (show is a PRBS11 test sequence with slightly unequal numbers of 0s and 1s.)

# **ComBlock Ordering Information**

COM-1827SOFT PCM/FM DEMOD, VHDL source code / IP core

#### **Contact Information**

MSS • 845-N Quince Orchard Boulevard • Gaithersburg, Maryland 20878-1676 • U.S.A.

Telephone: (240) 631-1111 E-mail: info@comblock.com