# COM-1852SOFT CCSDS Proximity-1 Modem VHDL source code overview / IP core

## Overview

The COM-1852SOFT is a proximity space-link modem for short-range, bi-directional, fixed or mobile radio links, generally used to communicate among probes, landers, rovers, orbiting constellations, and orbiting relays. The modem is fully compliant with the PROXIMITY-1 CCSDS standard [1].

More generally, this IP core is a fairly generic PCM/Bi-Phase L/Phase Modulation modem.

The IP core is intended for implementation in FPGA, SoC or ASIC. It is written in generic portable VHDL.

The entire **VHDL source code** is deliverable. It is portable to a variety of FPGA targets.

This IP core is available as transmitter-only, receiver-only or bundled tx/rx.

#### **Key Features**

- PCM/Bi-Phase L/phase modulation modem, 60 deg.

- Programmable symbol rate from 1KS/s to 4096 KS/s

- Large 160 KHz (two-sided) frequency acquisition and tracking.

- Large 1000ppm symbol rate acquisition range

- Tracking threshold  $E_b/N_0 = 0 \text{ dB}$

- Built-in tools: PRBS-11 pseudo-random test sequence, BER tester, AWGN generator, internal loopback mode, carrier frequency error measurement.

#### CCSDS standard compliance

| CCSDS standard compliance                                                                                                                          |                                                                                                                                  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|

| Key parameters                                                                                                                                     | CCSDS reference                                                                                                                  |  |

| Modulation:<br>Bi-phase L coding<br>60° phase modulation                                                                                           | [1] Section 3.3.4                                                                                                                |  |

| Coded symbol rates R <sub>cs</sub> :<br>1000, 2000, 4000, 8000,<br>16000, 32000, 64000,<br>128000, 256000, 512000,<br>1024000, 2048000,<br>4096000 | <ul> <li>[1] Section 3.3.6.1</li> <li>*ADC sampling rate<br/>must be strictly greater<br/>than 4*symbol rate +<br/>1%</li> </ul> |  |

| Channel symbol rate $R_{cs}$ is 2 * $R_{cs}$                                                                                                       |                                                                                                                                  |  |

| Discrete spurious spectral<br>lines in tx spectrum:<br>< 30 dBc below 2* R <sub>chs</sub><br>< -60 dBc above 20* R <sub>cs</sub>                   | [1] Section 3.4.4                                                                                                                |  |

| Receiver frequency<br>acquisition window (two-<br>sided):<br>160 KHz (includes<br>maximum Doppler + RF<br>synthesizer drifts)                      | [1] Section 3.4.5.1<br>+ extension from 10<br>KHz to 160 KHz                                                                     |  |

| Receiver tracking                                                                                                                                  | +-160 KHz                                                                                                                        |  |

| Doppler rate: 200 Hz/s max                                                                                                                         | [1] Section 3.4.5.1                                                                                                              |  |

| Channel symbol rate<br>offset<br>< 50ppm without idle<br>sequence<br>< 1% with at least 3200-<br>bit long idle sequence                            | [1] Section 3.3.6.3                                                                                                              |  |

## Portable VHDL code

The code is written in generic standard VHDL and is thus portable to a variety of FPGAs. The code was developed on a Xilinx 7-series FPGA but is expected to work similarly on other targets. No manufacturer-specific primitive is used.

MSS • 845 Quince Orchard Boulevard Ste N • Gaithersburg, Maryland 20878-1676 • U.S.A. Telephone: (240) 631-1111 www.ComBlock.com © MSS 2024 Issued 1/24/2024

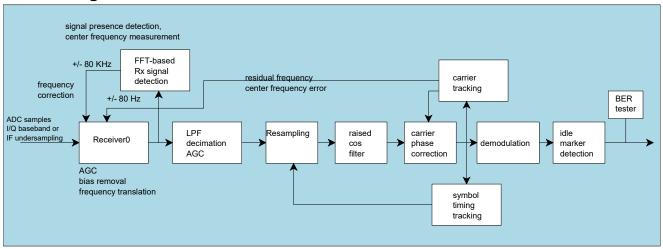

# Block Diagram

receiver block diagram

## Configuration

# Pre-Synthesis configuration parameters

The following constants are user-defined in the component generic section prior to synthesis. These parameters generally affect the size of the embodiment.

| Synthesis-time configuration parameters |                                                                                                                                                                        |  |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Proximity-1 transmitter                 |                                                                                                                                                                        |  |

| AWGN_EN                                 | 'l' to instantiate an<br>Additive White Gaussian<br>Noise generator.<br>'0' during operational<br>conditions to save space<br>in FPGA (and to increase<br>clock speed) |  |

| Proximity-1 receiver                    |                                                                                                                                                                        |  |

| FREQ_ACQUISITION_<br>RANGE              | Maximum detectable<br>center frequency error.<br>In Hz. (one-sided)                                                                                                    |  |

| CLK_FREQUENCY                           | Synchronous CLK<br>frequency in Hz                                                                                                                                     |  |

| BER_INST                                | '1' to instantiate a Bit<br>Error Rate Tester.                                                                                                                         |  |

| SIMULATION                              | true during simulation, false for synthesis.                                                                                                                           |  |

## Runtime dynamic configuration

The transmitter and receiver can be configured dynamically at runtime, in parallel (using the VHDL components input parameters).

The top-level components for parallel (I/O) configuration are: *COM1852\_TX.vhd COM1852\_RX.vhd*

## **Control registers (Receiver)**

**SIGNAL** designates the I/O signal when configuring the VHDL component directly at its interface.

$\mathbf{f}_{clk}$  is the ADC sampling frequency

| Demodulator               | •                                                                                |

|---------------------------|----------------------------------------------------------------------------------|

| (controls mus             | t be synchronous with CLK)                                                       |

| Parameters                | Configuration                                                                    |

| Nominal                   | The nominal center frequency is a fixed                                          |

| input center              | frequency offset applied to the input                                            |

| frequency                 | samples. It is used for fine frequency                                           |

| ( <b>f</b> <sub>c</sub> ) | corrections, for example to correct clock                                        |

|                           | drifts.                                                                          |

|                           | 32-bit signed integer (2's complement                                            |

|                           | representation) expressed as                                                     |

|                           | $f_{c} * 2^{32} / f_{clk}$                                                       |

|                           | DECENTED CENTED EDEC(21.0)                                                       |

|                           | RECEIVER CENTER FREQ(31:0)                                                       |

| Nominal                   | Nominal symbol rate, defined as $x^{32}$                                         |

| symbol rate               | $\mathbf{f}_{symbol}$ rate * $2^{32}$ / $\mathbf{f}_{clk}$                       |

| f <sub>symbol_rate</sub>  | Clarification: this is the symbol rate after                                     |

|                           | Bi-Phase L decoding, i.e. data symbol                                            |

|                           | rate.                                                                            |

| External                  | NOMINAL_SYMBOL_RATE(31:0)                                                        |

| AGC                       | Users can to optimize AGC response time while avoiding instabilities (depends on |

| response time             |                                                                                  |

| response unie             | external factors such as gain signal                                             |

|                           | filtering at the RF front-end and                                                |

|                           | modulation symbol rate). The AGC_DAC                                             |

|                           | gain control signal is updated as follows                                        |

|                           | 0 = every symbol,                                                                |

|                           | 1 = every 2 input symbols,                                                       |

|                           | 2 = every 4 input symbols,<br>3 = every 8 input symbols, etc                     |

|                           | 10 = every 1000 input symbols.                                                   |

|                           | Valid range 0 to 14.                                                             |

|                           | valid lange 0 to 14.                                                             |

|                           | AGC_RESPONSE(4:0)                                                                |

| CIC_R                     | Receiver decimation factor from $f_{clk}$ to                                     |

|                           | f <sub>clk</sub> /R                                                              |

|                           |                                                                                  |

|                           | 1 to bypass. 0 is illegal, otherwise,                                            |

|                           | nominal range is 1 to 16384.                                                     |

|                           | Usage: be careful not to decimate too                                            |

|                           | much as the CIC decimation filter is not                                         |

|                           | very sharp and thus can distort the                                              |

|                           | modulated signal.                                                                |

|                           | Rule of thumb: the CIC filter output                                             |

|                           | sampling rate should be $> 8$ samples per                                        |

|                           | data symbol.                                                                     |

|                           | CIC R(15:0)                                                                      |

| Spectrum                  | Invert Q bit                                                                     |

| inversion                 | 0 = off                                                                          |

|                           | 1 = on                                                                           |

|                           | DEMOD_CONTROL(0)                                                                 |

| L                         |                                                                                  |

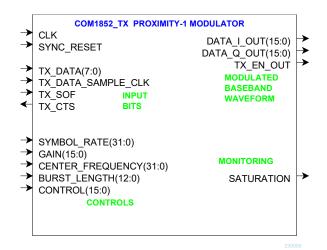

# Control registers (Transmitter)

| Modulator                                             |                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                       | t be synchronous with CLK)                                                                                                                                                                                                                                                                                                                                                                      |

| Parameters                                            | Configuration                                                                                                                                                                                                                                                                                                                                                                                   |

| Symbol rate<br>f <sub>symbol_rate</sub>               | Nominal symbol rate, defined as $f_{symbol rate} * 2^{32} / f_{clk}$<br>Clarification: this is the data symbol rate before Bi-Phase L encoding.                                                                                                                                                                                                                                                 |

|                                                       | SYMBOL_RATE(31:0)                                                                                                                                                                                                                                                                                                                                                                               |

| Output<br>Center<br>frequency<br>(f <sub>c_tx</sub> ) | Fine tuning of center frequency. Typically<br>0 Hz.<br>32-bit signed integer (2's complement<br>representation) expressed as<br>$f_{c_tx} * 2^{32} / f_{clk}$<br>For a clean output waveform, we<br>recommend keeping the maximum<br>frequency (center frequency + ½ symbol<br>rate) below 1/10 <sup>th</sup> of the processing clock<br>$f_{clk}$ .<br>Note: as the AWGN noise samples are not |

|                                                       | frequency translated, noise tests should<br>only be performed while the center<br>frequency translation is smaller than the<br>modulation bandwidth.                                                                                                                                                                                                                                            |

|                                                       | CENTER_FREQ(31:0)                                                                                                                                                                                                                                                                                                                                                                               |

| Digital<br>Signal gain                                | 16-bit amplitude scaling factor for the<br>modulated signal.<br>The maximum level should be adjusted to<br>prevent saturation. The settings may vary<br>slightly with the selected symbol rate.<br>Therefore, we recommend <u>checking for</u><br><u>saturation at the D/A converter</u> when<br>changing either the symbol rate or the signal<br>gain.                                         |

|                                                       | GAIN(15:0)                                                                                                                                                                                                                                                                                                                                                                                      |

| Additive<br>White<br>Gaussian<br>Noise gain           | 16-bit amplitude scaling factor for additive<br>white Gaussian noise.<br>Because of the potential for saturation,<br>please <u>check for saturation at the D/A</u><br><u>converter</u> when changing this parameter.                                                                                                                                                                            |

| Spectrum<br>inversion                                 | NOISE_GAIN(15:0)<br>Invert Q bit. (Inverts the modulated<br>spectrum only, not the subsequent frequency<br>translation)<br>0 = off<br>1 = on                                                                                                                                                                                                                                                    |

|                                                       | CONTROL(11)                                                                                                                                                                                                                                                                                                                                                                                     |

| Test mode | 00 = input is user data<br>01 = internal PRBS-11 test mode |

|-----------|------------------------------------------------------------|

|           | 10 = unmodulated carrier test mode                         |

CONTROL(9:8)

# Status registers (Receiver)

| Demodulator<br>(synchronous with CLK)                                                                                                                                                                                                                                                   |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| '1' when the receiver is locked to the<br>received RF signal and '0' when not in<br>lock. This status is a combination of<br>carrier tracking lock and signal presence<br>detection                                                                                                     |  |  |

| CARRIER_ACQUIRED                                                                                                                                                                                                                                                                        |  |  |

| Combination of symbol timing loop lock<br>and signal presence<br>Solid 1 when locked, toggling when<br>unlocked, 0 when no signal presence                                                                                                                                              |  |  |

| SYMBOL INLOCK STATUS                                                                                                                                                                                                                                                                    |  |  |

| 'l' when FFT detects the residual carrier.<br>Reliable status.<br>SIGNAL_PRESENT_OUT                                                                                                                                                                                                    |  |  |

| Measured frequency offset with respect<br>to the nominal carrier frequency.<br>32-bit signed integer expressed as<br>$f_{cerror} * 2^{32} / f_{elk}$<br>CARRIER FREQUENCY                                                                                                               |  |  |

| Number of bit errors over 80000<br>demodulated bits. (the 80000 bit window<br>length can be changed in the generic<br>section of the BER2.vhd component)<br>Valid only when the BER tester is<br>synchronized (BER_SYNC = '1') and the<br>received signal is a PRBS11 test<br>sequence. |  |  |

| BER_COUNT(31:0)                                                                                                                                                                                                                                                                         |  |  |

| 1 when the BERT is synchronized. BER SYNC                                                                                                                                                                                                                                               |  |  |

| 1 CLK pulse for each wrong Byte<br>detected by the BERT<br>BYTE_ERROR                                                                                                                                                                                                                   |  |  |

| monitor miscellaneous saturations<br>bit 0: at receiver0<br>bit 1: FFT for signal detection<br>bit 2: AGC<br>bit 3: at half-band filter<br>bit 4: resampling<br>bit 5: raised cosine filter<br>SATURATION_OUT(8:0)                                                                      |  |  |

|                                                                                                                                                                                                                                                                                         |  |  |

#### I/Os

| →<br>→                                                                                                                                                                 | COM1852_RX F<br>CLK<br>SYNC RESET                                                                                                            | PROXIMITY-1 RE           | CEIVER                                                                                                                                                                  |            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| <b>)</b><br><b>)</b><br><b>)</b>                                                                                                                                       | _                                                                                                                                            | INPUT COMPLEX<br>SAMPLES | OUTPUT STREAMS<br>DATA_OUT(3:0)<br>SAMPLE_CLK_OUT                                                                                                                       | <b>→</b> → |

| $\begin{array}{c} \leftarrow \\ \leftarrow \\ \rightarrow \\$ | AGC_DAC(11:0)<br>AGC_DAC_SAMPLE_CLK<br>AGC_RESPONSE(4:0)<br>RECEIVER_CENTER_FRE<br>NOMINAL_SYMBOL_RATE<br>CIC_R(15:0)<br>DEMOD_CONTROL(15:0) | EQ(31:0)                 | MONITORING<br>CARRIER_ACQUIRED<br>SYMBOL_INLOCK_STATUS<br>CARRIER_LOCK_OUT<br>SIGNAL_PRESENT_OUT<br>SYMBOL_TIMING_LOCK_OUT<br>CARRIER_FREQUENCY(31:0)<br>SATURATION_OUT | ******     |

|                                                                                                                                                                        |                                                                                                                                              |                          | BERT BER_SYNC<br>BER_ERROR_COUNT(31:0)<br>BYTE_ERROR                                                                                                                    | * * *      |

#### **Receiver inputs**

**ADC\_DATA\_I/Q\_IN(15:0)**: input samples from one or two external ADCs. (one in the case of IF undersampling, two for near-zero frequency complex inputs). If the ADCs have fewer than 16-bit precision, align the most significant bit with ADC\_DATA\_IN(15). Format: 2's complement (signed).

**ADC\_SAMPLE\_CLK\_IN**: '1' when **ADC\_DATA\_I/Q\_IN** is valid. Generally fixed at '1' when input is connected directly to ADCs.

AGC\_DAC(11:0): output to an external DAC to control an external AGC. Gain control for the external analog/IF/RF front-end. May need to be inverted depending on the analog front-end. 12-bit unsigned. FFF represents the minimum gain, 000 the maximum gain.

Read when AGC\_DAC\_SAMPLE\_CLK is '1'

The above signals are clock-synchronous with ADC sampling clock CLK.

#### **Receiver output**

**DATA\_OUT(3:0)**: 4 bit soft-quantized demodulator output. 4-bit sample format: 0000 most negative, 1111 most positive, with no zero representation.

**DATA\_OUT\_VALID**: 1 clock-wide pulse indicating that **DATA\_OUT** is valid.

The output signals are synchronous with the CLK ADC sampling clock.

#### **Transmitter inputs**

**DATA\_IN(7:0)**: input data is read one Byte at a time.

**DATA\_IN\_VALID**: 1 clock-wide pulse indicating that **DATA\_IN** is valid.

**SOF\_IN**: optional Start Of Frame. 1 clock-wide pulse.

**CTS\_OUT**: "Clear-To-Send" output flow-control signal. The data source should stop sending new Bytes when CTS\_OUT = '0';

#### **Transmitter outputs**

**DATA\_I/Q\_OUT(17:0)**: Modulated baseband output samples (I = in-phase, Q = quadrature). One output sample every clock. Format: 2's complement (signed)

**TX\_EN\_OUT**: goes low to turn off an external power amplifier when the modulator is active. It includes a timing margin at the start/end of burst.

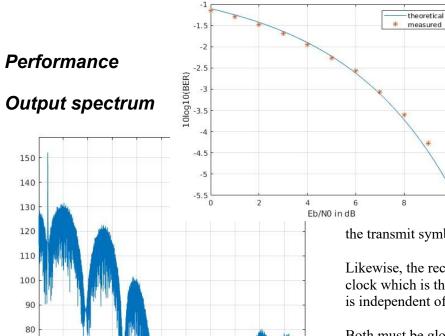

Transmitted spectrum: 32.768 Msamples/s, 64 Ksymbols/s data (Bi-Phase L encoded). Resolution 100Hz.

#### Spectrum, symmetric around the residual carrier. No output filtering.

1.2 1.4 1.6 1.8 2

## BER vs E<sub>b</sub>/N<sub>0</sub> performance

0.2

0.4 0.6 0.8 1

The theoretical BER performance is shown as a blue line. It is generated by the Matlab function berawgn(0:0.1:10, 'psk', 2, 'nondiff')

Actual modem BER measurements over 250ms are shown as red stars.

## Operation

#### Clocks

The transmitter COM1852 TX uses a single clock CLK which is the DAC interface sampling clock. The DAC sampling clock selection is independent of

the transmit symbol rate.

10

Likewise, the receiver COM1852 RX uses a single clock which is the ADC sampling clock. Its selection is independent of the received symbol rate.

Both must be global clocks (i.e. go through BUFG global buffers in the FPGA).

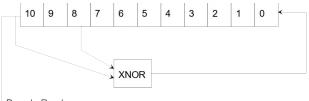

#### Pseudo-Random Bit Stream (Test Pattern)

A periodic pseudo-random sequence can be used as modulator source instead of the input data stream. A typical use would be for end-to-end bit-error-rate measurement of a communication link. The sequence is 2047-bit long maximum length sequence generated by a 11-tap linear feedback shift register:

Pseudo-Random Sequence

The first 100 bits of the PN sequence are as follows: 000000000 011111111 0011111110 0001111100 1101001100 0011000001

#### Format Conversion

Serial to parallel conversion occurs at the interface between the modem and the application, for example at TX DATA(7:0) modulator input. The general rule is that the first received bit is placed at the MSb position in the byte.

#### **Receiver AGC**

To maintain linearity throughout the receive path, several AGC loops control the signal level. While most AGC loops are internal, an additional AGC loop is dedicated to controlling an external RF/IF/analog front-end.

The purpose of this AGC is to prevent saturation at the external A/D converter(s) while making full use of the A/D converter(s) dynamic range. The controlling signal AGC\_DAC(11:0) can be read from the receiver status or can be connected directly to an external auxiliary DAC.

The AGC responsiveness can be adjusted using the **RECEIVER\_AGC\_RESPONSE(4:0)** control.

#### Software Licensing

The COM-1852SOFT is supplied under the following key licensing terms:

- 1. A nonexclusive, nontransferable license to use the VHDL source code internally, and

- 2. An unlimited, royalty-free, nonexclusive transferable license to make and use products incorporating the licensed materials, solely in bit stream format, on a worldwide basis.

The complete VHDL/IP Software License Agreement can be downloaded from http://www.comblock.com/download/softwarelicense.pdf

## **Configuration Management**

The current software revision is 012424

| Directory        | Contents                                                                                                                                                                                                                          |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /doc             | Specifications, user manual, implementation documents                                                                                                                                                                             |

| /src             | .vhd source code,.pkg packages, .xdc<br>constraint files (Xilinx)<br>One component per file.                                                                                                                                      |

| /sim             | VHDL test benches                                                                                                                                                                                                                 |

| /matlab          | Matlab.m file for simulating the encoding<br>and decoding algorithms, for generating<br>stimulus files for VHDL simulation,<br>including channel impairments: noise,<br>frequency error, Doppler rate, amplitude<br>changes, etc. |

| com-<br>1852data | A folder containing ready-to-use stimulus<br>files for receiver VHDL simulation. Use in<br>conjunction with the testbench<br>/sim/tbcom1852_demodonly.vhd                                                                         |

Project files:

Xilinx Vivado v2020 project file: project\_1v2020.xpr project\_1v2020.tcl

## VHDL development environment

The VHDL software was developed using the following development environment:

• Xilinx Vivado 2020 for synthesis, place and route and VHDL simulation

#### **Device Utilization Summary**

AWGN generator instantiated.

| Transmitter<br>COM1852_TX |      | Artix7-<br>100T<br>utilization |

|---------------------------|------|--------------------------------|

| LUTs                      | 6269 | 9.9%                           |

| Registers                 | 2941 | 2.3%                           |

| Block RAM/FIFO 36Kb       | 9.5  | 7.0%                           |

| DSP                       | 33   | 13.8%                          |

| GCLKs                     | 1    | 3.1%                           |

BER tester instantiated.

| Receiver<br>COM1852_RX |      | Artix7-<br>100T<br>utilization |

|------------------------|------|--------------------------------|

| LUTs                   | 7528 | 11.9%                          |

| Registers              | 6941 | 5.5%                           |

| Block RAM/FIFO 36Kb    | 21.5 | 15.9%                          |

| DSP                    | 64   | 26.7%                          |

| GCLKs                  | 1    | 3.1%                           |

#### VHDL components overview

#### **Transmitter top level**

#### • -- COM1852\_TX(Behavioral) (com1852\_tx.vhd) (9)

- > Inst\_LFSR11P : LFSR11P(behavior) (Ifsr11p.vhd) (1)

- > BURST\_TX\_001 : BURST\_TX(Behavioral) (burst\_tx.vhd) (2)

- ROM\_FIL1\_001 : ROM\_FIL1(behavioral) (rom\_fil1.vhd) (5)

- SAMPLINGx4.CPM\_FILTERSx4\_001 : CPM\_FILTERSx4(Behavioral) (cpm\_filt

- SAMPLINGx4.CPM\_FILTERSx4\_002.CPM\_FILTERSx4\_002 : CPM\_FILTERSx4(

- SAMPLINGx4.CPM\_FILTERSx4\_003.CPM\_FILTERSx4\_003 : CPM\_FILTERSx4(

- SAMPLINGx4.CPM\_FILTERSx4\_004.CPM\_FILTERSx4\_004 : CPM\_FILTERSx4(

- xil\_defaultlib.cpm\_filtersx8

- DELAY4\_001 : DELAY4(behavioral) (delay4.vhd) (1)

- BRAM\_DP2\_001 : BRAM\_DP2C(Behavioral) (bram\_dp2c.vhd)

- RESAMPLING8\_001I : RESAMPLING8(behavioral) (resampling8.vhd)

- SIN\_COS001 : SIGNED\_SIN\_COS\_TBL3(BEHAVIOR) (signed\_sin\_cos\_tbl3.vhd)

- > AWGN\_GEN1.AWGN\_001 : AWGN(behavior) (awgn.vhd) (40)

- AWGN\_GEN1.POWER\_MEASUREMENT\_002a : POWER\_MEASUREMENT(beha'

IMULT18X18SIGNED\_001 : MULT18X18SIGNED(BEHAVIOR) (mult18x18si

- > AWGN\_GEN1.POWER\_MEASUREMENT\_002b : POWER\_MEASUREMENT(beha

*COM1852\_TX.vhd* implements the digital PCM/Bi-Phase L/phase modulation. Its input consists of 8-bit parallel data bits, packed MSb first. Key controls include modulation symbol rate, output signal amplitude, output center frequency and additive noise generation. The modulated complex baseband signal output is in 16-bit 2's complement format at the DAC sampling rate. The *BURST\_TX.vhd* component stores input data in an elastic input buffer, then packs input bits into symbols (1 bit/symbol) at the specified symbol rate.

*RESAMPLING8.vhd* interpolates the modulated waveform from its native 8 samples/symbol to the DAC sampling rate. The interpolation is based on a 1024-step polyphase filter.

*DIGITAL\_DC3.vhd* translates the modulated signal to a non-zero output center frequency, under the control of the 32-bit NCO *NCO32X.vhd*. The frequency translation uses *SIGNED\_SIN\_COS\_TBL3.vhd* as sine/cosine lookup tables.

*BRAM\_DP2.vhd* is a generic dual-port memory, used as input and output elastic buffers. Memory is inferred for code portability (no primitive is used).

Prior to the DAC, the digital waveform amplitude is adjusted by digital multiplers *MULT18X18SIGNED.vhd*.

#### Ancillary components

*LFSR11P.vhd* is a pseudo-random sequence generator used for test purposes. It generates a PRBS11 test sequence commonly used for bit error rate testing at the receiving end of a transmission channel.

*AWGN.vhd* generates a precise Additive White Gaussian Noise. The noise bandwidth is 2\*symbol rate.

*POWER\_MEASUREMENT.vhd* is used to provide independent power measurements for the modulated signal and the AWGN.

*SIM2OUTFILE.vhd* writes three 12-bit data variables to a tab delimited file which can be subsequently read by Matlab (load command) for plotting or analysis.

#### **Receiver top level**

| COM1852_RX_001          | COM1852_RX(Behavioral)           |

|-------------------------|----------------------------------|

| >  RECEIVER0 001        | RECEIVER0(Behavioral)            |

| > RX_DETECT_001         | RX_SIGNAL_DETECTION(Behavioral)  |

| CIC_FILTER_001          | CIC(behavioral)                  |

| CIC_FILTER_002          | CIC(behavioral)                  |

| > <b>a</b> GC21_002     | AGC21(behavioral)                |

| > FIRHALFBAND32_I1      | FIRHALFBAND32(Behavioral)        |

| > E FIRHALFBAND32_Q1    | FIRHALFBAND32(Behavioral)        |

| PROXIMITY_1_DEMOD_001   | PROXIMITY_1_DEMOD(behavioral)    |

| > 🗐 phase_006           | PROXIMITY_1_DEMOD(behavioral)    |

| > ERESAMPLING71_0011    | RESAMPLING71(behavioral)         |

| > ERESAMPLING71_001Q    | RESAMPLING71(behavioral)         |

| > 🗐 phase_007           | PROXIMITY_1_DEMOD(behavioral)    |

| FIR_RC1_0011            | FIR_RC1(Behavioral)              |

| FIR_RC1_001Q            | FIR_RC1(Behavioral)              |

| > 🔳 phase_009           | PROXIMITY_1_DEMOD(behavioral)    |

| > 🔳 SIN_COS001          | SIGNED_SIN_COS_TBL3(BEHAVIOR)    |

| > 📃 phase_010           | PROXIMITY_1_DEMOD(behavioral)    |

| > CARRIER_TRACK2_003    | CARRIER_TRACKING2_1852(behaviora |

| > E ST_LOOP_003         | SYMBOL_TIMING_LOOP5(BEHAVIOR)    |

| > 🔳 MF001               | MATCHED_FILTERNx1(Behavioral)    |

| > 🗐 sim2outfile_x       | PROXIMITY_1_DEMOD(behavioral)    |

| PX_TO_P8_CONVERSION_003 | PX_TO_P8_CONVERSION(behavioral)  |

*RECEIVER0.vhd* is the front-end digital receiver which processes digital samples from the A/D converter(s). It performs non modulation-specific tasks, including bias removal, internal and external AGC and fixed frequency translation to (near-zero) baseband. Input digital samples can be complex (in the case of baseband input samples) or real (in the case of IF undersampling). This generic component is not modulation-specific. When enabled, it can control the gain of the external RF/IF front-end receiver.

$RX\_SIGNAL\_DETECTION.vhd$  detects the received signal presence and estimates the center frequency. The received signal is first low-pass filtered in a CIC decimation filter to reduce the frequency span to 2\*frequency acquisition window, then fed into a 2048-point FFT. The decimation factor controls the receiver frequency acquisition range (here +/- 80 KHz). Upon signal detection, the measured SIGNAL\_CENTER\_FREQUENCY is used to translate the received signal to near-zero frequency baseband in *RECEIVER0.vhd*. The residual frequency error is thus (+/- 2\*frequency acquisition window / 2048) = +/- 80 Hz The near-zero frequency signal undergoes Low-Pass Filtering and decimation through a CIC decimation filter *CIC.vhd*. The decimation ratio is computed so that the resulting sampling rate is slightly but strictly larger than 8\*data symbol rate.

Following the *RECEIVER0* front-end, the received signal undergoes CIC decimation filtering (*CIC.vhd*), where the signal is Low-Pass Filtered, then decimated down to slightly more than 8 samples per symbol.

*AGC21.vhd* normalizes the signal level, since a significant portion of the noise was rejected in the CIC decimation filter.

*FIRHALFBAND32.vhd* provides some additional low-pass filtering in a half-band FIR filter.

*PROMITY\_1\_DEMOD.vhd* performs typical tasks for a coherent demodulation, namely carrier recover, frequency translation to zero center frequency, symbol timing recovery, resampling at exactly 4 samples per symbol and AGC.

#### The carrier tracking loop

(CARRIER\_TRACKING\_1852.vhd) approximates the phase error as DATA10Q when measured at the center of the Bi-Phase L coded symbol. A secondorder loop ensues. The PLL loop gains are configured to acquire the +/- 80 Hz residual center frequency error (based on the  $RX_SIGNAL_DETECTION.vhd$  FFT resolution). The convergence time is typically 100ms. The second-order branch reports the residual frequency error FREQ\_ERROR. The second-order loop gain LOOP\_GAIN2 may be adjusted to meet specific application requirements in terms of Doppler rate.

The carrier tracking loop is reset while the receiver is in STATE 1 (i.e. before FFT signal detection and coarse frequency estimate)

The symbol timing recovery loop

SYMBOL\_TIMING\_LOOP61.vhd is a second-order Gardner loop based on the DATA10Q signal sampled twice per symbol. It is configured to acquire a symbol rate error of more than 100ppm. A much larger symbol rate error (up to 1%) can be acquired during the idle signal by detecting the periodic sync marker (see MATCHED FILTERNx1.vhd) Two small circuits are added to ensure detection and removal of (a) a 0/180 deg carrier phase ambiguity and (b) a  $\frac{1}{2}$  symbol timing ambiguity.

The 0x352EF853 sync marker (when not FEC encoded) is detected by the *MATCHED\_FILTERNx1.vhd* component. Depending on the application, the sync marker could be FEC encoded or not. Therefore, it is up to the user to move and connect this component after the FEC decoder if applicable.

The sync marker detection pulses are use to perform a coarse symbol rate acquisition, thus reducing the symbol rate error from the maximum 1% down to 100ppm or less. The remaining error is 'mopped up' by *SYMBOL\_TIMING\_LOOP61.vhd*

#### Ancillary components

*INFILE2SIM.vhd* reads up to 3 input signals from a text file (input.txt) formatted as 12-bit tab delimited signals.

*BER2.vhd* is a bit error rate tester expecting to receive a PRBS11 test sequence. It synchronizes with the received bit stream and count errors over a user-defined window. It can be placed immediately after the demodulator, or after the error correction.

#### VHDL simulation

Two VHDL testbenches are located in the /sim directory.

The tbcom1852\_modemonly.vhd connects the modulator and demodulator back to back. End-toend BER tests can be performed as the com1852\_tx.vhd transmitter includes a built-in pseudo-random sequence generator and the com1852\_rx.vhd receiver includes a built-in Bit Error Rate Tester.

The tbcom1852\_demodonly.vhd testbench reads a tab-delimited stimulus files of modulated I/Q baseband complex input samples. The stimulus file *index.txt* is typically generated by a matlab .m program such as siggen\_proximity1.m in the /matlab folder.

## Matlab simulation

Matlab programs are located in the /matlab directory.

The siggen\_proximity1.m program generates a stimulus file input.txt for use as input to the demodulator VHDL simulation (tbcom1852\_demodonly.vhd). The stimulus file includes a continuous stream of pseudo-random (PRBS11) data bits, additive white Gaussian noise, channel filtering, frequency translation and quantization.

Care must be taken to match the modulator configuration in siggen\_proximity1 .m and the demodulator configuration in tbcom1852 demodonly.vhd. This setup allows end-to-end BER testing, as the demodulator com1852\_rx.vhd includes a built-in bit error rate tester.

The Matlab program demod\_ber\_pm.m plots theoretical vs actual BER measurements as a function of the  $E_b/N_0$ .

The following stimulus waveform files can be downloaded from comblock.com/download/VHDL/COM-1852SOFT/. Use test1.txt file with the tbcom1852\_demodonly\_test1 testbench in the sim folder, etc.

| test1.txt | Over the air 16KSymbols/s<br>$E_b/N_0$ . 20 dB<br>Center frequency offet: 0 Hz<br>Symbol rate offset: 0 Hz<br>Duration: 250ms<br>Carrier: 62.5us<br>Idle sequence: 20ms<br>Data: 230ms<br>ADC sampling rate 32.768KS/s        |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| test2     | Over the air 16KSymbols/s<br>$E_b/N_0$ . 8 dB<br>Center frequency offet: 75KHz, 100Hz/s<br>Symbol rate offset: 0 Hz<br>Duration: 250ms<br>Carrier: 10ms<br>Idle sequence: 20ms<br>Data: 220ms<br>ADC sampling rate 32.768KS/s |

| test3     | Over the air 256KSymbols/s<br>$E_b/N_0$ . 5 dB<br>Center frequency offet: 75KHz, 100Hz/s<br>Symbol rate offset: 0 Hz<br>Duration: 250ms<br>Carrier: 10ms<br>Idle sequence: 10ms<br>Data: 230ms                                |

ADC sampling rate 32.768KS/s

| test4 | Over the air 1024KSymbols/s           |

|-------|---------------------------------------|

|       | $E_b/N_0$ . 5 dB                      |

|       | Center frequency offet: 20KHz, 75Hz/s |

|       | Symbol rate offset: 0 Hz              |

|       | Duration: 250ms                       |

|       | Carrier: 10ms                         |

|       | Idle sequence: 10ms                   |

|       | Data: 230ms                           |

|       | ADC sampling rate 32.768KS/s          |

|       |                                       |

test5 Over the air 4096KSymbols/s  $E_b/N_0.0 dB$ Center frequency offet: -81KHz, -200Hz/s Symbol rate offset: 0 Hz Duration: 250ms Carrier: 10ms Idle sequence: 10ms Data: 230ms ADC sampling rate 32.768KS/s

## **Specifications**

[1] CCSDS "Proximity-1 Space Link Protocol: Physical layer", CCSDS 211.1-B-4, December 2013

[2] CCSDS "Proximity-1 Space Link Protocol: coding and synchronization sublayer", CCSDS 211.2-B-3, October 2019

## Acronyms

| Acronym          | Definition                                         |

|------------------|----------------------------------------------------|

| ADC              | Analog to Digital Converter                        |

| AWGN             | Additive White Gaussian Noise                      |

| BRAM             | Dual-port Block RAM                                |

| BER              | Bit Error Rate                                     |

| BERT             | Bit Error Rate Tester                              |

| CCSDS            | Consultative Committee for Space Data<br>Systems   |

| DAC              | Digital to Analog Converter                        |

| DVB              | Digital Video Broadcast                            |

| FPGA             | Field Programmable Gate Arrays                     |

| LSb              | Least Significant bit                              |

| LSB              | Least Significant Byte                             |

| M&C              | Monitoring and Control                             |

| MSb              | Most Significant bit                               |

| MSB              | Most Significant Byte                              |

| N/A              | Not Applicable                                     |

| NCO              | Numerically Control Oscillator                     |

| PRBS-11          | Pseudo-Random Binary Sequence, 2047-<br>bit period |

| R <sub>cs</sub>  | Coded symbol rate                                  |

| R <sub>chs</sub> | Channel symbol rate                                |

| SoC              | System on Chip                                     |

| UART             | Universal Asynchronous<br>Receiver/Transmitter     |

## **ComBlock Ordering Information**

#### COM-1852SOFT CCSDS Proximity-1 modem, ,

- VHDL source code / IP core

- transmit-only

- $\circ$  receive-only

- o tx/rx bundle

#### ECCN: EAR99

MSS • 845 Quince Orchard Boulevard Ste N• Gaithersburg, Maryland 20878-1676 • U.S.A. Telephone: (240) 631-1111 E-mail: sales@comblock.com