COM-5002

## Key Features

- TCP-IP server connects ComBlock assemblies to network clients for data transfer, monitoring and control.

- Standard 100Base-Tx/10Base-T, RJ-45 connector. Autonegotiation or manual settings: 10/100 Mbit/s, full/half duplex.

- Maximum sustained throughput: 25 Mbits/s (100Base-Tx).

5.3 Mbits/s (10Base-T). Actual speed depends on host computer.

- Elastic buffering and flow-control on each transmit and receive link.

- Monitoring and control of ComBlock assemblies over LAN or serial link from a graphical user interface.

- Single 5V supply. Standard 40 pin 2mm dual row connectors (right, left)

For the latest data sheet, please refer to the **ComBlock** web site: <u>www.comblock.com/download/com5002.pdf</u>. These specifications are subject to change without notice.

For an up-to-date list of **ComBlock** modules, please refer to <u>www.comblock.com/product\_list.htm</u>.

# LAN / IP NETWORK INTERFACE

# **Typical Applications**

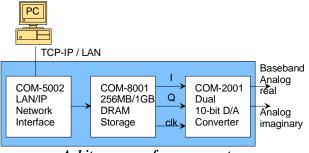

#### Arbitrary Waveform Signal Generation

Files representing binary or analog sampled signals can be uploaded through the COM-5002 to the COM-8001 SDRAM memory over the network, then played back at the selected speed. Various ComBlocks can be used to generate analog signals at baseband, 70 MHz intermediate frequency or radio-frequency.

Arbitrary waveform generator, analog baseband example

# Interfaces

| Input Interface                                                      | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATA_IN[7:0]                                                         | Input signal. The input width is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| _ []                                                                 | user programmable as a function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                      | of the data source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

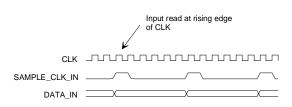

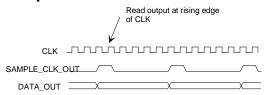

| SAMPLE_CLK_IN                                                        | Input signal sampling clock. One                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                      | CLK_IN-wide pulse. Read the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                      | input signal at the rising edge of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                      | CLK_IN when                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                      | $SAMPLE_CLK_IN = '1'.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                      | Samples can be consecutive. For                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                      | example, SAMPLE_CLK_IN can                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                      | be fixed at '1' to indicate that                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                      | new input samples are provided                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                      | once per CLK_IN clock period.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                      | Signal is pulled-up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CLK_IN                                                               | Input reference clock for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                      | synchronous I/O. DATA_IN and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                      | SAMPLE_CLK_IN are read at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                      | the rising edge of CLK_IN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                      | Maximum 40 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Output Interface                                                     | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DATA_OUT[7:0]                                                        | Output signal. The output width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1                                                                    | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                      | is user programmable as a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SAMPLE CLK OUT                                                       | function of the data sink.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SAMPLE_CLK_OUT                                                       | function of the data sink.<br>Output signal sampling clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SAMPLE_CLK_OUT                                                       | function of the data sink.<br>Output signal sampling clock.<br>One CLK_OUT-wide pulse.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SAMPLE_CLK_OUT                                                       | function of the data sink.<br>Output signal sampling clock.<br>One CLK_OUT-wide pulse.<br>Read the output signal at the                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SAMPLE_CLK_OUT                                                       | function of the data sink.<br>Output signal sampling clock.<br>One CLK_OUT-wide pulse.<br>Read the output signal at the<br>rising edge of CLK_OUT when                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                      | function of the data sink.<br>Output signal sampling clock.<br>One CLK_OUT-wide pulse.<br>Read the output signal at the<br>rising edge of CLK_OUT when<br>SAMPLE_CLK_OUT = '1'.                                                                                                                                                                                                                                                                                                                                                                                                         |

| SAMPLE_CLK_OUT                                                       | function of the data sink.<br>Output signal sampling clock.<br>One CLK_OUT-wide pulse.<br>Read the output signal at the<br>rising edge of CLK_OUT when<br>SAMPLE_CLK_OUT = '1'.<br>40 MHz output reference clock.                                                                                                                                                                                                                                                                                                                                                                       |

| CLK_OUT                                                              | function of the data sink.<br>Output signal sampling clock.<br>One CLK_OUT-wide pulse.<br>Read the output signal at the<br>rising edge of CLK_OUT when<br>SAMPLE_CLK_OUT = '1'.<br>40 MHz output reference clock.<br>(from internal oscillator).                                                                                                                                                                                                                                                                                                                                        |

|                                                                      | function of the data sink.<br>Output signal sampling clock.<br>One CLK_OUT-wide pulse.<br>Read the output signal at the<br>rising edge of CLK_OUT when<br>SAMPLE_CLK_OUT = '1'.<br>40 MHz output reference clock.<br>(from internal oscillator).<br><b>Definition</b>                                                                                                                                                                                                                                                                                                                   |

| CLK_OUT Other Interfaces                                             | function of the data sink.<br>Output signal sampling clock.<br>One CLK_OUT-wide pulse.<br>Read the output signal at the<br>rising edge of CLK_OUT when<br>SAMPLE_CLK_OUT = '1'.<br>40 MHz output reference clock.<br>(from internal oscillator).<br>Definition<br>4 wire. 10Base-T/100Base-TX.                                                                                                                                                                                                                                                                                          |

| CLK_OUT Other Interfaces                                             | function of the data sink.<br>Output signal sampling clock.<br>One CLK_OUT-wide pulse.<br>Read the output signal at the<br>rising edge of CLK_OUT when<br>SAMPLE_CLK_OUT = '1'.<br>40 MHz output reference clock.<br>(from internal oscillator).<br><b>Definition</b>                                                                                                                                                                                                                                                                                                                   |

| CLK_OUT Other Interfaces                                             | function of the data sink.<br>Output signal sampling clock.<br>One CLK_OUT-wide pulse.<br>Read the output signal at the<br>rising edge of CLK_OUT when<br>SAMPLE_CLK_OUT = '1'.<br>40 MHz output reference clock.<br>(from internal oscillator).<br><b>Definition</b><br>4 wire. 10Base-T/100Base-TX.<br>RJ45 connector. NIC wiring. Use                                                                                                                                                                                                                                                |

| CLK_OUT Other Interfaces                                             | function of the data sink.<br>Output signal sampling clock.<br>One CLK_OUT-wide pulse.<br>Read the output signal at the<br>rising edge of CLK_OUT when<br>SAMPLE_CLK_OUT = '1'.<br>40 MHz output reference clock.<br>(from internal oscillator).<br><b>Definition</b><br>4 wire. 10Base-T/100Base-TX.<br>RJ45 connector. NIC wiring. Use<br>standard category 5 cable for<br>connection to a Hub. Use<br>crossover cable for connection to                                                                                                                                              |

| CLK_OUT Other Interfaces                                             | function of the data sink.<br>Output signal sampling clock.<br>One CLK_OUT-wide pulse.<br>Read the output signal at the<br>rising edge of CLK_OUT when<br>SAMPLE_CLK_OUT = '1'.<br>40 MHz output reference clock.<br>(from internal oscillator).<br><b>Definition</b><br>4 wire. 10Base-T/100Base-TX.<br>RJ45 connector. NIC wiring. Use<br>standard category 5 cable for<br>connection to a Hub. Use                                                                                                                                                                                   |

| CLK_OUT Other Interfaces                                             | function of the data sink.<br>Output signal sampling clock.<br>One CLK_OUT-wide pulse.<br>Read the output signal at the<br>rising edge of CLK_OUT when<br><u>SAMPLE_CLK_OUT = '1'.</u><br>40 MHz output reference clock.<br>(from internal oscillator).<br><b>Definition</b><br>4 wire. 10Base-T/100Base-TX.<br>RJ45 connector. NIC wiring. Use<br>standard category 5 cable for<br>connection to a Hub. Use<br>crossover cable for connection to<br>a host computer.<br>DB9 connector.                                                                                                 |

| CLK_OUT<br>Other Interfaces<br>LAN                                   | function of the data sink.<br>Output signal sampling clock.<br>One CLK_OUT-wide pulse.<br>Read the output signal at the<br>rising edge of CLK_OUT when<br><u>SAMPLE_CLK_OUT = '1'.</u><br>40 MHz output reference clock.<br>(from internal oscillator).<br><b>Definition</b><br>4 wire. 10Base-T/100Base-TX.<br>RJ45 connector. NIC wiring. Use<br>standard category 5 cable for<br>connection to a Hub. Use<br>crossover cable for connection to<br>a host computer.<br>DB9 connector.<br>115 Kbaud/s. 8-bit, no parity, one                                                           |

| CLK_OUT<br>Other Interfaces<br>LAN<br>Serial Monitoring<br>& Control | function of the data sink.<br>Output signal sampling clock.<br>One CLK_OUT-wide pulse.<br>Read the output signal at the<br>rising edge of CLK_OUT when<br><u>SAMPLE_CLK_OUT = '1'.</u><br>40 MHz output reference clock.<br>(from internal oscillator).<br><b>Definition</b><br>4 wire. 10Base-T/100Base-TX.<br>RJ45 connector. NIC wiring. Use<br>standard category 5 cable for<br>connection to a Hub. Use<br>crossover cable for connection to<br>a host computer.<br>DB9 connector.<br>115 Kbaud/s. 8-bit, no parity, one<br>stop bit. No flow control.                             |

| CLK_OUT<br>Other Interfaces<br>LAN<br>Serial Monitoring              | function of the data sink.<br>Output signal sampling clock.<br>One CLK_OUT-wide pulse.<br>Read the output signal at the<br>rising edge of CLK_OUT when<br>SAMPLE_CLK_OUT = '1'.<br>40 MHz output reference clock.<br>(from internal oscillator).<br><b>Definition</b><br>4 wire. 10Base-T/100Base-TX.<br>RJ45 connector. NIC wiring. Use<br>standard category 5 cable for<br>connection to a Hub. Use<br>crossover cable for connection to<br>a host computer.<br>DB9 connector.<br>115 Kbaud/s. 8-bit, no parity, one<br>stop bit. No flow control.<br>4.75 – 5.25VDC. Terminal block. |

| CLK_OUT<br>Other Interfaces<br>LAN<br>Serial Monitoring<br>& Control | function of the data sink.<br>Output signal sampling clock.<br>One CLK_OUT-wide pulse.<br>Read the output signal at the<br>rising edge of CLK_OUT when<br><u>SAMPLE_CLK_OUT = '1'.</u><br>40 MHz output reference clock.<br>(from internal oscillator).<br><b>Definition</b><br>4 wire. 10Base-T/100Base-TX.<br>RJ45 connector. NIC wiring. Use<br>standard category 5 cable for<br>connection to a Hub. Use<br>crossover cable for connection to<br>a host computer.<br>DB9 connector.<br>115 Kbaud/s. 8-bit, no parity, one<br>stop bit. No flow control.                             |

# Initial Configuration (via Serial Link)

The IP address must first be configured over serial link. This network setting is saved in non-volatile memory. Once the correct network setting is configured, the Comblock Control Center and this ComBlock assembly can communicate over the intranet or internet as well as over a serial link.

# Configuration (via Serial Link / LAN)

Complete assemblies can be monitored and controlled centrally over a single serial or LAN connection.

The module configuration parameters are stored in non-volatile memory. All control registers are read/write.

Undefined control registers or register bits are for backward software compatibility and/or future use. They are ignored in the current firmware version.

| Parameters       | Configuration                           |

|------------------|-----------------------------------------|

| IP address       | 4-byte IP address.                      |

|                  | Example : 0x AC 10 01 80 designates     |

|                  | address 172.16.1.128                    |

|                  | The new address becomes effective       |

|                  | immediately (no need to reset the       |

|                  | ComBlock).                              |

|                  | REG0: MSB                               |

|                  | REG1                                    |

|                  | REG2                                    |

|                  | REG3: LSB                               |

| Reserved         | REG4-19 Reserved for other network      |

|                  | configurations. No need to write any    |

|                  | data.                                   |

| Input format     | 00000 = J2 input is disabled            |

|                  | 00001 = 1-bit wide from J2              |

|                  | 01000 = 8-bit wide from J2              |

|                  | 11110 = test mode. Internally generated |

|                  | 8-bit wide periodic counting sequence   |

|                  | (0-255) as input. J2 input is disabled. |

|                  | The throughput is determined by the     |

|                  | TCP-IP client.                          |

|                  | REG20 bits 4-0                          |

| Output format    | 00001 = 1-bit wide                      |

|                  | 01000 = 8-bit wide                      |

|                  | REG21 bits 4-0                          |

| COM-8001         | Special use: Writing to REG22 with a    |

| external trigger | '1' in bit 1 will generate a 1 CLK wide |

|                  | pulse on pin J3/B6. The main            |

|                  | application is to trigger the COM-8001  |

|                  | file playback/download. There is no     |

|                  | need to reset this bit to '0' prior to  |

|                  | writing a '1'.                          |

|                  | REG22 bit 1.                            |

| 10Base-T /       | 00 = 10Base-T                           |

| 100Base-TX       | 01 = 100Base-TX                         |

| LAN selection    | 10 = Auto negotiation                   |

|                  | Changes will take effect at the next    |

|                  | power up.                               |

|                  | REG22 bits 3-2                          |

| Half / Full<br>duplex LAN<br>link | 0 = half duplex<br>1 = full duplex<br>Changes will take effect at the next<br>power up.<br>REG22 bit 4                              |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Promiscuous<br>(listen) mode      | Test mode. Incoming packets are not<br>checked for matching destination<br>address.<br>0 = disabled.<br>1 = enabled.<br>REG22 bit 5 |

Baseline configurations can be found at <u>www.comblock.com/tsbasic\_settings.htm</u> and imported into the ComBlock assembly using the ComBlock Control Center File | Import menu.

## Monitoring (via Serial Link / LAN)

Monitoring registers are read-only.

| Parameters                                                                       | Monitoring                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCP-IP<br>connection on<br>port 1024                                             | 1 = connected, 0 otherwise.<br>REG23 bit 0                                                                                                                                                                                               |

| (data stream)                                                                    |                                                                                                                                                                                                                                          |

| TCP-IP<br>connection on<br>port 1028<br>(Monitoring<br>& Control)                | 1 = connected, 0 otherwise.<br>REG23 bit 2                                                                                                                                                                                               |

| Transmit data<br>elastic buffer<br>empty                                         | 1 = empty, 0 otherwise<br>REG23 bit 3                                                                                                                                                                                                    |

| Transmit data<br>elastic buffer<br>full                                          | 1 = full, 0 otherwise<br>REG23 bit 4                                                                                                                                                                                                     |

| Receive data<br>elastic buffer<br>empty                                          | 1 = empty, 0 otherwise<br>REG23 bit 5                                                                                                                                                                                                    |

| Receive data<br>elastic buffer<br>more than half<br>full                         | 1 = more than half full, 0 otherwise<br>REG23 bit 6                                                                                                                                                                                      |

| Number of<br>bytes<br>transmitted<br>from LAN to<br>digital device               | Total number of bytes transmitted over<br>data and signaling channels. 32-bit byte<br>count. Counter rolls over when<br>reaching 0xFFFFFFF.<br>REG24: bits 7-0 (LSB)<br>REG25: bits 15-8<br>REG26: bits 23-16<br>REG27: bits 31-24 (MSB) |

| Number of<br>bytes received<br>from digital<br>device and<br>forwarded to<br>LAN | Total number of bytes received over<br>data and signaling channels. 32-bit byte<br>count. Counter rolls over when<br>reaching 0xFFFFFFF.<br>REG28: bits 7-0 (LSB)<br>REG29: bits 15-8                                                    |

|                         | REG30: bits 23-16<br>REG31: bits 31-24 (MSB)                                       |

|-------------------------|------------------------------------------------------------------------------------|

| MAC address             | Unique 48-bit hardware address<br>(802.3). In the form<br>REG32:REG33:REG34::REG37 |

| Option o /<br>Version v | Returns '5002ov' when prompted for option o and version v numbers.                 |

As the monitoring data is constantly changing, it is important to be able to prevent changes while reading a multi-byte parameter. The monitoring data is latched upon reading register 23. Therefore, register 23 should always be read first.

# **IP Protocols**

This module supports the following IP protocols:

- Ping

- ARP

- TCP-IP

#### Ping

The module responds to ping requests with size up to 470 bytes. Ping can be used to check the module response over the network. Ping can be used at any time, concurrently with other transmit and receive transactions. For example, on a Windows operating system, open the Command prompt window and type "ping -t -1 470 172.16.1.128" to send pings forever of length 470 bytes to address 172.16.1.128.

## TCP-IP

As a Server, the module opens the following sockets in listening mode:

Port 1024: transmit and receive data streams

Port 1028: monitoring and control port

# Operation

#### Concept

The COM-5002 converts a TCP-IP socket stream into a simple data stream and vice versa. On the transmit side, the COM-5002 decodes the TCP-IP protocol and extracts the data from the network client. TCP, IP and Network information, and in particular routing information, are not transmitted from one end to the other. At the receiving end, the network client must first connect to the COM-5002 to receive data.

The COM-5002 maintains the flow-control information between the TCP-IP socket and the input/output interfaces. For example, if the COM-5002 is connected to a COM-1001 QPSK modulator configured for 1 Mbit/s data throughput, the network client (i.e. data source) will be asked for 1 Mbit/s throughput over the TCP-IP link.

#### **Throughput Benchmarks**

The COM-5002 is capable of a sustained (average) throughput of 25 Mbits/s over 100base-Tx and 5.3 Mbit/s over 10base-T. In most cases, the sustained throughput is limited by the TCP-IP client computer and the application running on the client computer as illustrated in the one-way data transfer

benchmarks below:

| Throughput tosts conditions              | Throughput           |

|------------------------------------------|----------------------|

| Throughput tests conditions              | Throughput           |

| Client: Intel Pentium 4 2.6 GHz running  | 25 Mbits/s           |

| winsock-based console application.       |                      |

| Direct cross-over LAN cable. No          | 100Mbytes            |

| network connection. No other application | transferred in 32    |

| running.                                 | seconds.             |

| COM-5002 configured as 'Auto             | 500011051            |

| Negotiation". 100Base-Tx connection.     |                      |

| Client: Intel Celeron 766 MHz running    | 14 Mbits/s           |

| winsock-based console application.       |                      |

| Direct cross-over LAN cable. No          | 100Mbytes            |

| network connection. No other application | transferred in 57    |

| running.                                 | seconds.             |

| COM-5002 configured as 'Auto             | seconds.             |

| Negotiation". 100Base-Tx connection.     |                      |

| Client: Intel Pentium 4 2.6 GHz running  | 5.36 Mbits/s         |

| winsock-based console application.       |                      |

| Direct cross-over LAN cable. No          | 100Mbytes            |

| network connection. No other application | transferred in       |

| running.                                 | 149 seconds.         |

| COM-5002 or client computer              | 14) seconds.         |

| configured as '10Base-T". 10Base-T       |                      |

| connection.                              |                      |

| Client: Intel Celeron 766 MHz running    | 4.16 Mbits/s         |

| winsock-based console application.       |                      |

| Direct cross-over LAN cable. No          | 100Mbytes            |

| network connection. No other application | transferred in       |

| running.                                 | 192 seconds.         |

| COM-5002 or client computer              | 1 <i>92</i> seconds. |

| configured as '10Base-T". 10Base-T       |                      |

| connection.                              |                      |

| Client: Intel Pentium 4 2.6 GHz running  | 4.82 Mbits/s         |

| Java JRE-based application (ComBlock     |                      |

| Control Center). Direct cross-over LAN   | 208Mbytes            |

| cable. No network connection. No other   | transferred in       |

| application running.                     | 345 seconds.         |

| COM-5002 or client computer              | 545 seconds.         |

| configured as '10Base-T". 10Base-T       |                      |

| connection.                              |                      |

#### **Format Conversion**

Parallel to serial conversion occurs at the output when a 8-bit byte received over the TCP-IP link is converted to n-bit serial, where the sample width n is selected by the user. The key rule for parallel to serial conversion is that the most significant bit (MSb) is transmitted first.

Likewise, in the serial-to-parallel conversion which occurs at the input, the first received bit is placed at the MSb position in the byte.

# **Client Programming**

This section is intended to help designers who want to design their own client application. It can be skipped by users of ready-to-use applications such as Hyperterminal, ComBlock Control Center, etc.

In network terminology, the COM-5002 is a server. It awaits connection establishment and connection termination under the initiation of clients. It never initiate any connection establishment or termination.

An example of C-language Winsock programming for Windows OS clients is shown below. More information about Winsock programming can be found at <u>http://msdn.microsoft.com/library/default.asp?url=/l</u> <u>ibrary/en-</u> <u>us/winsock/winsock/finished\_server\_and\_client\_co</u> de.asp

Be sure to include a reference to the Winsock2 library (WS2\_32.lib) in the project release and/or debug settings.

```

#include <stdio.h>

#include "winsock2.h"

void main() {

// Initialize Winsock.

WSADATA wsaData;

int iResult = WSAStartup( MAKEWORD(2,2), &wsaData );

if ( iResult != NO_ERROR )

printf("Error at WSAStartup()\n");

// Create a socket.

SOCKET m_socket;

m_socket = socket( AF_INET, SOCK_STREAM, IPPROTO_TCP );

if ( m_socket == INVALID_SOCKET ) {

printf( "Error at socket(): %ld\n", WSAGetLastError() );

WSACleanup();

return;

}

// Connect to a server.

sockaddr_in clientService;

clientService.sin family = AF INET;

// insert destination address below

clientService.sin_addr.s_addr = inet_addr( "172.16.1.128" );

// insert destination port below

clientService.sin_port = htons(1024);

if ( connect( m_socket, (SOCKADDR*) &clientService, sizeof(clientService) ) ==

SOCKET_ERROR) {

printf( "Failed to connect.\n" );

WSACleanup();

return;

}

// Send and receive data.

int bytesSent;

int bytesRecv = SOCKET_ERROR;

char sendbuf[32] = "Client: Sending data.";

char recvbuf[32] = "";

bytesSent = send( m_socket, sendbuf, strlen(sendbuf), 0 );

printf( "Bytes Sent: %ld\n", bytesSent );

while( bytesRecv == SOCKET_ERROR ) {

bytesRecv = recv( m_socket, recvbuf, 32, 0 );

if ( bytesRecv == 0 || bytesRecv == WSAECONNRESET ) {

printf( "Connection Closed.\n");

break;

}

if (bytesRecv < 0)

return;

printf( "Bytes Recv: %ld\n", bytesRecv );

}

return;

```

# Timing

#### Clocks

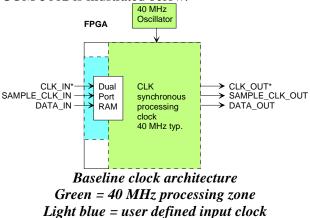

The clock distribution scheme embodied in the COM-5002 is illustrated below.

\* indicates edge-trigger signal

The core signal processing performed within the FPGA is synchronous with the processing clock  $\mathbf{f}_{clk}$ . The processing clock is derived from a 40 MHz oscillator.  $\mathbf{f}_{clk}$  is <u>not</u> related to the external CLK\_IN clock.

A 512-sample Dual-port RAM elastic buffer is used at the boundary between inputs and internal processing area. Thus, the input clocks frequencies can be independent from the internal processing clock frequency.

The input signals at the J2 connector are synchronous with the CLK\_IN clock at J2/A1. This clock can be up to 40 MHz.

The output signals are synchronous with the rising edge of the 40 MHz reference clock CLK\_OUT (i.e. all signals are stable at the rising edge of the reference clock CLK\_OUT).

#### Input

# LEDs

2 LEDs located close to the LAN RJ-45 jack provide summary information as to the LAN: Link and activity.

## **Test Points**

Test points are provided for easy access by an oscilloscope probe. The main focus of these test points is to help monitor proper flow control operation.

| Test  | Definition                                        |

|-------|---------------------------------------------------|

| Point |                                                   |

| TP 1  | TCP-IP connection on port 1024 (data stream)      |

|       | 1 = connected, $0 $ otherwise                     |

| TP 2  | Future use                                        |

| TP 3  | TCP-IP connection on port 1028 (Monitoring &      |

|       | Control)                                          |

|       | 1 = connected, $0 $ otherwise                     |

| TP 4  | Transmit data elastic buffer empty                |

|       | 1 = empty, $0 $ otherwise                         |

| TP 5  | Transmit data elastic buffer full                 |

|       | 1 = full, 0 otherwise                             |

| TP 6  | Receive data elastic buffer empty                 |

|       | 1 = empty, $0 $ otherwise                         |

| TP 7  | Receive data elastic buffer more than half full   |

|       | 1 = more than half full, 0 otherwise              |

| TP 8  | Sample requests received through the J3 connector |

| TP9   | Future use                                        |

| TP10  | Future use                                        |

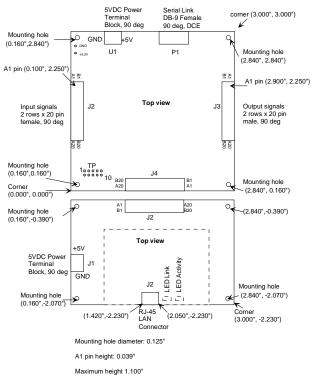

# Mechanical Interface

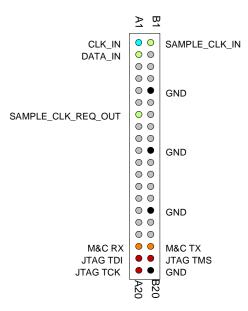

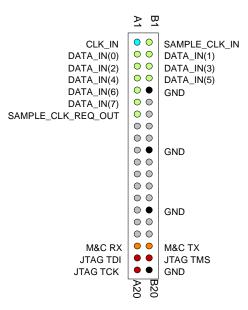

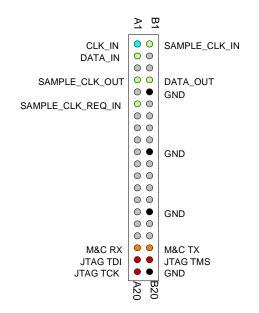

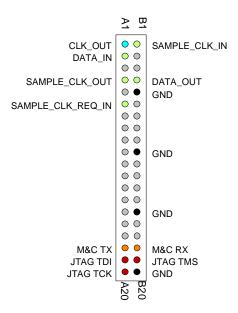

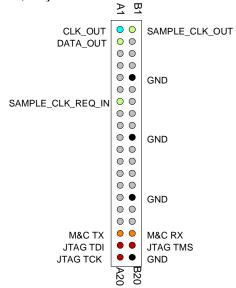

## **Input Connector J2**

There are several possible connector configurations, depending on the application:

(a) 1-bit wide connection to another ComBlock [COM-1001, COM-1011,etc]

Pinout

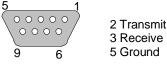

## Serial Link P1

The DB-9 connector is wired as data circuit terminating equipment (DCE). Connection to a PC is over a straight-through cable. No null modem or gender changer is required.

DB-9 Female

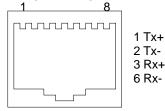

# LAN Connector J2

The RJ-45 Jack is wired as a standard PC network interface card. Connection to a LAN Hub is over a straight-through cable.

RJ-45 Jack

(b) 8-bit wide connection to another ComBlock [COM-8002,etc]

(c) Special case: input connector is used for bidirectional connection to COM-7001 module.

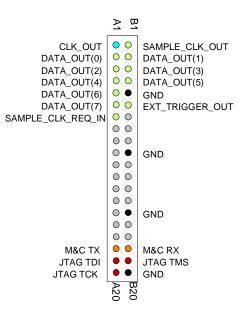

(c) Special case: output connector is used for bi-directional connection to COM-7001 module.

## Output Connector J3

There are several possible connector configurations, depending on the application:

(a) 1-bit wide connection to another ComBlock [COM-1002, COM-1012, COM-1019, COM-1028, etc]

(b) 8-bit wide connection to another ComBlock [COM-8001, etc]

## I/O Compatibility List

(not an exhaustive list)

| Input              | Output             |

|--------------------|--------------------|

| COM-8002 Data      | COM-8001 Arbitrary |

| acquisition module | Waveform Generator |

## **Configuration Management**

This specification is to be used in conjunction with VHDL software revision 6.

# ComBlock Ordering Information

COM-5002 LAN/IP NETWORK INTERFACE

MSS • 18221 Flower Hill Way #A • Gaithersburg, Maryland 20879 • U.S.A. Telephone: (240) 631-1111 Facsimile: (240) 631-1676 E-mail: sales@comblock.com