# **Key Features**

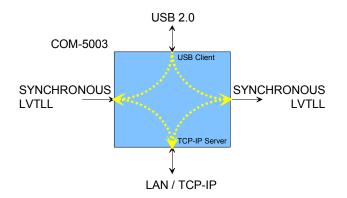

- Generic gateway for LAN/TCP-IP, USB • and LVTTL clock synchronous interfaces.

- Provides ComBlock assemblies with • standard TCP-IP network connectivity and direct USB connection to host computer for both high-speed payload data transfer and monitoring and control.

- **TCP-IP** interface:

- Role: TCP-IP server, Awaits 0 remote client(s) connection.

- Supports 3 bidirectional 0 connections.

- 0 Maximum sustained throughput 53 Mbits/s (100Base-Tx). Actual speed depends on host computer.

- 0 Standard 100Base-Tx/10Base-T, RJ-45 connector. Autonegotiation or manual settings: 10/100 Mbit/s

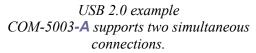

- USB 2.0 interface:

- Role: USB client.

- Supports 2 bidirectional 0 connections.

- Maximum sustained throughput 85 0 Mbits/s (USB 2.0 High-Speed). Actual speed depends on host computer.

- Serial HDLC for interface between byte-• wise asynchronous connections (USB, TCP-IP) and bit-serial fixed data rate connections. Support for two virtual channels when using TCP-IP.

- 16Kbits Elastic buffering and flow-control • on each transmit and receive link

- Single 5V supply. Standard 40 pin 2mm ٠ dual row connectors (right, left)

# COM-5003 TCP-IP / USB GATEWAY

For the latest data sheet, please refer to the **ComBlock** web site: www.comblock.com/download/com5003.pdf. These specifications are subject to change without notice.

For an up-to-date list of **ComBlock** modules, please refer to www.comblock.com/product list.htm.

# **Typical Applications**

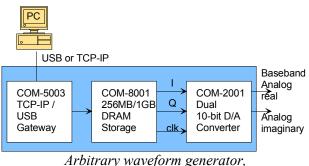

#### Arbitrary Waveform Signal Generation

Files representing binary or analog sampled signals can be uploaded through the COM-5003 to the COM-8001 SDRAM memory over the network, then played back at the selected speed. Various ComBlocks can be used to generate analog signals at baseband, 70 MHz intermediate frequency or radio-frequency.

analog baseband example

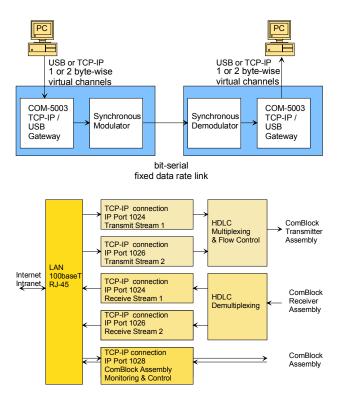

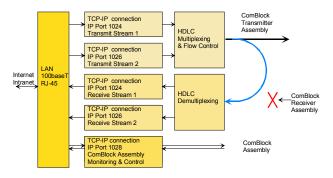

# LAN / USB to Synchronous Link Interface

The COM-5003 can be used as a bridge between a variable data rate (asynchronous) connection such as TCP-IP or USB and a fixed data rate (synchronous) connection like satellite / wireless or cable link.

An HDLC protocol is used over the synchronous link to multiplex multiple data streams over a single link, in effect creating virtual channels. In this module, two virtual channels are implemented in each direction to convey stream 1 and stream 2. Stream 1 is given priority over stream 2.

Whenever no data is available for transmission, the HDLC encoder generates empty frames to fill the synchronous data link. Empty frames are discarded during HDLC decoding.

Note: The COM-5003 differs from a conventional router<sup>1</sup> in several ways:

(a) the TCP and IP protocols are decoded on the transmit side before transmission. Only

the data contents is transmitted. No network information is sent.

- (b) Propagation delay over the synchronous link does not affect the TCP-IP throughput as the TCP-IP protocol is used only locally on the transmit and receive sides.

- (c) The COM-5003 is perfectly suited for use in a broadcast network.

#### LAN TCP-IP example COM-5003-B supports three simultaneous connections.

<sup>&</sup>lt;sup>1</sup> See also  $\underline{\text{COM-5004}}$  IP Router.

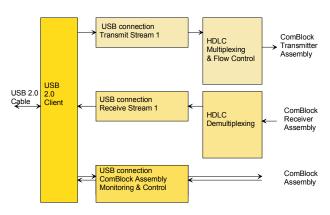

# ComBlock Assembly Monitoring & Control via LAN and/or USB

ComBlock assemblies can be remotely monitored and controlled by a host computer. The COM-5003 extend the selection of communication types to include both TCP-IP and USB.

When using TCP-IP, ComBlock assemblies can be controlled over an internet or intranet network. USB's simple plug&play direct connection to a host computer can be easier as no network configuration is needed. Both USB and TCP-IP are supported by the <u>ComBlock Control Center</u> graphical user interface, so no programming is needed. Several ComBlock assemblies can be monitored and controlled simultaneously from the same computer.

# Interfaces

| Input Signals     | Definition                          |  |  |  |  |

|-------------------|-------------------------------------|--|--|--|--|

| DATA_IN[7:0]      | Input signal. The input width       |  |  |  |  |

|                   | is can be 1-bit or 8-bit under      |  |  |  |  |

|                   | user control. See control           |  |  |  |  |

|                   | register <u>REG20</u> . Signals are |  |  |  |  |

|                   | pulled-down. LVTTL 0 – 3.3V         |  |  |  |  |

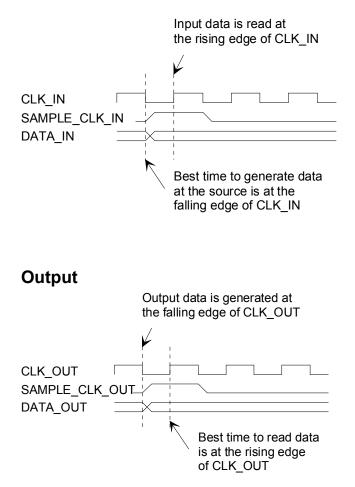

| SAMPLE_CLK_IN     | Input signal sampling clock.        |  |  |  |  |

|                   | One CLK_IN-wide pulse.              |  |  |  |  |

|                   | Read the input signal at the        |  |  |  |  |

|                   | rising edge of CLK_IN when          |  |  |  |  |

|                   | $SAMPLE_CLK_IN = '1'.$              |  |  |  |  |

|                   | Samples can be consecutive.         |  |  |  |  |

|                   | For example,                        |  |  |  |  |

|                   | SAMPLE_CLK_IN can be                |  |  |  |  |

|                   | fixed at '1' to indicate that       |  |  |  |  |

|                   | new input samples are               |  |  |  |  |

|                   | provided once per CLK_IN            |  |  |  |  |

|                   | clock period.                       |  |  |  |  |

|                   | Signal is pulled-up.                |  |  |  |  |

|                   | LVTTL 0 – 3.3V                      |  |  |  |  |

| SAMPLE_CLK_IN_REQ | Input flow control signal           |  |  |  |  |

|                   | (output). '1' indicates that the    |  |  |  |  |

|                   | COM-5003 is ready to accept         |  |  |  |  |

|                   | DATA_IN input samples into          |  |  |  |  |

|                   | its input elastic buffer. LVTTL     |  |  |  |  |

|                   | 0 - 3.3V. Signal is pulled-         |  |  |  |  |

|                   | down.                               |  |  |  |  |

| CLK_IN | Input reference clock for<br>synchronous I/O. DATA_IN<br>and SAMPLE_CLK_IN are<br>read at the rising edge of<br>CLK_IN. Maximum<br>frequency: 40 MHz. LVTTL 0<br>- 3.3V |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output Signals     | Definition                      |

|--------------------|---------------------------------|

| DATA_OUT[7:0]      | LVTTL $0 - 3.3V$ output         |

|                    | signal. The output width is     |

|                    | can be 1-bit or 8-bit under     |

|                    | user control. See control       |

|                    | register <u>REG21</u>           |

| SAMPLE_CLK_OUT     | LVTTL $0 - 3.3V$ output         |

|                    | signal sampling clock. One      |

|                    | CLK_OUT-wide pulse.             |

|                    | Read the output signal at the   |

|                    | rising edge of CLK_OUT          |

|                    | when SAMPLE_CLK_OUT             |

|                    | = '1'.                          |

| SAMPLE_CLK_OUT_REQ | Output flow control signal      |

|                    | (input). '1' asks the COM-      |

|                    | 5003 to send DATA_OUT           |

|                    | output data to the next         |

|                    | module. LVTTL $0 - 3.3V$ .      |

|                    | Signal is pulled-up.            |

| CLK_OUT            | LVTTL 0 – 3.3V 40 MHz           |

|                    | output reference clock.         |

|                    | (from internal oscillator).     |

| EXT_TRIGGER_OUT    | 25 ns pulse triggered by        |

|                    | software command. See           |

|                    | command register <u>REG22</u> . |

|                    | Helpful in triggering events    |

|                    | such as COM-8001 start of       |

|                    | data acquisition. LVTTL 0 –     |

|                    | 3.3V                            |

| Other      | Definition                                |  |  |  |  |  |

|------------|-------------------------------------------|--|--|--|--|--|

| Interfaces |                                           |  |  |  |  |  |

| LAN        | 4 wire. 10Base-T/100Base-TX. RJ45         |  |  |  |  |  |

|            | connector. NIC wiring. Use standard       |  |  |  |  |  |

|            | category 5 cable for connection to a Hub. |  |  |  |  |  |

|            | Use crossover cable for connection to a   |  |  |  |  |  |

|            | host computer.                            |  |  |  |  |  |

| USB        | USB 2.0                                   |  |  |  |  |  |

|            | Use USB 2.0 approved cable for            |  |  |  |  |  |

|            | connection to a host computer. Maximum    |  |  |  |  |  |

|            | recommended cable length is 3'.           |  |  |  |  |  |

| Power      | 4.75 – 5.25VDC. Terminal block. Power     |  |  |  |  |  |

| Interface  | consumption is typically 450mA.           |  |  |  |  |  |

# Initial Configuration

The static <u>IP address</u> must first be configured over USB or through adjacent ComBlocks. This network setting is saved in non-volatile memory. Once the correct network setting is configured, the Comblock Control Center and this ComBlock assembly can communicate over the intranet or internet.

# Configuration

An entire ComBlock assembly comprising several ComBlock modules can be monitored and controlled centrally over a single connection with a host computer. Connection types include built-in types:

- TCP-IP/LAN

- USB

or connections via adjacent ComBlocks:

- USB

- TCP-IP/LAN

- Asynchronous serial (DB9)

- PC Card (CardBus, PCMCIA).

The module configuration is stored in non-volatile memory.

## **Configuration (Basic)**

The easiest way to configure the COM-5003 is to use the **ComBlock Control Center** software supplied with the module on CD.

Start the ComBlock Control Center, click on the *Communication parameters setup* button is and select USB or LAN/IP as the primary communication channel. In the latter case, enter the COM-5003 static IP address.

| Communication Setup |                                          |  |  |  |

|---------------------|------------------------------------------|--|--|--|

| 0                   | Com Port                                 |  |  |  |

|                     | LAN/IP                                   |  |  |  |

| ۲                   | IP-address:<br>172_16_1_130<br>Ping Test |  |  |  |

| 0                   | USB                                      |  |  |  |

| 0                   | CardBus                                  |  |  |  |

|                     | Ok Cancel                                |  |  |  |

Then detect the ComBlock module(s) by clicking the *Detect* button, next click to highlight the COM-5003 module to be configured, next click the *Settings* button to display the *Settings* window shown below:

| 🔁 ComBlock Control Center                                          |  |  |  |  |

|--------------------------------------------------------------------|--|--|--|--|

| File Operations Functions Help                                     |  |  |  |  |

| × • • • • • • • • • • • • • • • • • • •                            |  |  |  |  |

| COM5003 TCP-IP / USB GATEWAY                                       |  |  |  |  |

| TCP-IP / USB GATEWAY Basic Settings                                |  |  |  |  |

| IP-address:<br>172 16 1 130<br>Input Format:<br>8-bit wide from J5 |  |  |  |  |

| Output Format:                                                     |  |  |  |  |

| Apply Ok Advanced Cancel                                           |  |  |  |  |

# **Configuration (Advanced)**

Alternatively, users can access the full set of configuration features by specifying 8-bit control registers as listed below. These control registers can be set manually through the ComBlock Control Center or by software using the ComBlock API (see www.comblock.com/download/M&C\_reference.pdf)

All control registers are read/write.

Undefined control registers or register bits are for backward software compatibility and/or future use. They are ignored in the current firmware version.

| Parameters             | Configuration                                                                                                                                                                                                                     |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IP address             | 4-byte IP address.<br>Example : 0x AC 10 01 80 designates<br>address 172.16.1.128<br>The new address becomes effective<br>immediately (no need to reset the<br>ComBlock).<br>REG0: MSB<br>REG1<br>REG2<br>REG3: LSB               |

| Reserved               | REG4-19 Reserved for other network configurations. No need to write any data.                                                                                                                                                     |

| Input selection        | 00000 = J5 connector is disabled                                                                                                                                                                                                  |

|                        | 00001 = 1-bit serial input from J5 <sup>1</sup>                                                                                                                                                                                   |

|                        | 01000 = 8-bit parallel input from J5                                                                                                                                                                                              |

|                        | 10001 = 1-bit serial input from J8<br>connector (bi-directional I/O)                                                                                                                                                              |

|                        | 11101 = test mode: loopback for 1-bit<br>serial HDLC-encoded stream. J5 input is<br>disabled.                                                                                                                                     |

|                        | 11110 = test mode. Internally generated<br>8-bit wide periodic counting sequence<br>(0-255) as input. J5 input is disabled.<br>Useful in testing the throughput of the<br>TCP-IP or USB data link.                                |

|                        | REG20 bits 4-0                                                                                                                                                                                                                    |

| Bypass<br>descrambling | V.34 descrambling of the bit-serial<br>stream is implemented prior to HDLC<br>decoding. This command is ineffective<br>then HDLC decoding is disabled.<br>0 = descrambling enabled<br>1 = bypass the descrambling.<br>REG20 bit 6 |

| Receive HDLC           | Perform HDLC decoding on 1-bit serial                                                                                                                                                                                             |

<sup>1</sup> Enabling the bit-wise HDLC is strongly advised to preserve the bit to byte alignment information during bit-serial transmission.

| 1.1                          | · / · · · · · · · · ·                                                                                                                                                                                                                                                                |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| enable                       | receive stream (applicable only when 1-<br>bit input serial format is selected above).<br>0 = no<br>1 = yes<br>REG20 bit 7                                                                                                                                                           |

| Output                       | 00000 - 18 connector is dischied                                                                                                                                                                                                                                                     |

| selection                    | 00000 = J8 connector is disabled.                                                                                                                                                                                                                                                    |

|                              | $00001 = 1$ -bit serial output to $J8^1$                                                                                                                                                                                                                                             |

|                              | 01000 = 8-bit parallel output to J8                                                                                                                                                                                                                                                  |

|                              | 10001 = 1-bit serial output to J5 (bi-<br>directional I/O)                                                                                                                                                                                                                           |

|                              | 11111 = special case: 1-bit serial output<br>to COM-7001 FEC encoder through J8.                                                                                                                                                                                                     |

|                              | REG21 bits 4-0                                                                                                                                                                                                                                                                       |

| Bypass<br>scrambling         | V.34 scrambling of the bit-serial stream<br>is implemented after HDLC encoding.<br>This control is ineffective when HDLC<br>is disabled.<br>0 = scrambling enabled                                                                                                                   |

|                              | 1 = bypass the scrambling stage.                                                                                                                                                                                                                                                     |

| Transmit                     | REG21 bit 6<br>Perform HDLC encoding on 1-bit serial                                                                                                                                                                                                                                 |

| HDLC enable                  | receive stream (applicable only when 1-<br>bit output serial format is selected<br>above). When no data is available from<br>the selected source(s), the HDLC engine<br>sends empty frames 7E 7E. Use HDLC<br>encoding to multiplex two streams on<br>the synchronous physical link. |

|                              | When HDLC is disabled, the data<br>source must be ready to fill the IP port<br>1024 or USB connection in order to<br>avoid any underflow condition in the<br>transmit elastic buffers.                                                                                               |

|                              | 0 = no HDLC<br>1 = HDLC enabled.<br>REG21 bit 7                                                                                                                                                                                                                                      |

| COM-8001<br>external trigger | Special use: Writing to REG22 with a '1' in bit 1 will generate a 1 CLK wide                                                                                                                                                                                                         |

|                              | pulse on pin J8/B6. The main<br>application is to trigger the COM-8001<br>file playback/download. There is no<br>need to reset this bit to '0' prior to<br>writing a '1'.                                                                                                            |

|                              | REG22 bit 1.                                                                                                                                                                                                                                                                         |

| 10Base-T /<br>100Base-TX     | 00 = 10Base-T $01 = 100Base-TX$                                                                                                                                                                                                                                                      |

| LAN selection                | 10 = Auto negotiation<br>Changes will take effect at the next                                                                                                                                                                                                                        |

|                              | power up.<br>REG22 bits 3-2                                                                                                                                                                                                                                                          |

| Half/Full                    | Half-duplex is a safe configuration                                                                                                                                                                                                                                                  |

| duplex                       | which can be used with older                                                                                                                                                                                                                                                         |

|                              | networking equipment. Full duplex                                                                                                                                                                                                                                                    |

| results in higher throughput but may be |

|-----------------------------------------|

| incompatible with unswitched hubs.      |

| 0 = half-duplex                         |

| 1 = full duplex.                        |

| Changes will take effect at the next    |

| power up. REG22 bit 4                   |

Baseline configurations can be found at <u>www.comblock.com/tsbasic\_settings.htm</u> and

imported into the ComBlock assembly using the ComBlock Control Center File | Import menu.

# Monitoring

Monitoring registers are read-only.

| <b>D</b> (  |                                                               |  |  |  |  |  |

|-------------|---------------------------------------------------------------|--|--|--|--|--|

| Parameters  | Monitoring                                                    |  |  |  |  |  |

| TCP-IP      | Monitors the TCP-IP connections for all                       |  |  |  |  |  |

| connection  | three ports supported.                                        |  |  |  |  |  |

|             | 1 = connected, $0$ otherwise.                                 |  |  |  |  |  |

|             |                                                               |  |  |  |  |  |

|             | SREG0 bit 0 port 1024 data stream 1                           |  |  |  |  |  |

|             | SREG0 bit 1 port 1026 data stream 2                           |  |  |  |  |  |

|             | SREG0 bit 2 port 1028 M&C                                     |  |  |  |  |  |

| HDLC        | '1' when an HDLC transmit elastic buffer                      |  |  |  |  |  |

| transmit    | is empty, 0 when data transmission is                         |  |  |  |  |  |

| elastic     | pending.                                                      |  |  |  |  |  |

| buffers     | SREG0 bit 3: stream 1                                         |  |  |  |  |  |

| empty       | SREG0 bit 4: stream 2                                         |  |  |  |  |  |

| HDLC        | '1' when an HDLC receive elastic buffer                       |  |  |  |  |  |

| receive     | is more than <sup>3</sup> / <sub>4</sub> full, '0' otherwise. |  |  |  |  |  |

| elastic     | SREG0 bit 5: stream 1                                         |  |  |  |  |  |

| buffer 3⁄4  | SREG0 bit 6: stream 2                                         |  |  |  |  |  |

| full        |                                                               |  |  |  |  |  |

| Number of   | Total number of payload data bytes                            |  |  |  |  |  |

| transmitted | received from LAN or USB and                                  |  |  |  |  |  |

| bytes (USB  | forwarded to an external digital device                       |  |  |  |  |  |

| or LAN)     | (excludes monitoring & control                                |  |  |  |  |  |

|             | messages, includes all virtual data                           |  |  |  |  |  |

|             | streams). 32-bit byte count. Counter rolls                    |  |  |  |  |  |

|             | over when reaching 0xFFFFFFFF.                                |  |  |  |  |  |

|             | SREG1: bits 7-0 (LSB)                                         |  |  |  |  |  |

|             | SREG2: bits 15-8                                              |  |  |  |  |  |

|             | SREG3: bits 23-16                                             |  |  |  |  |  |

|             | SREG4: bits 31-24 (MSB)                                       |  |  |  |  |  |

| Number of   | Total number of payload data bytes                            |  |  |  |  |  |

| received    | received from an external digital device                      |  |  |  |  |  |

| bytes (USB  | and forwarded to LAN / USB (excludes                          |  |  |  |  |  |

| or LAN)     | monitoring & control messages, includes                       |  |  |  |  |  |

|             | all data virtual streams). 32-bit byte                        |  |  |  |  |  |

|             | count. Counter rolls over when reaching                       |  |  |  |  |  |

|             | 0xFFFFFFFFF                                                   |  |  |  |  |  |

|             | SREG5: bits 7-0 (LSB)                                         |  |  |  |  |  |

|             | SREG6: bits 15-8                                              |  |  |  |  |  |

|             | SREG7: bits 23-16                                             |  |  |  |  |  |

|             | SREG8: bits 31-24 (MSB)                                       |  |  |  |  |  |

| MAC address | Unique 48-bit hardware address (802.3).                       |  |  |  |  |  |

|             | In the form                                                   |  |  |  |  |  |

|             | SREG9:SREG10:SREG11::SREG14                                   |  |  |  |  |  |

| L           | SKEU9.SKEU10.SKEU11SKEU14                                     |  |  |  |  |  |

As the monitoring data is constantly changing, it is important to be able to prevent changes while reading a multi-byte parameter. The monitoring data is latched upon reading register 0. Therefore, register 0should always be read first.

# Test Points

Test points are provided for easy access by an oscilloscope probe. The main focus of these test points is to help monitor proper flow control operation.

| Test  | Definition                                                            |  |  |  |

|-------|-----------------------------------------------------------------------|--|--|--|

| Point |                                                                       |  |  |  |

| TP 1  | TCP-IP connection on port 1024 (stream 1)                             |  |  |  |

|       | 1 = connected, $0$ otherwise                                          |  |  |  |

| TP 2  | TCP-IP connection on port 1026 (stream 2)                             |  |  |  |

|       | 1 = connected, $0$ otherwise                                          |  |  |  |

| TP 3  | TCP-IP connection on port 1028 (Monitoring &                          |  |  |  |

|       | Control)                                                              |  |  |  |

|       | 1 = connected, $0$ otherwise                                          |  |  |  |

| TP 4  | Stream 1 HDLC transmit elastic buffer empty                           |  |  |  |

|       | 1 = empty, $0$ otherwise                                              |  |  |  |

| TP 5  | Stream 2 HDLC transmit elastic buffer empty                           |  |  |  |

|       | 1 = empty, 0 otherwise                                                |  |  |  |

| TP 6  | Stream 1 HDLC receive elastic buffer <sup>3</sup> / <sub>4</sub> full |  |  |  |

|       | $1 = \frac{3}{4}$ full, 0 otherwise                                   |  |  |  |

| TP 7  | Stream 2 HDLC receive elastic buffer <sup>3</sup> / <sub>4</sub> full |  |  |  |

|       | $1 = \frac{3}{4}$ full, 0 otherwise                                   |  |  |  |

| TP 8  | HDLC flag 7E detected at input                                        |  |  |  |

| TP 9  | CRC error detected on channel 1 HDLC frame.                           |  |  |  |

|       | 1 = error detected at end of frame, 0 = no error                      |  |  |  |

| TP 10 | CRC error detected on channel 2 HDLC frame.                           |  |  |  |

|       | 1 = error detected at end of frame, 0 = no error                      |  |  |  |

| INIT# | Internal processing clock divided by 8.                               |  |  |  |

|       | 5 MHz square wave.                                                    |  |  |  |

| DONE  | 1 when the FPGA is loaded with a valid .mcs                           |  |  |  |

|       | configuration file (typically 0.4 seconds after power                 |  |  |  |

|       | up).                                                                  |  |  |  |

# Operation

#### Concept

The COM-5003 converts a TCP-IP socket stream or a USB stream into a simple clock-synchronous data stream and vice versa.

#### Using TCP-IP:

On the transmit side, the COM-5003 decodes the TCP-IP protocol and extracts the data from the network client. TCP, IP and Network information, and in particular routing information, are <u>not</u> transmitted from one end to the other.

At the receiving end, the network client must first connect to the COM-5003 to receive data.

The COM-5003 maintains the flow-control information between the TCP-IP socket and the input/output interfaces. For example, if the COM-5003 is connected to a COM-1001 QPSK modulator configured for 1 Mbit/s data throughput, the network client (i.e. data source) will be asked for 1 Mbit/s throughput over the TCP-IP link.

#### Using USB:

USB and TCP-IP can be used interchangeably and independently at the transmit-end or receive-end. For example, the user can select TCP-IP on the transmit side while using USB on the receiving end.

The main functional difference is that the COM-5003 USB interface supports only one bi-directional stream whereas the TCP-IP interface supports two streams.

#### Connectivity

As a gateway, the COM-5003 interconnects TCP-IP, USB and clock synchronous LVTTL interfaces. Some connections are configured by control registers (see <u>configuration registers</u>), while others are configured by selecting an FPGA option, as described below.

To select the **-A** or **-B** option, please follow the three steps:

Step 1: from the ComBlock Control Center graphical user interface, enumerate the ComBlocks, highlight the COM-5003 and open the personalities windows by clicking on the swiss army knife button.

Step 2: pull-down the personalities index and select index 2 for option **–A** or 3 for option **–B**.

Step 3: push the "Set Default" button.

|      | ComBlock Control Cent         |              |         |          |            |           |  |

|------|-------------------------------|--------------|---------|----------|------------|-----------|--|

| File | e Operatio                    | ons Function | р Н     |          |            |           |  |

| ×    | s 💊 🖻                         | 1 🐝 🖸        |         |          |            |           |  |

| _    |                               |              |         |          |            | _         |  |

| C    | OM50                          | 03 TCP-      | -IP / U | JSB G    | ATEWA      | Y         |  |

|      |                               |              |         |          |            |           |  |

| L.   | COM500                        | 3 TCP-IP /   | USB GAT | EWAY     |            |           |  |

|      | Personalit                    | ties         |         |          |            |           |  |

|      | Index                         | Personality  | Option  | Default  | Authorized | Boot Prot |  |

|      | 1                             | 1400         | в       |          | Yes        | No        |  |

|      | 2                             | 5003         | A       |          | Yes        | No        |  |

|      | 3                             | 5003         | в       | D        | Yes        | No        |  |

|      | 4                             | 0000         | в       |          | Yes 🌔      | No        |  |

|      | 5                             | 0000         | в       |          | Yes 5      | No        |  |

|      | 6                             | 0000         | в       |          | Yes 💛      | No        |  |

|      | 7                             | 0000         | В       |          | Yes        | No        |  |

|      | Add/Remove/Modify Personality |              |         |          |            |           |  |

|      | Index                         | Personality  | Option  | Password | ı 🤸        |           |  |

|      | 2 5003 B Set Default          |              |         |          |            |           |  |

|      | Close                         |              |         |          |            |           |  |

| •    |                               |              |         |          |            |           |  |

It takes 0.4 seconds to switch between options under user control.

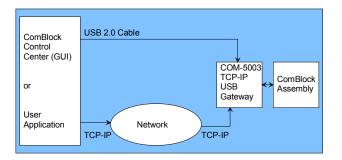

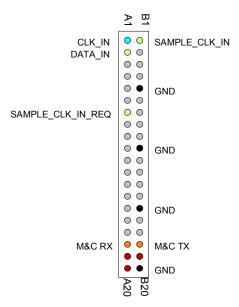

#### Option –A

Monitoring and Control is performed through either TCP-IP (IP port 1028) or USB, at the user's discretion.

A single high-speed bi-directional data channel is supported through USB.

The user can select several formats (8-bit parallel mode, 1-bit serial with HDLC, 1-bit serial without HDLC) at the input and output connectors through control registers.

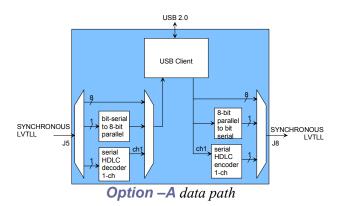

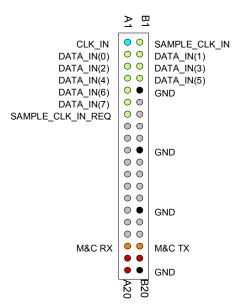

#### **Option** –B

All communications are established exclusively through the TCP-IP server. The USB Client is disabled.

The TCP-IP server supports three simultaneous connections: 2 high-speed bi-directional data channels and one bi-directional monitoring and control channel.

The user can select several formats (8-bit parallel mode, 1-bit serial with HDLC, 1-bit serial without HDLC) at the input and output connectors through control registers.

### **Format Conversion**

Parallel to serial conversion occurs at the output when a 8-bit byte received over the TCP-IP or USB link is converted to one-bit serial when so configured by the user. The key rule for parallel to serial conversion is that the most significant bit (MSb) is transmitted first.

Likewise, in the serial-to-parallel conversion which may be implemented at the input, the first received bit is placed at the MSb position in the byte.

#### Serial HDLC

A bit-serial HDLC format can be used to convey data over a synchronous serial link such as a wireless or satellite link. The HDLC objective is three-fold:

- (a) Tell the receiver side when no information is available for transmission.

- (b) Implement multiple virtual channels over a common physical link.

- (c) Recover the original bit-to-byte alignment of the original USB or TCP-IP connection at the receiving end.

HDLC can be enabled or disabled under user control. See control registers <u>REG21</u> and REG22.

## Serial HDLC format

This section provides details as to the serial HDLC format used on the synchronous serial link. It is intended for developers and can be skipped by most users.

| 78                               | E | Address<br>Field | Information Field | FCS              | 7E                        |  |

|----------------------------------|---|------------------|-------------------|------------------|---------------------------|--|

| 1 byte 1 byte<br>opening<br>flag |   |                  | variable-length   | 2 bytes<br>CRC16 | 1 byte<br>closing<br>flag |  |

Data is encapsulated within variable length frames starting and ending with a 0x7E flag. A two-byte CRC check can be used to verify if the frame is error free.

The information field always contain an integer number of bytes. The most significant bit is transmitted first. The maximal frame length (before accounting for bit stuffing) is 1024 bytes of information plus 5 bytes of overhead.

The following bit-stuffing mechanism is used on the transmit side for all fields except the opening and closing flags: a '0' is inserted after five consecutive 1's.

The address field is used to indicate the type of data conveyed within:

01: data from IP port 1024 02: data from IP port 1026

#### Loop Back

A loop back mode is provided for system-level test purposes. Transmitted data are looped back into the 1-bit serial input. The nominal input pins are disabled. However, the nominal output pins are enabled. Be sure to configure the output format as '1 bit serial with HDLC'.

The loopback test mode can be used in conjunction with USB (1 channel) and TCP-IP (2 channels).

#### **Trigger Pulse**

Users can remotely generate a short (25ns) pulse to trigger external devices such as the COM-8001 arbitrary waveform generator. The EXT\_TRIGGER\_OUT pulse is generated on pin J8/B6 upon sending control register <u>REG22</u> with bit 1 set to '1'.

#### Recovery

The COM-5003 is protected against corruption by an invalid FPGA configuration file or an invalid user configuration. To recover from such occurrence, connect the BOOT pin to the nearby ground pin using a jumper and power-up the COM- 5003. Remove the jumper after 1 second. The COM-5003 will be automatically configured with a boot configuration which restores both USB and LAN/TCP-IP communications. This boot file is unerasable. Once this is done, the user can safely restore the user configuration and/or re-load a valid FPGA configuration file into flash memory using the ComBlock Control Center.

## **TCP-IP Interface**

#### **IP Ports**

While configured in option –B, the COM-5003 acts as a TCP-IP server. As such it opens the following sockets in listening mode:

- Port 1024: transmit and receive data stream 1.

- Port 1026: transmit and receive data stream 2.

- Port 1028: monitoring and control port.

In addition, the COM-5003 opens port 1029 as a UDP port for remote reset.

While configured in option –A, the COM-5003 acts as a TCP-IP server for remote monitoring and control only (port 1028).

## **TCP-IP Throughput Benchmarks**

The COM-5003 is capable of a sustained (average) throughput of 53 Mbits/s over 100base-Tx. In most cases, the sustained throughput is limited by the TCP-IP client computer, the application(s) running on the client computer and the network configuration, as illustrated in the one-way data transfer benchmarks below:

| Throughput tests conditions                                                                                                                                                                                             | Throughput<br>(100MB<br>average) |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Client: Intel Pentium 4 2.8 GHz running<br>winsock-based console application. Direct<br>cross-over LAN cable. No other application<br>running.<br>COM-5003 configured as 'Auto<br>Negotiation''. 100Base-Tx connection. | 53 Mbits/s                       |

| Client: AMD Sempron 3000<br>Direct cross-over LAN cable.                                                                                                                                                                | 47 Mbits/s                       |

| Client: Intel Pentium 4 2.8 GHz over LAN<br>(through two LAN switches)                                                                                                                                                  | 32 Mbits/s                       |

# IP Protocols

This module supports the following IP protocols:

- Ping

- ARP

- TCP-IP

## Power Up

The LAN link is available typically 2.1 seconds after power up.

### Ping

The module responds to ping requests with size up to 470 bytes. Ping can be used to check the module response over the LAN network. Ping can be used at any time, concurrently with other transmit and receive transactions. For example, on a Windows operating system, open the Command prompt window and type "ping -t -1 470 172.16.1.128" to send pings forever of length 470 bytes to address 172.16.1.128.

# UDP-IP

Port 1029 is open as a UDP receive-only port. This port serves a single purpose: being able to reset all TCP-IP connections gracefully. This feature is intended to remedy a common practical problem: it is a common occurrence for one side of a TCP-IP connection to end abnormally without the other side knowing that the connection is broken (for example when a server 'crashes'). In this case, new connections cannot be established without first closing the previous ones. The problem is particularly acute when the COM-5003 is at a remote location. The command "@001RST<CR><LF>" sent as a UDP packet to this port will reset all TCP-IP connections within the COM-5003.

TCP-IP connections can also be cleared remotely from the ComBlock Control Center as illustrated below:

|   | Communication Setup<br>Detect ComBlocks                   | Help<br>Ctrl+S<br>Ctrl+D<br>Ctrl+E |

|---|-----------------------------------------------------------|------------------------------------|

|   | Personalities                                             | Ctrl+M                             |

|   | Status Registers                                          | Ctrl+R                             |

|   | TCPReset TCP/IP Cor                                       | nnection.                          |

| R | TCP <mark>Reset TCP/IP Cor</mark><br>Reset TCP/IP Connect |                                    |

|   | Reset TCP/IP Connect                                      |                                    |

|   | Reset TCP/IP Connect                                      | ion                                |

# Client Programming : TCP-IP

This section is intended to help designers who want to design their own client application. It can be skipped by users of ready-to-use applications such as Hyperterminal, ComBlock Control Center, etc.

In network terminology, the COM-5003 is a server. It awaits connection establishment and connection termination under the initiation of clients. It never initiate any connection establishment or termination.

An example of C-language Winsock programming for Windows OS clients is shown below. More information about Winsock programming can be found at

http://msdn.microsoft.com/library/default.asp?url=/l

us/winsock/winsock/finished\_server\_and\_client\_co de.asp

Be sure to include a reference to the Winsock2 library (WS2\_32.lib) in the project release and/or debug settings.

```

#include <stdio.h>

#include "winsock2.h"

void main() {

// Initialize Winsock.

WSADATA wsaData;

int iResult = WSAStartup( MAKEWORD(2,2), &wsaData );

if ( iResult != NO ERROR )

printf("Error at WSAStartup()\n");

// Create a socket.

SOCKET m socket;

m socket = socket( AF INET, SOCK STREAM, IPPROTO TCP );

if ( m socket == INVALID SOCKET ) {

printf( "Error at socket(): %ld\n", WSAGetLastError() );

WSACleanup();

return;

}

// Connect to a server.

sockaddr in clientService;

clientService.sin family = AF INET;

// insert destination address below

clientService.sin addr.s addr = inet addr( "172.16.1.128" );

// insert destination port below

clientService.sin port = htons(1024);

if ( connect( m socket, (SOCKADDR*) & clientService, sizeof(clientService) ) ==

SOCKET ERROR) {

printf( "Failed to connect.\n" );

WSACleanup();

return;

}

// Send and receive data.

int bytesSent;

int bytesRecv = SOCKET ERROR;

char sendbuf[32] = "Client: Sending data.";

char recvbuf[32] = "";

bytesSent = send( m_socket, sendbuf, strlen(sendbuf), 0 );

printf( "Bytes Sent: %ld\n", bytesSent );

while( bytesRecv == SOCKET ERROR ) {

bytesRecv = recv( m socket, recvbuf, 32, 0 );

if ( bytesRecv == 0 || bytesRecv == WSAECONNRESET ) {

printf( "Connection Closed.\n");

break;

if (bytesRecv < 0)

return;

printf( "Bytes Recv: %ld\n", bytesRecv );

}

return;

```

# USB Interface

## **USB** Throughput Benchmarks

The COM-5003 is capable of a sustained (average) throughput of 85 Mbits/s over USB 2.0. In most cases, the sustained throughput is limited by the host computer and the application(s) running on the host computer.

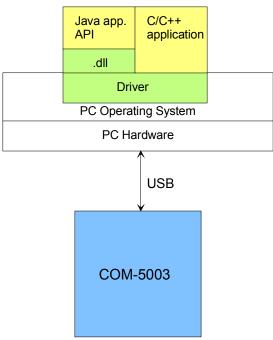

# **Client Programming : USB 2.0**

Software to help developers create USB high-speed communications between the COM-5003 and a host PC is provided. The **USB 2.0 software package** includes the following:

- Windows device driver for XP/2000/Me (.sys, .inf files)

- Java API, .dll and application sample code

- C/C++ application sample code

The USB 2.0 software package is available in the ComBlock CD and can also be downloaded from <u>ComBlock.com/download/usb20.zip</u>. The user manual is available at <u>ComBlock.com/download/USB20\_UserManual.pdf</u>

Blue: supplied hardware Green: supplied ready-to-use software Yellow: source code examples

# Troubleshooting

## LAN problems

Quick checklist:

- is the LAN connection through a Hub or directly to the host PC? In the former case, use a straight LAN cable, in the latter case use a cross-over cable.

- 2) Make sure the +5V power is applied to both submodules, not just the larger one.

- The LAN adapter (the one with the RJ-45 connector) should be plugged in the larger module through the J9 bottom connector, never through J5 or J8.

- The 'DONE' test point should be high (2.5V), otherwise the FPGA is not properly configured. If not, please contact us for assistance.

- 5) Link LED should be ON when the LAN cable is plugged in. Likewise, a LED at the Hub or PC should be ON. If not, the cable could be bad or see points 1 4 above.

- 6) Did you assign a static IP address to the COM-5003? Please see the "Initial configuration" section on page 4.

- 7) Do not assign the same IP address for the COM-5003 and the host computer.

- 8) Is the COM-5003 IP address consistent with the PC address? In general the first 3 numbers of the IP address must match

- If ping does not work, see points 5 − 8 above.

# Timing

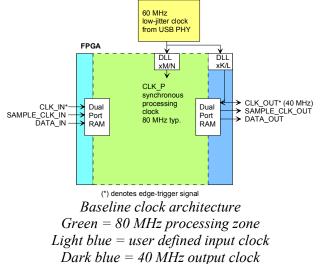

## Clocks

The clock distribution scheme embodied in the COM-5003 is illustrated below.

#### Input:

The input signals at the J5 connector are synchronous with the CLK\_IN clock at J5/A1. This clock can be up to 40 MHz.

A 16Kbit dual-port RAM elastic buffer is used at the boundary between inputs and internal processing area. Thus, the input clock frequency can be independent from the internal processing clock frequency.

#### Output:

The 40 MHz output clock CLK\_OUT is locked to the internal USB PHY 60 MHz clock by means of a DLL. CLK\_OUT is <u>not</u> related in frequency to the external CLK\_IN clock.

The output signals are synchronous with the rising edge of the 40 MHz reference clock CLK\_OUT (i.e. all signals are stable at the rising edge of the reference clock CLK\_OUT).

#### Internal processing:

The core signal processing performed within the FPGA is synchronous with the 80 MHz processing clock CLK\_P. The processing clock is derived from the USB PHY 60 MHz oscillator. CLK\_P is not related to the external CLK IN clock.

#### Input

# LEDs

2 LEDs located close to the LAN RJ-45 jack provide summary information as to the LAN: Link and activity.

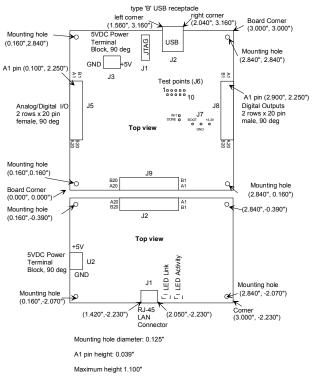

# Mechanical Interface

# Schematics

The board schematics are available on-line at <u>ComBlock.com/download/com\_1400schematics.zip</u> for the main board and <u>ComBlock.com/download/com\_5002schematics.zip</u> for the LAN adapter.

# Pinout

#### **USB Connector J2**

USB type B receptacle.

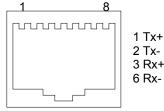

## LAN Connector J1

The RJ-45 Jack is wired as a standard PC network interface card. Connection to a LAN Hub is over a straight-through cable.

RJ-45 Jack

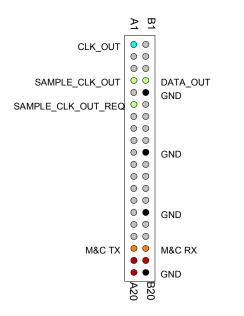

## **Connector J5**

There are several possible connector configurations, depending on the application:

(a) 1-bit wide input from another ComBlock [COM-1009, COM-7001, COM-1202, COM-1418, COM-1027, etc]

(b) 8-bit wide input from another ComBlock [COM-8002,etc]

#### **Connector J8**

There are several possible connector configurations, depending on the application:

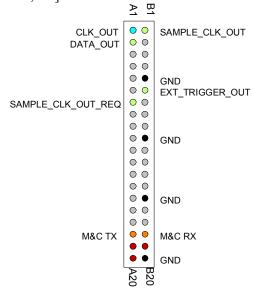

(a) 1-bit wide output to another ComBlock [COM-1010, COM-1402, COM-1019, COM-1028, etc]

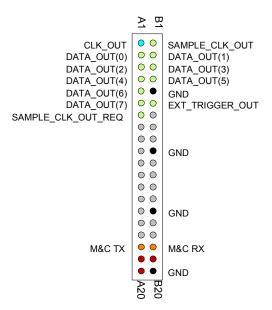

(b) 8-bit wide output to another ComBlock [COM-8001, etc]

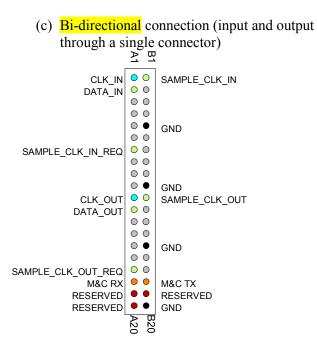

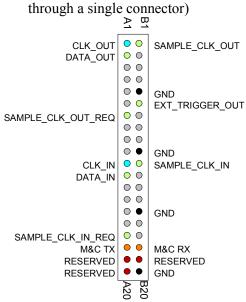

(c) Bi-directional connection (input and output

(d) Special case: 1-bit serial output to a COM-7001 turbo code encoder.

#### I/O Compatibility List

(not an exhaustive list)

| Input Output                                                                     |                        |  |  |  |

|----------------------------------------------------------------------------------|------------------------|--|--|--|

|                                                                                  |                        |  |  |  |

| <u>COM-1202</u>                                                                  | <u>COM-1402</u>        |  |  |  |

| PSK/QAM/APSK modem                                                               | PSK/QAM/APSK           |  |  |  |

|                                                                                  | modulator              |  |  |  |

| <u>COM-1418</u> DSSS                                                             | <u>COM-1019</u> DSSS   |  |  |  |

| Demodulator                                                                      | Modulator              |  |  |  |

| COM-1027 FSK/MSK                                                                 | <u>COM-1028</u>        |  |  |  |

| demodulator                                                                      | FSK/MSK/GFSK/GMSK      |  |  |  |

|                                                                                  | modulator              |  |  |  |

| COM-1009A Viterbi                                                                | COM-1010 Convolutional |  |  |  |

| decoder K=7                                                                      | encoder                |  |  |  |

| COM-8002 Data                                                                    | COM-8001 Arbitrary     |  |  |  |

| acquisition module                                                               | Waveform Generator     |  |  |  |

| COM-7002 Turbo code encoder/decoder                                              |                        |  |  |  |

| COM-1200/1300/1400 FPGA development platforms                                    |                        |  |  |  |

| $\underline{\text{COM-1600/1500}}$ FPGA + ARM development platforms <sup>2</sup> |                        |  |  |  |

#### **Configuration Management**

This specification is to be used in conjunction with VHDL software revision 8.

# **ComBlock Ordering Information**

COM-5003 TCP-IP / USB Gateway

MSS • 18221-A Flower Hill Way • Gaithersburg, Maryland 20879 • U.S.A. Telephone: (240) 631-1111 Facsimile: (240) 631-1676 E-mail: sales@comblock.com

<sup>&</sup>lt;sup>2</sup> 98-pin to 40-pin adapters to interface with other Comblocks are supplied free of charge. Please let us know about your interface requirements at the time of order.